一種基于串口協議的程序燒寫方法與改進措施

李菁,趙龍飛,凌霄

(北京航天發射技術研究所北京100076)

在英飛凌16位/32位控制器的開發過程中,比較通用的方法是利用仿真器通過14針腳的JTAG端口對控制程序進行在線調試與加載,該方法在硬件測試及軟件調試階段非常方便,但著眼于現有車載控制器機械外形,外接的有限接插件端子數便成為制約控制器性能的一個重要因素,如預留多個端子專供JTAG口程序加載,會造成控制器資源的巨大浪費,此時利用端口復用技術便成為解決此類問題的關鍵。

文中以16位的XC164單片機為例,設計并改進了一種利用UART串口協議對其進行程序加載的方法,該方法也稱為BSL工作模式下的程序加載,它通過特定的引腳與PC主機進行通信,采用標準的UART協議完成數據傳輸,從而完成控制器的程序下載功能。該方法硬件接口簡單,并可復用為RS232/RS422接口,功能可靠,已在實際調試中取得良好效果。

1 XC164單片機的BSL模式簡介

BSL(Bootstrap loader)是英飛凌單片機的內嵌引導程序加載器提供的一種加載啟動程序的機制,用于標準的系統啟動。XC164系列單片機可支持3種協議/模式的BSL啟動機制:標準UART協議,同步串行協議和CAN總線協議。不論哪種協議/模式,XC164系列單片機加載程序的處理方式是相同的。其中UART協議是實現設備之間低速數據通信的標準協議,是一種異步串行通信協議。

1.1 基于UART協議的BSL引導程序

引導程序加載器是通過預先定義好的一組接口引腳與外部主機通信的,BSL啟動模式下,這些接口引腳被自動使能,并由引導程序加載器控制。XC164根據外部引腳設置,上電復位后進入BSL模式,同時禁止看門狗定時器和調試系統,在與PC機建立通信之后,BSL進入到下一個循環中,接收相應個數的字節,這些字節從地址E0'0000H開始順序保存到片上PSRAM中。加載的代碼可能是最后的應用代碼或是其他更為復雜的程序,該加載程序添加了傳送協議,從而增強了加載代碼或數據的一致性,還可能包含改變系統配置并使能總線接口,從而將接收到的數據保存在外部存儲器中的代碼序列。為了執行加載的代碼,之后BSL使寄存器VECSEG指向地址E0'0000H,即要加載的第一條指令處,然后跳轉到該指令。

1.2 BSL模式下XC164與PC機的UART通信時序

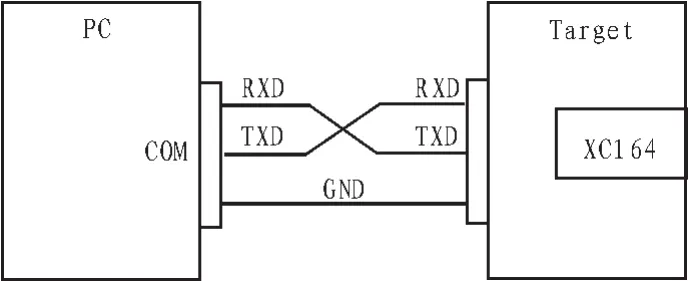

XC164與PC機的硬件連接原理性框圖如圖1所示,通過PC的串行端口,經RS232/RS422總線將加載程序發送給XC164單片機,通過引導程序加載到芯片的FLASH中,完成控制器的程序下載功能。

圖1 XC164與PC機的硬件連接圖

標準UART引導程序加載通過USIC0通道0(UOCO)將程序代碼/數據傳送到PSRAM中。發送ID字節之后才能使能U0C0接收與主機進行半雙工連接。在標準UART引導模式中,通信“握手”數據使用了不帶奇偶校驗的異步8位數據幀(1個起始位,1個停止位),其通信時序如圖2所示。

圖2 標準UART引導程序加載時序

XC164進入UART BSL模式并完成相應的初始化之后,XC164掃描RXD線,接收一個零字節。零字節被認為是包含1個起始位,8個0數據位以及1個停止位。在該零字節傳送期間,XC164以當前CPU時鐘為單位,計算相應的波特率因子,相應的初始化串行接口U0C0并將引腳TXD切換到輸出,使用該波特率,向提供加載數據的主機返回一個ID字節。一旦發送ID字節,BSL進入下一個循環,通過U0C0接收用戶數據。

1.3 BSL通信波特率設置

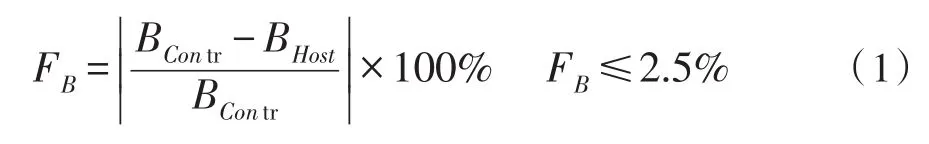

XC164系列單片機允許用戶在很寬的波特率范圍內進行引導程序加載操作,但為了確保正確的數據傳送操作,用戶波特率的設置必須滿足上限和下限的要求。XC164使用位域PDIV測量第一個零字節的長度。量化誤差使得測量值可能與實際波特率有一定偏差。為了正確從主機向XC164傳送數據,U0C0內部初始化波特率和主機的實際波特率之間的最大偏差應該低于2.5%。可根據式(1)計算XC164的波特率與主機波特率之間的偏差(FB,百分數)

注:函數(FB)不考慮振蕩器和其他支持串口通信的器件的容差。

該波特率偏差是一個非線性函數,和系統時鐘以及主機波特率有關。由于較小的波特率預分頻因子容易導致較大的量化誤差,因此函數(FB)的最大值隨主機波特率增加而增大,如圖3所示。

圖3 主機與XC16X之間的波特率偏差

測量零字節時,最小波特率BLow由位域PDIV最大計數能力決定,取決于系統時鐘,低于BLow的值會導致PDIV溢出,U0C0不能被正確初始化,可能導致與PC機通信失敗。最大波特率BHigh是指未超過偏差極限的最高波特率。主機與XC164單片機建立通信時,通信波特率的設置最好在BLow和BHigh之間選取。

標準UART加載模式下,最小波特率BLow為2.4 K,BHigh為19.2 K。

2 基于串口協議的程序燒寫方法的硬件實現

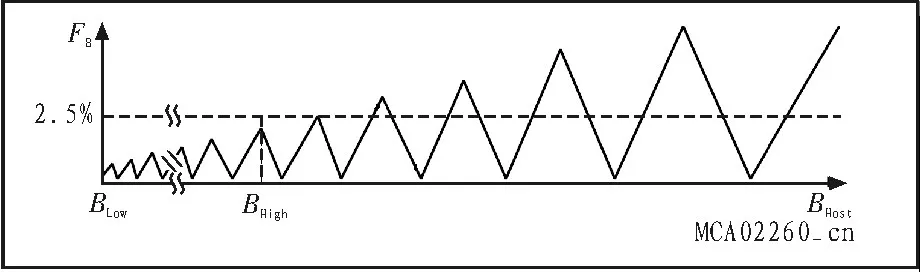

單片機選用型號SAK-XC164CS-32F40F,總線協議收發器選用MAX1490EBEPG,單片機配置引腳如圖4所示,信號EX_DL連同RS422的4條總線信號一起被引出控制器接插件,作為控制器的BSL模式配置端口和RS422通信端口,當EX_DL通過開關切換至低電平時,單片機復位后進入BSL加載模式;切換至高電平時,串口僅作有RS422通信功能。

圖4 單片機XC164 BSL加載模式配置引腳

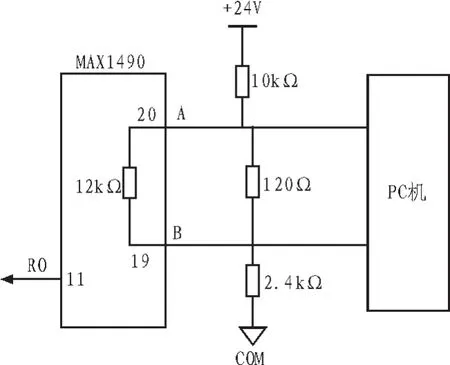

UART BSL程序加載是通過特定的端口進行的,串口與XC164的硬件連接如下圖5所示,MAX1490是RS422收發器,實現PC機與422總線間的電平轉換,XC164的P3.10和P3.11既可以用于串口加載程序和RS232/RS422通信,也可以復用普通IO端口。

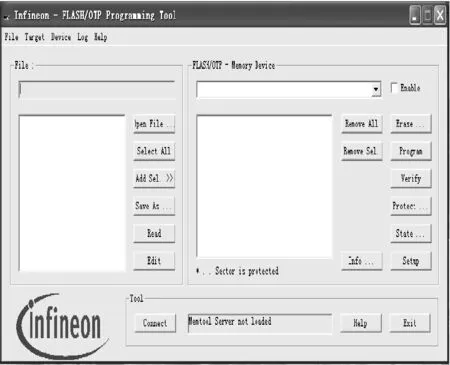

串口協議的引導程序加載功能可以通過Memtool實現。Memtool是英飛凌提供的免費下載軟件,可以對目前英飛凌單片機所有產品進行編程,包括片內存儲器編程和外部Flash編程。Memtool 4.2軟件的主界面如圖6所示,選擇菜單欄“Target”菜單下的“Change”欄,在XC16X系列中配置具體的目標芯片,串口使用的波特率115200和COM端口。

圖5 串口總線與單片機的硬件連接

圖6 Memtool 4.2軟件主界面

Memtool軟件配置完成后,控制器重新上電復位,點擊“connect”,XC164芯片則進入引導程序硬件初始化和與PC主機建立通信的階段,通信建立的實測時序如圖7所示。從圖6中可看出,PC主機向控制器發送10位的0字節,每位占據時間約10 μs,由此計算出波特率為115 200,與設置值相符合,之后控制器向PC主機發送D5H的ID字節,每位時間也為10 μs,波特率相同。通訊建立完成后,用戶程序的加載可以通過“Program”實現。

圖7 XC164與PC機建立通信實測時序

3 影響串口程序加載的因素及改進

RS422標準規定了收發器門限為±200 mV,這樣規定能夠提供比較高的噪聲抑制能力。當接收器正端(A)電平比負端(B)高+200 mV以上時,輸出為正邏輯,反之,輸出為負邏輯。但由于第三態的存在,即總線空閑時沒有任何信號驅動總線,使AB之間的電壓在-200 mV~+200 mV直至趨于0 V,這帶來了一個問題:接收器輸出狀態不確定。MAX1490收發器本身解決了這個問題,當總線空閑時,MAX1490通過自身的內部電路,將總線驅動為高電平狀態。

RS422通信為避免長線信號傳輸時信號的反射和回波,一般在信號接收端接入終端匹配電阻,典型值為120 Ω。但這樣做有可能引入一種后果,當總線上有超過-200 mV的雜波電平干擾時,接收器輸出為低電平,如果雜波的干擾電平一直未達到+200 mV以上,則接收器的輸出就一直為低電平,XC164芯片則進入引導程序硬件初始化后接收不到0字節(因為總線一直被驅動為低),與PC主機不能成功建立通信,從而導致程序燒寫失敗。

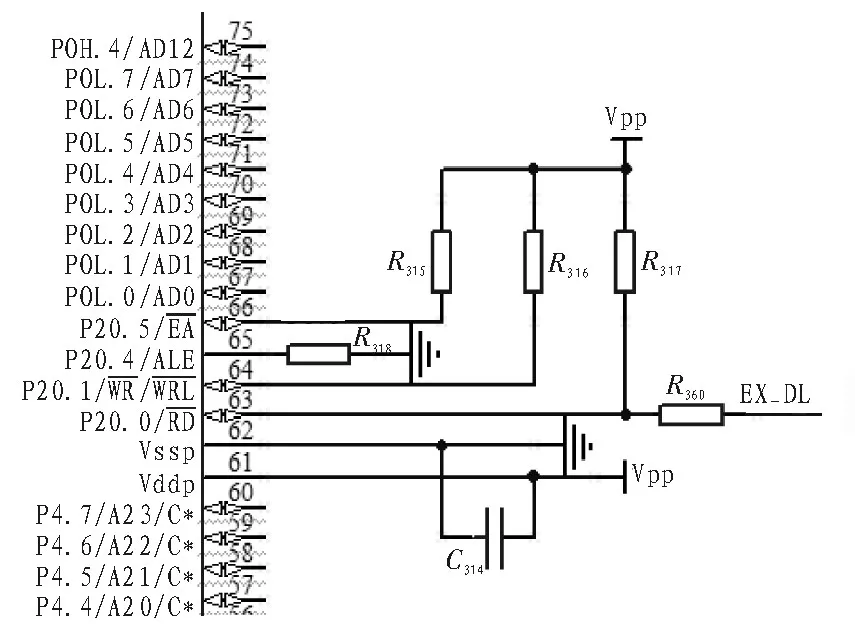

雜波電平干擾問題可以通過設置適宜的偏置電阻解決,偏置電阻可以加在下載工裝電纜中,控制器接插件引出電源是24 V,所以偏置電阻阻值的計算是根據24 V電源來計算的,偏置電阻添加的目的是在總線空閑狀態下,匹配電阻120 Ω上的分壓達到+200mV以上。改進后的硬件電路圖如圖8所示。

圖8 工裝電纜的改進

4 結論

基于串口協議的程序燒寫方法充分利用了英飛凌flash系列芯片所提供的BSL功能,硬件實現結構簡單,可以與RS422通信接口復用,不占用控制器有限的接插件資源,程序下載無需額外的下載器,減少了控制器的生產成本,簡化了控制器生產流程。改進后的串口協議程序燒寫方法成功解決了串口燒寫失敗的問題,該方法已經廣泛應用于控制器的批產工作中。

[1]張立強,宋玲,劉寶娟.JTAG并口下載設計[J].微處理機,2013(1):280-285.

[2]鄔子嬰,步鑫,任齊鳳.邊界掃描JTAG控制器設計與實現[J].航空電子技術,2016,1(7):31-34

[3]姚海濱,高磊,黃貴晨.RS232串口直連線與交叉線可變裝置[J].黑龍江科技信息,2016(5):106.

[4]孫慧強.基于單片機的數據串口通信研究[J].數字技術與應用,2016(3):24.

[5]HuiZhao,Tiejun Xiao,Xiaoru Han.The Application of Boundary-Scan Technology to FPGA-Based ExperimentSystem:The Ninth International Conference on Electronic Measurement&Instruments[C]//Beijing,China,2009:2629-2632.

[6]Wen-Cheng Hsieh.U-BootPorting And Implementation On Embedded System[M].National Taiwan University of Science and Tecnology,NTUST Library,2005:8-15.

[7]崔旭晶,李天雷.基于SOPC的UART IP核設計與驅動開發及系統移植[J].電子設計工程,2014(6):121-125.

[8]鄧偉.徐揚婧.基于SOPC技術的異步串行通信IP核的設計與實現[J].電子設計工程,2012,20(3):185-188.

[9]夏柯.門蘭寧.基于ZYNQ-7000 DMA控制器的UART數據傳輸的設計與實現[J].信息化建設,2014(9):113-114.

[10]黃毓芯.基于FPGA的UART電路設計與實現[J].機電技術,2014(4):33-35.

[11]劉浩淼,卞樹檀.基于CPLD的RS 422串口通信實現[J].電子設計工程,2011(12):153-155.

[12]李洋洋,吳武臣.基于斷言的驗證方法在UART模塊中的應用研究[J].微電子學與計算機,2012(1):151-153.

[13]孟敬,王冬青,姜璐璐,等.基于單片機的CAN/UART協議轉換器的設計[J].青島大學學報,2012(12):38-42.

[14]桂桂,李吉.王珍.基于UART的AVR和FPGA 的通信設計及實現[J].儀表技術,2013(11):44-46.

[15]薛志遠,朱浩,張鐵軍.一種基于串口通信的DSP調試平臺設計[J].微電子學與計算機,2013(12):151-154.