體系結(jié)構(gòu)內(nèi)可編程數(shù)據(jù)平面方法

馬久躍 余子濠 包云崗 孫凝暉

1(中國科學院計算技術(shù)研究所 北京 100190)2 (中國科學院大學 北京 100049)(baoyg@ict.ac.cn)

體系結(jié)構(gòu)內(nèi)可編程數(shù)據(jù)平面方法

馬久躍1,2余子濠1,2包云崗1孫凝暉1

1(中國科學院計算技術(shù)研究所 北京 100190)2(中國科學院大學 北京 100049)(baoyg@ict.ac.cn)

隨著互聯(lián)網(wǎng)與云計算的發(fā)展,越來越多的應(yīng)用被從本地遷移到云端,這些應(yīng)用最終被運行在共享的數(shù)據(jù)中心.受到數(shù)據(jù)中心應(yīng)用復雜并且需求多變特征的影響,傳統(tǒng)體系結(jié)構(gòu)中的部分硬件部件(如共享末級緩存、內(nèi)存控制器、IO控制器等)固定功能的設(shè)計不能很好地滿足這些混合多應(yīng)用的場景需求.為滿足這類應(yīng)用場景的需求,計算機體系結(jié)構(gòu)需要提供一種可編程硬件機制,使得硬件功能能夠根據(jù)應(yīng)用需求的變化進行調(diào)整.提出了一種可編程數(shù)據(jù)平面方法:通過在現(xiàn)有硬件部件中增加可編程處理器,使用執(zhí)行固件代碼的方式對硬件的請求進行處理,并通過更新數(shù)據(jù)平面處理器固件的方式實現(xiàn)硬件功能的擴展.該方法在FPGA原型系統(tǒng)中進行驗證,其結(jié)果表明,該方法并沒有給系統(tǒng)性能帶來嚴重的影響,只使用有限的資源即可為硬件增加更為靈活的可編程能力,使其能夠適應(yīng)應(yīng)用需求復雜多變的場景.

可編程;處理器;數(shù)據(jù)中心;服務(wù)器;服務(wù)質(zhì)量

當前數(shù)據(jù)中心正面臨著資源利用率與服務(wù)質(zhì)量相沖突的挑戰(zhàn).使用虛擬化、容器等負載融合的方法將多個應(yīng)用運行在同一服務(wù)器中,可以有效地提高服務(wù)器的資源利用率;但是在這一過程中,無管理的軟硬件資源共享帶來了不可預(yù)測的性能波動.為了保障延遲敏感型應(yīng)用的服務(wù)質(zhì)量,在共享的數(shù)據(jù)中心環(huán)境下,管理員或開發(fā)者通常會為這些應(yīng)用獨占或過量分配資源,造成了非常低的數(shù)據(jù)中心資源利用率,只有6%[1]~12%[2].

針對這種由于共享軟硬資源競爭所帶來的干擾問題,一些現(xiàn)有工作在軟件層次,通過分析應(yīng)用的競爭點,使用調(diào)度[3-6]、隔離[7-8]等方案嘗試解決該問題.但由于數(shù)據(jù)中心中海量應(yīng)用的特點,對海量的應(yīng)用組合進行競爭點的判別與消除是不切實際的;同時由于數(shù)據(jù)中心應(yīng)用不斷變化的動態(tài)性特點,資源競爭點也是隨時在發(fā)生變化,因此這些軟件技術(shù)很難在通用數(shù)據(jù)中心發(fā)揮作用.另一些研究提出在硬件層次上實現(xiàn)資源隔離與劃分(如末級緩存容量劃分[9-13]、內(nèi)存通道劃分[14-15]等),但由于缺少統(tǒng)一的接口,這些工作通常只關(guān)注單一的資源,而沒有考慮到資源之間的相關(guān)聯(lián);同時由于當前體系結(jié)構(gòu)在共享硬件層次的應(yīng)用語義信息缺失,使得其在硬件層次無法區(qū)分不同的應(yīng)用需求,造成在硬件層次很難實現(xiàn)硬件資源的細粒度管理.

構(gòu)建高效的數(shù)據(jù)中心需要一種軟硬件協(xié)調(diào)的機制,而傳統(tǒng)計算機體系結(jié)構(gòu)所提供的指令集架構(gòu)(ISA)抽象不能滿足這一需求,正如白皮書《21st Century Computer Architecture》[16]中所指出的:我們需要一種高層接口將程序員或編譯器信息封裝并傳遞給下層硬件,以獲得更好的性能或?qū)崿F(xiàn)更多應(yīng)用相關(guān)的功能.之前的工作PARD[17]提出了一種資源管理可編程體系結(jié)構(gòu),通過在計算機內(nèi)部請求附加應(yīng)用標簽,在共享部件中實現(xiàn)應(yīng)用區(qū)分;并通過控制平面對來自不同應(yīng)用的請求進行不同的處理,實現(xiàn)在同一服務(wù)器上為不同應(yīng)用提供區(qū)分化服務(wù);同時提供集中式的資源管理平臺,實現(xiàn)對不同部件的資源使用進行統(tǒng)一管理.但它使用的基于表的控制平面設(shè)計并不能很好地適應(yīng)應(yīng)用需求的變化,這種設(shè)計只提供了對硬件已有功能的配置,需要在硬件部件上靜態(tài)實現(xiàn)這些功能并對外提供配置接口,且功能一旦實現(xiàn)無法根據(jù)應(yīng)用的需求進行調(diào)整.

然而在實際場景中,應(yīng)用會對底層的硬件不斷提出不同的需求,如更換Cache控制器的緩存替換策略、更改內(nèi)存控制器的地址映射方式與調(diào)度策略、為IO控制器增加數(shù)據(jù)加密或壓縮的功能等.當前的這種靜態(tài)的數(shù)據(jù)平面設(shè)計不能很好地滿足這類需求,需要更換硬件才能實現(xiàn),而這需要很長的周期,無法適應(yīng)數(shù)據(jù)中心這種需要不斷變化的場景.

在學術(shù)界中,已有一些研究通過在硬件上增加可編程機制,實現(xiàn)根據(jù)應(yīng)用需求對硬件策略進行調(diào)整的功能.如體系結(jié)構(gòu)領(lǐng)域已經(jīng)提出在內(nèi)存控制器[18-20]、Cache與一致性協(xié)議[21-24]上使用可編程邏輯來提供更靈活的功能,但這些只考慮了如何為單一應(yīng)用提供更多的可編程支持,不能很好地在數(shù)據(jù)中心這種多應(yīng)用場景下使用.在網(wǎng)絡(luò)領(lǐng)域中也有工作提出在SDN數(shù)據(jù)平面上增加可編程邏輯的方案,以提高SDN數(shù)據(jù)平面的可編程性[25-28],通過數(shù)據(jù)平面的重編程,達到對更多數(shù)據(jù)包的檢測與處理的目的.PARD的一個重要貢獻是將網(wǎng)絡(luò)概念引入計算機體系結(jié)構(gòu),本文希望將SDN數(shù)據(jù)平面中這種高級的可編程機制引入到計算機體系結(jié)構(gòu)中,實現(xiàn)更靈活的控制.

綜上,本文提出了一種體系結(jié)構(gòu)內(nèi)可編程數(shù)據(jù)平面架構(gòu),通過在硬件部件中增加處理器邏輯,使用執(zhí)行固件代碼的方式對硬件部件的請求進行處理,并通過更新數(shù)據(jù)平面處理器固件的方式實現(xiàn)數(shù)據(jù)平面功能的擴展,以增強計算機體系結(jié)構(gòu)的可編程靈活度,使其能夠適應(yīng)更加復雜多變的數(shù)據(jù)中心應(yīng)用場景.

1 研究背景與關(guān)鍵問題

1.1 PARD與區(qū)分化服務(wù)

PARD實現(xiàn)區(qū)分化服務(wù)(DiffServ)的關(guān)鍵機制是:1)使用標簽區(qū)分應(yīng)用;2)控制平面與數(shù)據(jù)平面分離,將請求處理與策略控制分離;3)集中式的策略管理與反饋機制.為實現(xiàn)以上3個關(guān)鍵機制,PARD體系結(jié)構(gòu)由4個部分組成,如圖1所示:

Fig. 1 PARD architecture overview[17]圖1 PARD總體架構(gòu)圖[17]

① 標簽機制.為了使硬件資源能夠區(qū)分來自不同應(yīng)用的請求,PARD為給每個應(yīng)用分配一個區(qū)分服務(wù)標識符(DS-id),同時在CPU核心和IO設(shè)備等所有請求源中增加一個DS-id標簽寄存器.這些寄存器用于給Cache訪問請求、訪存請求、DMA請求以及中斷請求附加上標簽.請求在發(fā)出源附加上DS-id標簽后,這個標簽將跟隨請求在整個體系結(jié)構(gòu)中傳播.

② 可編程控制平面.為每個共享硬件資源增加一個可編程控制平面,以利用請求中所包含的DS-id標簽實現(xiàn)區(qū)分化服務(wù).當硬件接收到請求后,控制平面首先會根據(jù)請求的DS-id對其進行處理,并產(chǎn)生發(fā)送到下一級硬件的請求,同時將DS-id附加到新的請求上.由于不同硬件的行為差別很大,它們對DS-id的使用方式也不同,例如Cache使用DS-id實現(xiàn)容量劃分,內(nèi)存和IO控制器使用其實現(xiàn)帶寬分配.PARD為不同的硬件部件提供了一個通用的控制平面結(jié)構(gòu),該控制平面結(jié)構(gòu)包括3個由DS-id索引的控制表:參數(shù)表(parameter table),用于保存資源分配策略;統(tǒng)計表(statistics table),用于記錄資源使用信息;用于存放性能觸發(fā)條件的觸發(fā)表(trigger table).除此之外,該控制平面還包括一個可編程接口和一個連接到集中式平臺資源管理模塊(PRM)的中斷線.

③ 平臺資源管理模塊(PRM).與傳統(tǒng)服務(wù)器中的IPMI[6]類似,PARD包含一個集中式平臺資源管理模塊來連接所有的控制平面和標簽寄存器(參見圖1中的虛線).PRM是一個包含處理器、內(nèi)存、Flash存儲、以太網(wǎng)適配器以及多個控制平面適配器(control plane adaptor, CPA)的嵌入式SoC系統(tǒng).其上運行基于Linux的固件,將控制平面抽象為設(shè)備文件樹,使用基于文件樹的統(tǒng)一編程接口來訪問控制平面,并為管理員提供了“Trigger→Action”編程方法來部署資源管理策略.

④ 可編程方法.為了方便管理員通過對控制平面進行編程來部署資源管理策略,PARD提供了一種“Trigger→Action”編程方法.如圖2所示,對于一個DS-id,可以定義多個“Trigger→Action”規(guī)則,每個規(guī)則針對特定的硬件資源(如基于Cache缺失率等性能指標),并且被存放在觸發(fā)表中;觸發(fā)動作可以使用任何語言來編寫,實現(xiàn)策略調(diào)整.這些規(guī)則被安裝在PRM固件中,在PRM中可以對所有的控制平面進行管理,因此觸發(fā)規(guī)則和動作可以被指定給不同的資源.例如,如果一個觸發(fā)規(guī)則被設(shè)置為監(jiān)控內(nèi)存帶寬,由于內(nèi)存帶寬的變化可能與Cache缺失率有關(guān),因此它的動作可以定義為Cache容量調(diào)整,通過調(diào)整Cache容量來影響Cache缺失率,進一步反饋到內(nèi)存帶寬.數(shù)據(jù)中心管理員負責根據(jù)SLA為不同的資源管理策略預(yù)先定義一系列動作和觸發(fā)規(guī)則,用戶可根據(jù)他們的QoS需求選擇適當?shù)腟LA.

Fig. 2 Programmable data plane architecture圖2 可編程數(shù)據(jù)平面架構(gòu)

1.2 可編程數(shù)據(jù)平面抽象

在PARD中,計算機的硬件部件被抽象為數(shù)據(jù)平面與控制平面2部分,其中數(shù)據(jù)平面用于執(zhí)行數(shù)據(jù)操作,而控制平面用于對數(shù)據(jù)平面的策略進行管理.以緩存控制器為例,數(shù)據(jù)平面中包含用緩存數(shù)據(jù)的DataArray與記錄緩存內(nèi)容的TagArray,以及替換策略的實現(xiàn),其控制平面包含替換策略的參數(shù)、統(tǒng)計信息等;對于內(nèi)存控制器而言,數(shù)據(jù)平面用于接收上層訪存請求,并將其轉(zhuǎn)換為內(nèi)存地址,發(fā)送到內(nèi)存陣列中,其控制平面用于控制地址映射與訪存調(diào)度策略.從以上2個例子我們可以發(fā)現(xiàn),PARD控制平面的可編程主要體現(xiàn)在其對數(shù)據(jù)平面所提供功能的控制,而數(shù)據(jù)平面所提供的功能在其設(shè)計完成后即已確定,如果需要增加額外的功能,則需要對數(shù)據(jù)平面重新進行設(shè)計,并對控制平面暴露相應(yīng)的接口.因此,控制平面的可編程能力受到數(shù)據(jù)平面所能提供功能的限制.

另一方面,PARD中的“Trigger→Action”機制在響應(yīng)時間上存在瓶頸:每當觸發(fā)條件發(fā)生后,需要經(jīng)過控制平面網(wǎng)絡(luò)將該事件傳遞到PRM,由運行在PRM中的軟件代碼來更新策略,并通過控制平面網(wǎng)絡(luò)寫回到控制平面中.由于受到控制平面網(wǎng)絡(luò)延遲以及PRM軟件代碼延遲的影響,該機制并不能達到特別高的響應(yīng)速度;同時并非所有的觸發(fā)條件發(fā)生后都需要在PRM進行全局處理,完全可以預(yù)定義一些動作,在控制平面本地完成處理.

為解決以上2個問題,本文提出的可編程數(shù)據(jù)平面架構(gòu)如圖2所示.在PARD中所提出的控制平面數(shù)據(jù)平面模型基礎(chǔ)上,在數(shù)據(jù)平面中增加了多個可編程處理器,連接數(shù)據(jù)平面中其他的邏輯部分,并通過其中的固件代碼對數(shù)據(jù)進行處理.控制平面依然使用3張控制表作為對外訪問的接口,通過控制平面網(wǎng)絡(luò)與集中式的平臺資源管理模塊通信.由于數(shù)據(jù)平面部件能夠執(zhí)行代碼,因此可以使用軟件代碼來實現(xiàn)反饋調(diào)節(jié),因此觸發(fā)邏輯已經(jīng)從控制平面中被移除.

要實現(xiàn)以上可編程數(shù)據(jù)平面架構(gòu),需要解決3個問題:1)如何為不同硬件部件的數(shù)據(jù)平面增加處理器邏輯;2)處理器如何設(shè)計,如何與控制平面進行通信;3)處理器邏輯如何編程.本文后續(xù)章節(jié)將針對以上3個問題進行分別闡述.

2 可編程數(shù)據(jù)平面

在討論數(shù)據(jù)平面處理器設(shè)計前,我們首先以內(nèi)存控制器和Cache控制器為例,討論可編程數(shù)據(jù)平面的設(shè)計.

2.1 內(nèi)存控制器

當前的處理器芯片通常會集成2~4個獨立的內(nèi)存控制器,每個控制器使用獨立的內(nèi)存通道.每個內(nèi)存通道連接到多個可并行訪問的rank,而每個rank又是由多個共享地址與數(shù)據(jù)總線的二維存儲陣列(bank)組成.內(nèi)存控制器的主要工作就是接收上游的讀寫請求,并將其轉(zhuǎn)換為下游的DRAM命令,完成數(shù)據(jù)傳輸.以內(nèi)存控制器作為數(shù)據(jù)平面,可以在地址映射和訪存調(diào)度2個位置增加可編程功能.

1) 地址映射.地址映射分為2部分,首先是通過處理器的頁表機制實現(xiàn)了從虛擬地址空間到物理地址空間的映射,虛擬化場景的出現(xiàn)在這一基礎(chǔ)上又增加了擴展頁表EPT機制,額外增加了一級虛擬機物理地址到主機物理地址的映射.之后是內(nèi)存控制器將處理器的物理地址空間映射到DRAM陣列中,通常使用靜態(tài)地址映射,通過某種固定的規(guī)則將物理地址空間映射到DRAM的bank,row,column中.

在PARD架構(gòu)中,通過在內(nèi)存控制器前增加MMU模塊,通過映射表將不同應(yīng)用標簽的訪存請求進行隔離.但這種方式只實現(xiàn)了一種固定的地址映射機制,即只能進行連續(xù)的大塊地址分配,無法實現(xiàn)EPT等技術(shù)所支持的細粒度內(nèi)存空間管理.為解決這一問題,可以將靜態(tài)的MMU模塊替換為一個處理器,能夠在其中編寫軟件代碼實現(xiàn)地址空間的映射.通過這種方式除了可以完成PARD中MMU的功能外,還可以實現(xiàn)更細粒度的空間管理,也可以實現(xiàn)現(xiàn)有虛擬化平臺中常見的基于內(nèi)容的內(nèi)存空間壓縮機制.除此之外,該處理器還可以通過對請求數(shù)據(jù)進行額外處理,以在硬件層面實現(xiàn)更復雜的如數(shù)據(jù)加密、敏感詞過濾等高級功能.

2) 訪存調(diào)度.在PARD的內(nèi)存控制平面中,只實現(xiàn)了簡單的基于優(yōu)先級的訪存調(diào)度,可以通過增加處理器的方式實現(xiàn)更為靈活的調(diào)度策略;同時也可以像PARDIS[18]工作一樣,將處理器加入到內(nèi)存控制器內(nèi)部的請求調(diào)度模塊中,根據(jù)不同應(yīng)用的需求實現(xiàn)不同的DRAM調(diào)度策略.

2.2 Cache控制器

Cache控制器的功能是對到達的請求進行緩存操作,使用不同的替換策略對數(shù)據(jù)訪問熱度進行預(yù)測,以提高訪存命中率和系統(tǒng)性能.其核心主要包括TagArray,DataArray和替換策略3個部分.以Cache控制器作為數(shù)據(jù)平面,可以在容量劃分與替換策略2個角度增加可編程功能.

1) 容量劃分.傳統(tǒng)的Cache并沒有提供容量劃分功能,因此不同應(yīng)用在共享Cache上運行會造成不同程度的干擾.Intel最新提出的CAT技術(shù)[29]在Cache上增加了按路的緩存容量劃分機制.但按路劃分并非適合所有的應(yīng)用,可以通過使用處理器替換固定的SetWay映射方式,根據(jù)應(yīng)用實現(xiàn)更為靈活的緩存容量劃分方式.

2) 替換策略.與容量劃分的需求類似,不同應(yīng)用的訪存模式不同,固定的緩存替換策略并不能很好地適應(yīng)所有應(yīng)用.因此使用處理器與軟件替換策略,與PARD的應(yīng)用區(qū)分機制結(jié)合,可以實現(xiàn)更為靈活高效的緩存.

3 數(shù)據(jù)平面處理器體系結(jié)構(gòu)

由于數(shù)據(jù)平面處理器位于請求處理的關(guān)鍵路徑上,為了保障系統(tǒng)的性能不受影響,需要從以下3個方面進行考慮:

1) 處理器需要執(zhí)行一系列指令才能完成對請求的處理,因此處理器需要工作在比其所在硬件部件更高頻率,以滿足硬件部件的性能需求;

2) 處理器的固件代碼執(zhí)行需要確定性,因此不能使用cache結(jié)構(gòu),而是使用scratchpad memory代替;

3) 由于高頻需求,因此處理器功能要盡可能簡單,一些必需的復雜邏輯(如數(shù)據(jù)壓縮與加密等)通過外部加速器的方式進行擴展.

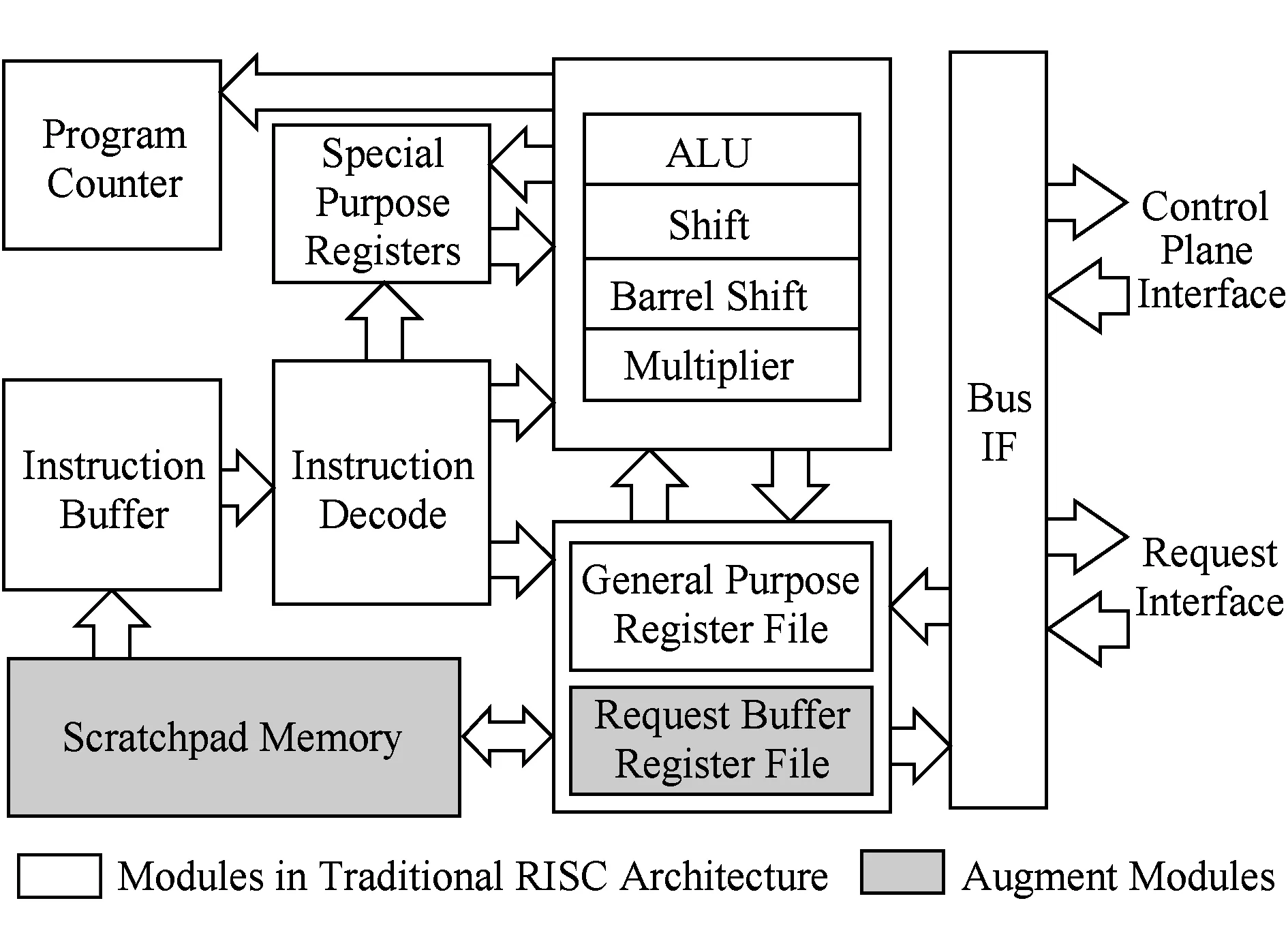

基于以上需求,我們選擇使用RISC作為數(shù)據(jù)平面處理器的基礎(chǔ)架構(gòu),如圖3所示.我們首先對傳統(tǒng)RISC架構(gòu)進行精簡,只保留其基本功能,以保證其頻率需求;同時增加scratchpad memory作為其指令與數(shù)據(jù)存儲,增加請求緩存接口用于接入硬件設(shè)備中,增加控制平面接口用于連接控制平面.

Fig. 3 Data plane processor block diagram圖3 數(shù)據(jù)平面處理器結(jié)構(gòu)圖

從第2節(jié)可知,對于內(nèi)存控制器與Cache,該處理器的主要工作包括:對請求進行調(diào)度、地址變換,對數(shù)據(jù)進行處理,生成控制信號(如Cache緩存與替換).要完成以上工作,該處理器需要具備基本的處理器功能外,還需要在數(shù)據(jù)類型、存儲模型和指令上進行擴展.

3.1 數(shù)據(jù)類型

數(shù)據(jù)平面處理器中執(zhí)行的算法代碼大都只是對輸入的請求進行處理,因此我們只有“無符號整數(shù)”和“請求”2種數(shù)據(jù)類型,如圖4所示.無符號整數(shù)的長度與處理器的位寬相同,都被設(shè)置為其所屬硬件的位寬,以節(jié)約請求處理時位寬轉(zhuǎn)換的開銷,保障請求處理的效率.

Fig. 4 Data types supported by the data plane processor圖4 數(shù)據(jù)平面處理器支持的數(shù)據(jù)類型

“請求”是一個變長數(shù)據(jù)類型,其中包含了固定的16位應(yīng)用標簽(DS-id)以及變長的請求數(shù)據(jù).以訪存請求為例,其中包含請求地址、長度、線程號、讀寫類型、鎖與緩存狀態(tài)等其他一些標志位;對于Cache替換請求,其中包含了請求地址、HitMiss標記以及其他一些標志位等信息.圖4給出了訪存請求以及Cache替換請求類型的示例.數(shù)據(jù)平面處理器本身并不關(guān)心請求類型中具體每個位的意義,而只是將其做一個整體進行處理,對每個域的解析或修改由其運行的固件代碼完成.

3.2 存儲模型

數(shù)據(jù)平面處理器中程序員可見的存儲結(jié)構(gòu)包含寄存器、請求緩存、scratchpad memory、IO地址空間4部分.與傳統(tǒng)的RISC架構(gòu)相同,數(shù)據(jù)平面處理器包含32個通用寄存器(r0~r31),用于進行算數(shù)邏輯運算,其中r0是常數(shù)0;除此之外,增加了4個用于保存“請求”類型數(shù)據(jù)的請求寄存器(s0~s3),可以通過請求緩存操作指令(rbget和rbput,參見3.3節(jié)),將請求輸入隊列中的請求讀取到該寄存器,或?qū)⒃摷拇嫫髦械恼埱蠹尤氲秸埱筝敵鲫犃兄校徽埱蠹拇嫫鞑荒苤苯訁⑴c算術(shù)邏輯計算,需要先將其部分數(shù)據(jù)讀取到通用寄存器后才能執(zhí)行計算;請求寄存器之間可以直接進行數(shù)據(jù)交換.處理器執(zhí)行的固件代碼與數(shù)據(jù)保存在scratchpad memory中,需要用戶自行管理.控制平面被映射為數(shù)據(jù)平面處理器的外設(shè),提供處理器的固件代碼ROM以及處理器的對外接口.

3.3 指令集

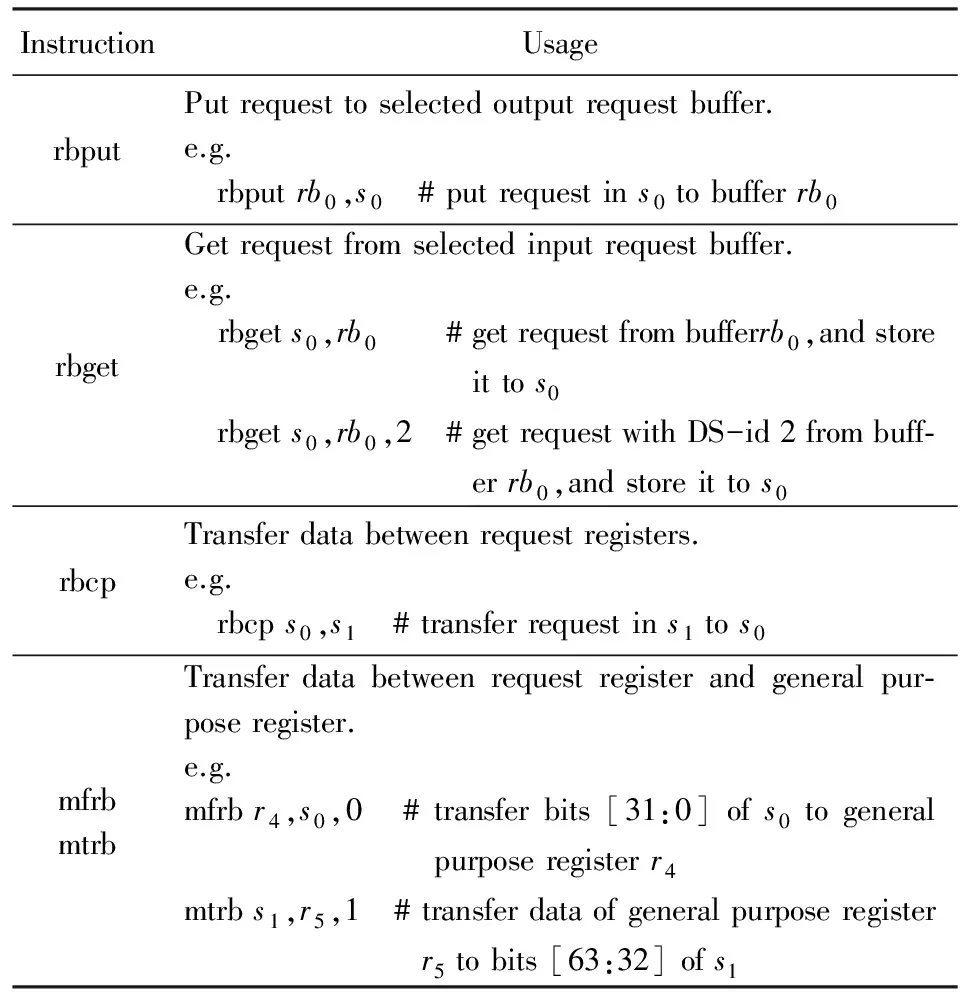

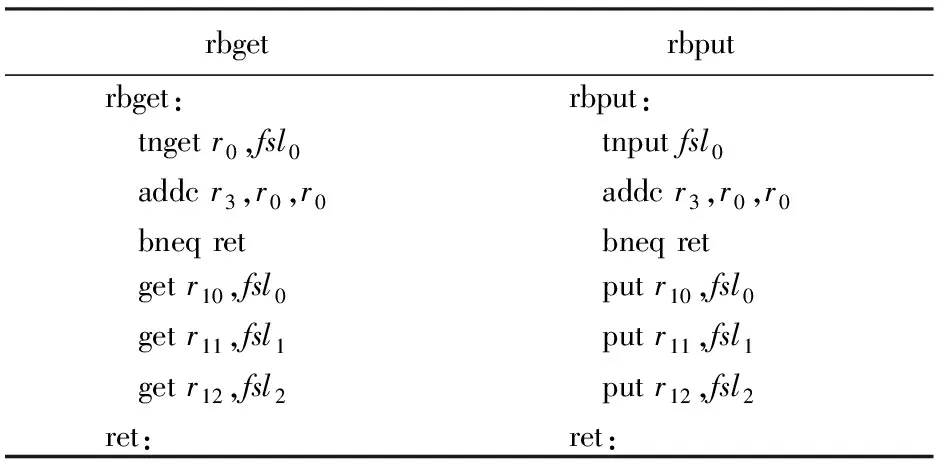

數(shù)據(jù)平面處理器使用RISC標準的算數(shù)邏輯、控制流和訪存指令,并在其基礎(chǔ)上額外增加了請求緩存操作指令,如表1所示:

Table 1 Instruction Extension for Data Plane Processor

請求緩存分為2部分:1)輸入緩存;2)輸出緩存.其中輸入緩存既可作為FIFO操作,也可基于DS-id進行內(nèi)容尋址;輸出緩存只能作為FIFO操作.用于請求緩存操作的指令如圖5所示,指令rbput可以將指定請求寄存器中的請求添加到輸出緩存隊列末尾.指令rbget有2種使用方式:1)將輸入緩存作為FIFO,取出隊列頭的請求到請求寄存器;2)通過DS-id對請求進行篩選,取出第1個滿足應(yīng)用標簽的請求到請求寄存器.指令rbcp用于在請求寄存器之間傳送數(shù)據(jù).指令mfrb用于將請求寄存器中的部分數(shù)據(jù)傳送到通用寄存器;指令mtrb與之相反,用于將通用寄存器的數(shù)據(jù)傳送到請求寄存器指定的位置.

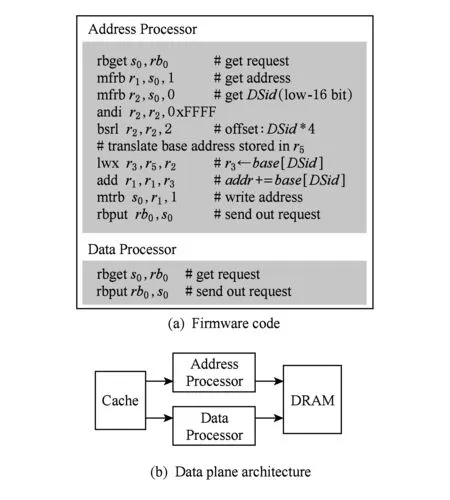

Fig. 5 Illustrative example of range address mapping圖5 段式地址映射示例

3.4 固件代碼示例

本節(jié)將以3段不同功能的固件代碼為例,介紹數(shù)據(jù)平面處理器的編程方法.

3.4.1 內(nèi)存地址映射

本示例用于實現(xiàn)PARD的內(nèi)存控制器控制平面所提供的地址映射功能,該功能只需要對訪存請求的地址進行修改,而請求的數(shù)據(jù)無需修改,我們將地址與數(shù)據(jù)分開由2個處理器進行處理,如圖5所示.對于數(shù)據(jù)處理器,其固件代碼只使用rbgetrbput指令對請求進行轉(zhuǎn)發(fā).地址處理器首先需要使用rbget指令獲取當前請求到請求寄存器,并使用mfrb指令將其中的地址與DS-id讀取到通用寄存器;而后通過查表的方式獲得該請求對應(yīng)的映射目的地址的基址,對請求地址進行變換,并使用mtrb指令將變換后的地址寫回到請求寄存器;最后通過rbput指令將新的訪存請求從處理器中送出,完成地址映射功能.

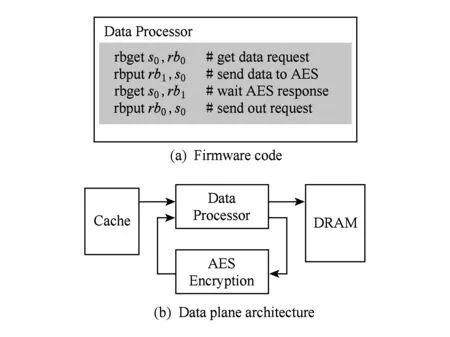

3.4.2 訪存數(shù)據(jù)加密

本示例實現(xiàn)訪存數(shù)據(jù)加密功能,由于數(shù)據(jù)加密操作通常需要耗費很長的時間,而且我們的數(shù)據(jù)平面處理器提供的指令集并不足以完成該操作.因此我們在外部實現(xiàn)了硬件AES加密模塊,并通過請求接口將其連接到數(shù)據(jù)平面處理器上,該結(jié)構(gòu)如圖6所示.基于該結(jié)構(gòu),數(shù)據(jù)處理器只需要將數(shù)據(jù)發(fā)送到AES模塊并等待其完成加密,將加密后的數(shù)據(jù)送出處理器即可.數(shù)據(jù)解密與加密過程類似,只需將數(shù)據(jù)發(fā)送到連接有解密模塊的請求接口即可.

Fig. 6 Illustrative example of memory access encryption圖6 訪存數(shù)據(jù)加密示例

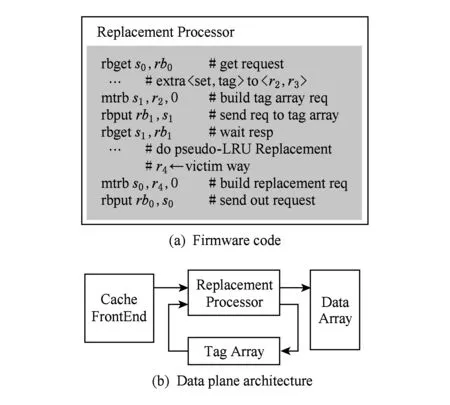

3.4.3 緩存替換策略

Fig. 7 Illustrative example of cache replacement policy圖7 緩存替換策略示例

本示例實現(xiàn)緩存替換策略功能,使用可編程處理器替換Cache中原有的LRU模塊,使用軟件實現(xiàn)基于二叉樹的偽LRU替換策略,如圖7所示.處理器固件代碼工作流程如下:1)處理器收到Cache前端的請求以及HitMiss信息,如果緩存命中則無需任何額外操作;2)對于緩存缺失的請求,首先從地址中解析出tag與set信息,并將解析后的set地址發(fā)送到TagArray,等待其返回該set的信息;3)根據(jù)TagArray返回的set信息以及內(nèi)部的數(shù)據(jù)結(jié)構(gòu)生成替換目標;4)將替換目標送出處理器.

4 原型實現(xiàn)

Fig. 8 Post placement&routing results (xc7vx690t device)圖8 FPGA原型系統(tǒng)的布局布線結(jié)果(xc7vx690t設(shè)備)

為了驗證可編程數(shù)據(jù)平面的思路,我們在Xilinx VC709(FPGA芯片型號為xc7vx690tffg1761-2)平臺上搭建了一個PARD的原型系統(tǒng),該原型系統(tǒng)使用4個MicroBlaze[30]作為處理器核,它們共享末級緩存和內(nèi)存控制器,使用AXI總線實現(xiàn)互連,CPU與共享末級緩存工作在133 MHz頻率,內(nèi)存總線工作在100 MHz頻率.系統(tǒng)的IO子系統(tǒng)包含2個以太網(wǎng)適配器和4個串口控制器;以太網(wǎng)適配器通過千兆光纖連接到外部交換機,4個串口控制器在FPGA內(nèi)部連接到PRM的虛擬串口,通過虛擬PRM的虛擬串口與外部通信.PRM是基于MicroBlaze的SoC系統(tǒng),使用I2C總線作為控制平面網(wǎng)絡(luò)連接到所有的控制平面,通過以太網(wǎng)與串口與外部進行通訊.該原型系統(tǒng)布局布線后的結(jié)果如圖8所示,其實現(xiàn)了PARD所描述的全硬件虛擬化功能,通過PRM中提供的固件將系統(tǒng)劃分為4個獨立的邏輯域,并可運行未修改的Linux操作系統(tǒng).

我們修改了該原型系統(tǒng)的內(nèi)存控制器部分,在其中增加了數(shù)據(jù)平面處理器(圖8箭頭所標識的區(qū)域),通過軟件代碼的方式實現(xiàn)內(nèi)存地址映射功能.為簡化實現(xiàn),我們使用精簡配置的MicroBlaze實現(xiàn)數(shù)據(jù)平面處理器的功能.

1) 將MicroBlaze配置為精簡模式,去除所有與數(shù)據(jù)平面處理器無關(guān)的可選指令,如硬件FPU、乘法器除法器、擴展指令等;關(guān)閉MMU、Cache、中斷異常等高級功能,只保留最基本的算術(shù)邏輯部分.通過精簡配置,MicroBlaze系統(tǒng)的頻率從133 MHz提高到了250 MHz.

2) 使用MicroBlaze提供的Stream Link接口作為數(shù)據(jù)平面處理器的請求接口.由于目前MicroBlaze的Stream Link接口是固定的32位AXIS接口,我們將多個Stream Link合并使用作為一個請求接口.

3) MicroBlaze提供putget指令實現(xiàn)對Stream Link的接口,通過合并多個put或get指令即可實現(xiàn)請求緩存指令rbput和rbget.如表2所示,“請求”類型的長度為12 B,我們使用3個MicroBlaze通用寄存器(r10~r12)作為請求寄存器,通過使用getput指令操作Stream Link接口fsl0~fsl2,實現(xiàn)rbget和rbput的功能.

Table 2 Request Buffer Instructions Implemented by MicroBlaze

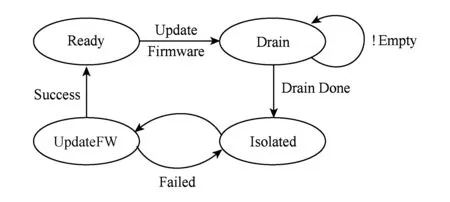

對于該原型系統(tǒng),另一個需要考慮的問題是如何對數(shù)據(jù)平面處理器的固件代碼進行更新,以實現(xiàn)“可編程”的功能.對數(shù)據(jù)平面處理器固件代碼更新可以分為兼容性更新與非兼容性更新.其中“兼容性”是指更新前后的代碼是否對數(shù)據(jù)平面的功能產(chǎn)生更改;對于非兼容性更新,需要首先關(guān)閉系統(tǒng)中所有正在運行的邏輯域,并在數(shù)據(jù)平面處理器固件更新完成后重新啟動邏輯域.對于兼容性更新,系統(tǒng)可實現(xiàn)無中斷運行,但需要對數(shù)據(jù)平面處理器與硬件的接口處進行額外的處理,如圖9所示,在收到更新固件命令后進入Drain狀態(tài),阻止請求繼續(xù)發(fā)送到數(shù)據(jù)平面處理器,等待數(shù)據(jù)平面處理器處理完全部請求,并將請求隊列排空后,使處理器進入Isolated隔離狀態(tài);之后完成對固件代碼的更新,新的固件代碼開始運行后,開始進行初始化操作,其中包括舊固件的狀態(tài)數(shù)據(jù)遷移步驟;在所有的初始化操作完成后,處理器恢復到就緒狀態(tài),重新開始處理請求,至此完成數(shù)據(jù)平面處理器固件代碼的兼容性更新操作.

Fig. 9 Compatible firmware update for data plane processor圖9 數(shù)據(jù)平面處理器兼容性固件更新狀態(tài)圖

5 性能評估

通過使用可編程處理器來替代硬件邏輯,可以極大增強設(shè)備的可編程能力,但由于處理器位于硬件請求處理的關(guān)鍵路徑,我們需要對其性能與資源開銷進行評估,以確保其不會對系統(tǒng)性能與開銷造成嚴重的影響.本節(jié)以內(nèi)存控制器的可編程數(shù)據(jù)平面為例,對其可編程數(shù)據(jù)平面的資源開銷進行分析;并通過stream與memcached兩種應(yīng)用負載來評估其對系統(tǒng)性能的影響;最后我們分析了可編程數(shù)據(jù)平面架構(gòu)對PARD體系結(jié)構(gòu)中“Trigger→Action”機制反饋時間的優(yōu)化.

5.1 系統(tǒng)延遲

與硬件邏輯實現(xiàn)相比,可編程處理器在系統(tǒng)中引入了額外的開銷,我們通過內(nèi)存控制器上增加本文所提出的可編程數(shù)據(jù)平面架構(gòu),實現(xiàn)與PARD中相同的地址映射功能來驗證該架構(gòu)對系統(tǒng)延遲的影響.

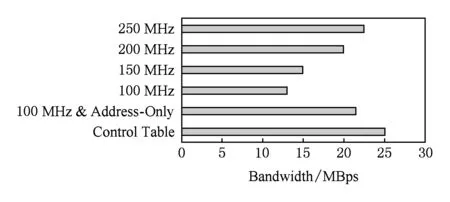

系統(tǒng)延遲的大小與應(yīng)用和固件功能相關(guān),因此我們選擇與硬件實現(xiàn)完全相同的地址映射功能,并使用內(nèi)存帶寬測試工具stream和內(nèi)存鍵值存儲應(yīng)用memcached對系統(tǒng)的延遲進行評估.由于受到FPGA設(shè)備的限制,在我們的平臺下MicroBlaze軟核處理器最高只能工作在250 MHz的頻率,我們選擇了100 MHz150 MHz200 MHz250 MHz四種不同的頻率對系統(tǒng)延遲進行了評估.

5.1.1 訪存帶寬

在PARD的控制平面設(shè)計中,實現(xiàn)地址映射的控制表并沒有引入額外的延遲開銷,其性能與直接訪問內(nèi)存控制器相同,受到MicroBlaze處理器性能的限制,我們能夠得到25.1 MBps的訪存帶寬,如圖10所示:

Fig. 10 Memory bandwidth of different processor configurations圖10 訪存帶寬對比

由于地址映射功能只需要對請求地址進行操作而無需對數(shù)據(jù)進行修改,因此我們實現(xiàn)了一個簡化版本的數(shù)據(jù)平面處理器(工作在100 MHz頻率),該處理器只對地址請求進行處理,數(shù)據(jù)繞過處理器直接發(fā)送到內(nèi)存控制器.在使用該設(shè)計后測得的訪存帶寬是21.5 MBps,與非處理器實現(xiàn)相比并沒有特別明顯的下降.

為了使數(shù)據(jù)平面處理器對訪存數(shù)據(jù)也能夠進行操作,我們將數(shù)據(jù)請求也發(fā)送到處理器進行處理,在100 MHz頻率下測得的訪存帶寬出現(xiàn)了明顯的下降,只有13 MBps.進一步提高數(shù)據(jù)平面處理器的工作頻率,帶寬基本呈線性上升,在150 MHz時能夠得到15 MBps的訪存帶寬;在200 MHz時,訪存帶寬提高到了20 MBps;而在250 MHz時,訪存帶寬達到了22.5 MBps.由于受到FPGA硬件的限制,我們無法實現(xiàn)更高頻率的數(shù)據(jù)平面處理器,但數(shù)據(jù)平面處理器的功能十分精簡,如果使用ASIC工藝,可以得到更高的頻率,因此其處理器的性能不會成為系統(tǒng)的瓶頸.

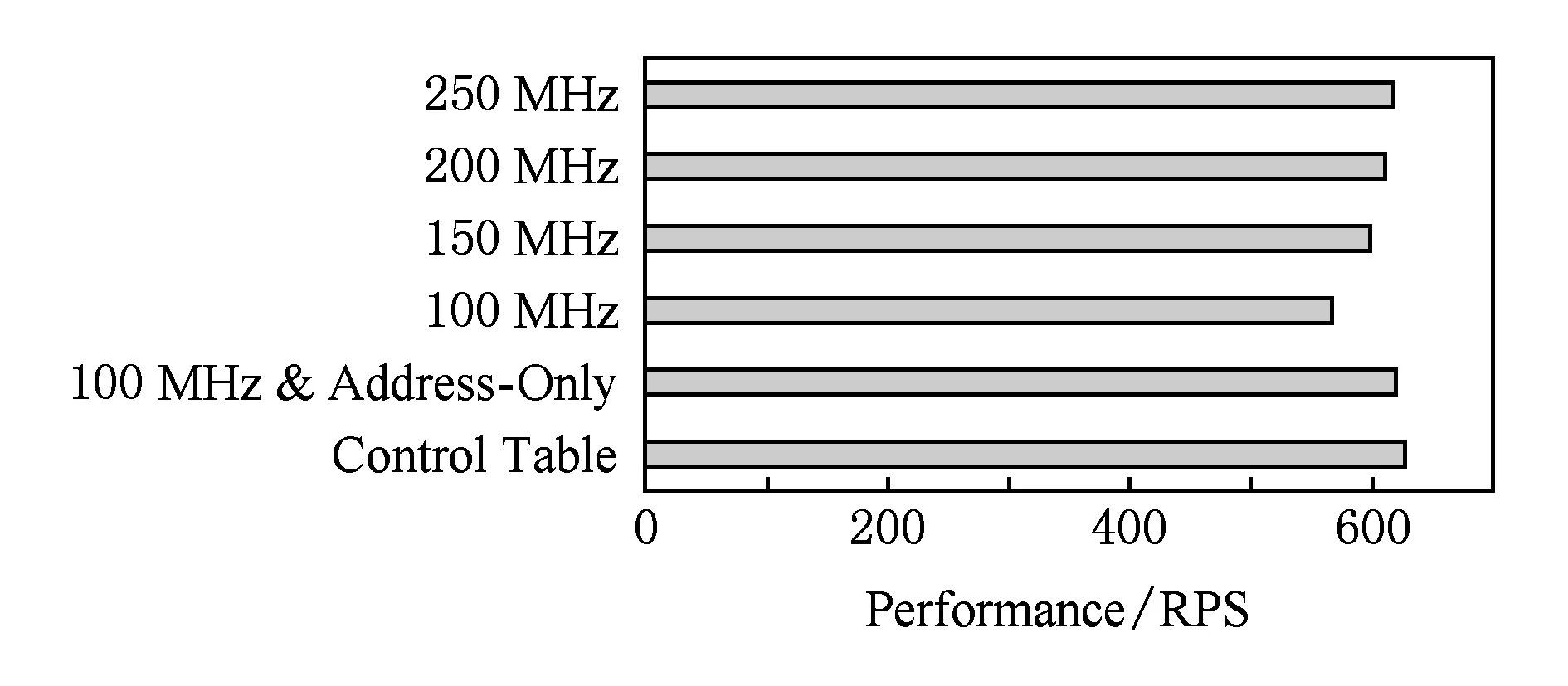

5.1.2 memcached 性能

訪存帶寬只能作為系統(tǒng)性能的一個評估指標,系統(tǒng)運行時的實際開銷要與應(yīng)用相關(guān)聯(lián).圖11給出了memcached在同硬件配置下的性能變化,與訪存帶寬的結(jié)果類似,memcached的性能與數(shù)據(jù)平面處理器頻率相關(guān),當工作在100 MHz頻率時,只能得到568RPS的性能,但如果處理器頻率提升到250 MHz,其性能(618RPS)與使用控制表的方案(628RPS)基本接近.

Fig. 11 Performance of memcached benchmark圖11 memcached性能

5.2 資源開銷

可編程數(shù)據(jù)平面的資源開銷主要在處理器邏輯及其使用的scratchpad memory兩個方面.在通過配置精簡后,MicroBlaze處理器所占用的資源量大大減少,其Slice(LUT和FF)占用只有完整配置的50%左右,scratchpad memory的容量由固件代碼的大小決定,當前的實現(xiàn)中我們?yōu)槠浔A袅?2 KB的容量,在FPGA中占用了8個RAMB36資源.原型系統(tǒng)中主要的硬件部件與可編程數(shù)據(jù)平面占用的FPGA資源如表3所示.可以看到可編程數(shù)據(jù)平面在只占用有限的FPGA資源下,為硬件增加了更為靈活的可編程能力.

Table 3 Resource Consumption for xc7vx690t Device

5.3 反饋時間

在PARD體系結(jié)構(gòu)基于表的控制平面設(shè)計中,“Trigger→Action”機制的反饋時間可以主要分為Trigger事件檢測、控制平面網(wǎng)絡(luò)傳送事件消息、PRM處理事件以及控制平面網(wǎng)絡(luò)傳送Action的參數(shù)修改4個階段.其中第1階段由控制表硬件邏輯完成,可以在有限的時鐘周期內(nèi)完成.第2階段和第4階段由于需要使用控制平面網(wǎng)絡(luò)傳送數(shù)據(jù),因此其響應(yīng)時間與控制平面網(wǎng)絡(luò)的速率相關(guān).在我們目前的原型系統(tǒng)中,由于使用了I2C總線作為控制平面網(wǎng)絡(luò),其最高速率為1 Mbps,對于一個32 b的事件消息以及一組96 b的參數(shù)修改消息,至少需要128 μs完成數(shù)據(jù)傳輸,如果需要傳輸更多的消息則需要消耗更長的時間.第3階段PRM處理中,需要經(jīng)過控制平面驅(qū)動、內(nèi)核、用戶態(tài)3個層次進行處理,也需要消耗一定的時間.在采用可編程數(shù)據(jù)平面架構(gòu)后,對Trigger事件的反饋調(diào)節(jié)代碼可以直接在數(shù)據(jù)平面的固件代碼中完成,消除了PARD原有設(shè)計中需要經(jīng)過PRM進行統(tǒng)一處理的時間消耗,實現(xiàn)更快速的反饋響應(yīng).

6 總 結(jié)

本文展示了一種計算機體系結(jié)構(gòu)內(nèi)可編程數(shù)據(jù)平面架構(gòu),通過在計算機硬件設(shè)備中增加可編程處理器,通過可編程處理器的固件代碼完成對硬件請求的處理,使硬件設(shè)備具備了更加靈活的可編程特性.我們的實驗結(jié)果表明,這種可編程數(shù)據(jù)平面的設(shè)計并沒有增加特別大的性能開銷,可以用于在數(shù)據(jù)中心等需求不斷變化的場景中,根據(jù)應(yīng)用需要的變化調(diào)整硬件實現(xiàn)策略以達到最優(yōu)效果.

[1]Kaplan J M, Forrest W, Kindler N. Revolutionizing data center energy efficiency[R]. New York: McKinsey & Company, 2008

[2]Goasduff L, Pettey C. Gartner says efficient data center design can lead to 300 percent capacity growth in 60 percent less space[OL]. 2010[2016-02-26]. http:www.gartner.comnewsroomid1472714

[3]Delimitrou C, Kozyrakis C. Paragon: QoS-aware scheduling for heterogeneous datacenters[C]Proc of the 18th Int Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS’13). New York: ACM, 2013: 77-88

[4]Delimitrou C, Kozyrakis C. Quasar: Resource-efficient and QoSaware cluster management[C]Proc of the 19th Int Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS’14). New York: ACM, 2014: 127-144

[5]Leverich J, Kozyrakis C. Reconciling high server utilization and sub-millisecond quality-of-service[C]Proc of the 2014 EuroSys Conf. New York: ACM, 2014: 4

[6]Mars J, Tang Lingjia, Hundt R, et al. Heterogeneity in “homogeneous” warehouse-scale computers: A performance opportunity[J]. Computer Architecture Letters, 2011, 10(2): 29-32

[7]Liu Lei, Cui Zehan, Xing Mingjie, et al. A software memory partition approach for eliminating bank-level interference in multicore systems[C]Proc of the 21st Int Conf on Parallel Architectures and Compilation Techniques. New York: ACM, 2012: 367-376

[8]Liu Lei, Li Yong, Cui Zehan, et al. Going vertical in memory management: Handling multiplicity by multi-policy[C]Proc of the 41st Annual Int Symp on Computer Architecture (ISCA’14). Piscataway, NJ: IEEE, 2014: 169-180

[9]Sanchez D, Kozyrakis C. The ZCache: Decoupling ways and associativity[C]Proc of the 43rd Annual IEEEACM Int Symp on Microarchitecture (MICRO’43). Los Alamitos, CA: IEEE Computer Society, 2010: 187-198

[10]Sanchez D, Kozyrakis C. Vantage: Scalable and efficient fine-grain cache partitioning[C]Proc of the 38th Annual Int Symp on Computer Architecture (ISCA’11). New York: ACM, 2011: 57-68

[11]Qureshi M K, Patt Y N. Utility-based cache partitioning: A low-overhead, high-performance, runtime mechanism to partition shared caches[C]Proc of the 39th Annual IEEEACM Int Symp on Microarchitecture (MICRO’39). Los Alamitos, CA: IEEE Computer Society, 2006: 423-432

[12]Kasture H, Sanchez D. Ubik: Efficient cache sharing with strict QoS for latency-critical workloads[C]Proc of the 19th Int Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS’14). New York: ACM, 2014: 729-742

[13]Jia Yaocang, Wu Chenggang, Zhang Zhaoqing. Program’s performance profiling optimization for guiding static cache partitioning[J]. Journal of Computer Research and Development, 2012, 49(1): 93-102 (in Chinese)(賈耀倉, 武成崗, 張兆慶. 指導cache靜態(tài)劃分的程序性能profiling優(yōu)化技術(shù)[J]. 計算機研究與發(fā)展, 2012, 49(1): 93-102)

[14]Muralidhara S P, Subramanian L, Mutlu O, et al. Reducing memory interference in multicore systems via application-aware memory channel partitioning[C]Proc of the 44th Annual IEEEACM Int Symp on Microarchitecture (MICRO’44). New York: ACM, 2011: 374-385

[15]Jia Gangyong, Li Xi, Wan Jian, et al. A memory partition policy for mitigating contention[J]. Journal of Computer Research and Development, 2015, 52(11): 2599-2607 (in Chinese)(賈剛勇, 李曦, 萬健, 等. 一種減少競爭的內(nèi)存劃分方法[J]. 計算機研究與發(fā)展, 2015, 52(11): 2599-2607)

[16]Computing Community Consortium (CCC). 21st century computer architecture: A community white paper[OL]. 2012[2016-02-26]. http:cra.orgcccdocsinit21stcentur yarchitecturewhitepaper.pdf

[17]Ma Jiuyue, Sui Xiufeng, Sun Ninghui, et al. Supporting differentiated services in computers via programmable architecture for resourcing-on-demand (PARD)[C]Proc of the 20th Int Conf on Architectural Support for Programming Languages and Operating Systems (ASPLOS’15). New York: ACM, 2015: 131-143

[18]Bojnordi M N, Ipek E. PARDIS: A programmable memory controller for the DDRx interfacing standards[C]Proc of the 39th Annual Int Symp on Computer Architecture (ISCA’12). Los Alamitos, CA: IEEE Computer Society, 2012: 13-24

[19]Martin J, Bernard C, Clermidy F, et al. A micropro-grammable memory controller for high-performance dataflow applications[C]Proc of European Solid-State Circuits Conf. Piscataway, NJ: IEEE, 2009: 348-351

[20]Kornaros G, Papaefstathiou I, Nikologiannis A, et al. A fully programmable memory management system optimizing queue handling at multi gigabit rates[C]Proc of the 40th Annual Design Automation Conf (DAC’ 03). New York: ACM, 2003: 54-59

[21]Kuskin J, Ofelt D, Heinrich M, et al. The stanford FLASH multiprocessor[C]Proc of the 21st Annual Int Symp on Computer Architecture (ISCA’94). Los Alamitos, CA: IEEE Computer Society, 1994: 302-313

[22]Reinhardt S K, Larus J R, Wood D A. Tempest and typhoon: User-level shared memory[C]Proc of the 21st Annual Int Symp on Computer Architecture (ISCA’94). Los Alamitos, CA: IEEE Computer Society, 1994: 325-336

[23]Carter J, Hsieh W, Stoller L, et al. Impulse: Building a smarter memory controller[C]Proc of the 5th Int Symp on High Performance Computer Architecture (HPCA’99). Los Alamitos, CA: IEEE Computer Society, 1999: 70-79

[24]Browne M, Aybay G, Nowatzyk A, et al. Design verification of the S3.mp cache coherent shared-memory system[J]. IEEE Trans on Computers, 1998, 47(1): 135-140

[25]Bosshart P, Daly D, Gibb G, et al. P4: Programming protocol-independent packet processors[J]. ACM SIGCOMM Computer Communication Review, 2014, 44(3): 87-95

[26]Song H. Protocol-oblivious forwarding: Unleash the power of SDN through a future-proof forwarding plane[C]Proc of the 2nd ACM SIGCOMM Workshop on Hot Topics in Software Defined Networking (HotSDN’13). New York: ACM, 2013: 127-132

[27]Jeyakumar V, Alizadeh M, Kim C, et al. Tiny packet programs for low-latency network control and monitoring[C]Proc of the 12th ACM Workshop on Hot Topics in Networks (HotNets-XII). New York: ACM, 2013: 8

[28]Sivaraman A, Winstein K, Subramanian S, et al. No silver bullet: Extending SDN to the data plane[C]Proc of the 12th ACM Workshop on Hot Topics in Networks (HotNets-XII). New York: ACM, 2013: 19

[29]Intel Corporation. Improving real-time performance by utilizing cache allocation technology[OL]. 2015 [2016-02-26]. http:www.intel.comcontentdamwwwpublicusendocumentswhite-paperscache-allocation-technology-white-paper.pdf

[30]Xilinx Corporation. MicroBlaze soft processor core[OL]. 2015 [2016-02-26]. http:www.xilinx.comproductsdesign-toolsmicroblaze.html

Ma Jiuyue, born in 1988. PhD from the Institute of Computing Technology, Chinese Academy of Sciences. His main research interests include computer archi-tecture and operating system (majiuyue@ncic.ac.cn).

Yu Zihao, born in 1991. PhD candidate in the Institute of Computing Technology, Chinese Academy of Sciences. His main research interests include computer architecture and operating system (yuzihao@ict.ac.cn).

Bao Yungang, born in 1980. Professor and PhD supervisor. Member of CCF. His main research interests include computer architecture, operating system and system performance modeling and evaluation.

Sun Ninghui, born in 1968. Professor and PhD supervisor. His main research interests include computer architecture, high perfor-mance computing and distributed OS (snh@ict.ac.cn).

A Programmable Data Plane Design in Computer Architecture

Ma Jiuyue1,2, Yu Zihao1,2, Bao Yungang1, and Sun Ninghui1

1(InstituteofComputingTechnology,ChineseAcademyofSciences,Beijing100190)2(UniversityofChineseAcademyofSciences,Beijing100049)

With the development of the Internet and cloud computing, more and more applications are migrated from local host to the cloud. In the cloud computing environment, these applications will finally be deployed to run in data centers, with the sharing of computer infrastructures. Influenced by the complexity and the variability of the applications running in data center, some fixed-function hardware components in traditional computer architecture, such as last-level cache, memory controller, IO controller, can not meet the requirements of deploying these application together in one data center. To adapt to these dynamic requirements, programmable hardware is needed from the view of computer architecture level, to make the function of computer hardware adaptable according to the application requirements. A programmable data plane design for computer architecture is presented, which brings programmability to hardware components by integrating programmable processors into the state-of-the-art hardware components, and let these new processors process hardware requests by firmware code. The functions of hardware components can be extended by updating firmware running on the processors. An FPGA prototype is implemented. Evaluation results show that the programmable data plane design brings flexible programmability to hardware by reasonable resource consumption, without introducing too much overhead to the original system performance. This makes it possible for the computer hardware to adapt to the dynamic requirement of application running in data centers.

programmable; processor; data center; server; quality of service (QoS)

2016-03-02;

2016-05-03

國家“九七三”重點基礎(chǔ)研究發(fā)展計劃基金項目(2011CB302500);國家自然科學基金項目(61420106013,61221062,61202062) This work was supported by the National Basic Research Program of China (973 Program) (2011CB302500) and the National Natural Science Foundation of China (61420106013, 61221062, 61202062).

TP303