基于FPGA與ARM的智能合并單元設計

郭艷平

近年來,隨著社會經濟的快速發展和科學技術的日益進步,智能電網在一定程度上已經成為電力系統發展的主要方向,普遍受到世界各國的關注與研究,其所涵蓋的工程領域眾多,如變電、輸電以及配電等。同時,智能變電站作為智能電網必不可少的組成部分,利用智能化設備有助于實現全站信息的數字化、通信網絡平臺的網絡化以及信息共享的標準化。然而,基于FPGA與ARM的智能合并單元在一定程度上可以為智能變電站的實現提供堅實的基礎。

【關鍵詞】FPGA ARM 智能合并 單元設計

1 智能合并單元的意義

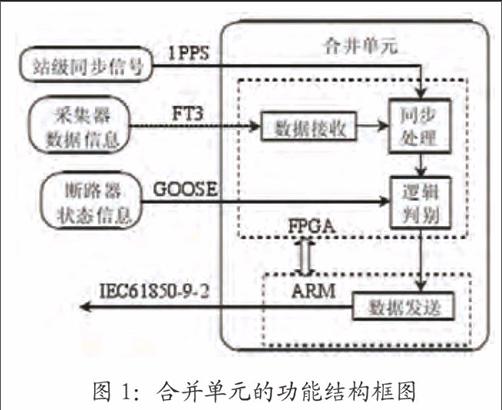

所謂的合并單元在2002年所頒布的IEC標準中最早將其定義為能夠對二次轉換器的電流或者電壓利用時間能夠同時進行轉換的一種物理單元,其在一定程度上是電子式互感器中的一個重要組件,并且還是一個相對獨立的單元,對其輸入的通道、編碼的方式等都能夠利用通信對點的方式進行準確而又詳細的描述。本文基于FPGA與ARM進行了智能合并單元設計,功能具體的原理如圖1所示,智能化合并單元設計較之前相比具有非常顯著的意義。

(1)在進行太網接口的過程中能夠充分利用和發揮ARM本身對處理數據的能力,在一定程度上有助于操作的簡化,同時FPGA的I/O異常豐富,能夠使得并行處理的速度顯著加快,基于FPGA與ARM本身的功能可以極大的滿足合并單元的多種需求,如同時處理多個任務、實時性和可靠性等。

(2)ARM作為主處理器能夠有效的延時補償、標定、發送采樣的信息,并且還能夠實現對FPGA的配置;而FPGA作為輔處理器能夠實現對數據的同步接收以及邏輯上的判斷,通過雙口RAM的利用可以直接向ARM提供一定的采樣值等各方面的數據信息。

2 數據接收模塊設計

所謂的數據接收模塊主要通過采集器所發出的多路異步串行數據在經過冗余循環的有效性校驗之后,按照先后順序將數據并行發送到后續模塊中。鑒于IEC 61850對于采集器和合并單元之間的通信數據進一步做出明確的規定,因此為保證電子式互感器閉鎖告警供功能的正常啟動,便可以在通信數據在電流和電壓數字量進行串行傳輸的過程中將一次設備的狀態量添加進去。同時,由于數據傳輸在不同通道內保持著一定的相對獨立性,所到達合并單元的先后關系是不固定的,而利用FPGA不僅有助于同時接收和校驗多路數據,并且還能憑借其本身的FIFO功能對多路數據進行正確的排序。此外,在排序數據的過程中還可以將最大等待的時間設置下來,若某路的數據不能正常的傳輸到目的地時,便可以通過FIFO將該路數據借助狀態信息位將故障告知二次設備。

3 數據處理模塊設計

3.1 同步模塊的處理

同步處理在一定程度上可以將對多路電量的模擬與采樣時刻同步,具體的包括不同采集器和合并單元之間的同步,從而有助于二次設備供給電流和電壓在時序上能夠保持一致性。不同采集器之間的同步是借助站級內的同步信號進行相應的插值算法,有助于不同采集器在相同時刻進行數據的采樣,若一旦發生站級同步信號失效的情,FPGA內的晶振分頻便會立即啟動相應的還會產生一定的采脈沖,并且還能將報警信號及時的發送至二次設備。不同合并單元之間的同步是在進行延時測算的基礎上將不同合并單元內的采集時刻歸算到實際時刻,其所輸出的采樣值的模擬報文中的時間標簽信息實際上就已經為同一合并單元SAV輸出的同步性,因此不同SAV實際采樣時刻可以利用當前的時刻減去不同合并單元的固有延時。

3.2 邏輯判別模塊

無論是單母分段還是雙母線,就接線方式而言每段母線的并行既可以是并列也可以是分列,不同母線之前的出線在一定程度上可以為負荷的不間斷供電提供重要的保障。邏輯判別模式在一定程度上可以借助相關邏輯判別的機制軟件并列和切換母線的電壓。同時合并單元通過總的過程線經相關斷路器和刀閘等方面的狀態信息,根據事先就已經設置好的機制軟件并列或者切換電壓,對母線電子式電壓互感器進行科學的選擇,從而有助于將一定的電壓傳送至智能化電子設備當中,如保護、測控以及計量等,并且在故障發生時還可以將相關的告警信息及時的發送出去。

4 數據發送模塊設計

數據發送模塊主要對定前端已經處理好的信息進行負責,在此基礎上按照相關的標準對通信進行約束,然后利用太網實時的將已經組幀好的數據單元發布出去。IEC 61850-9-2對串行鏈接上的采樣值進行了科學的規范,使其能夠支持ACSI的一系列服務,如傳輸采樣值的報文,控制采樣值的塊讀和塊寫。一方面,同采樣值報文的傳輸可以在一定的標準約束下對相關的數據鏈接層進行科學的映射;另一方面,控制采樣值的塊讀和塊寫可以及時有效的控制采樣值的傳輸屬性,如數據集、采樣的頻率和使能,從而可以最大限度的對采樣值的傳輸模塊進行靈活的配置。本文通過采用一種事前就已經配置好的采樣值控制模塊,進而有助于靈活的采樣值傳輸模型的相關映射方案進行靈活的定義,并且根據工程的實際需要完成了對采樣值數據集的提前配置,靈活的配置工程的實際間隔,在一定程度上極大的避免了MMS在映射時所面臨的各種困難。

5 總結

綜上所述,本文通過對智能合并單元意義的簡單介紹,從數據接收模塊設計、數據處理模塊設計、數據發送模塊設計等方面對基于FPGA與ARM的智能合并單元設計進行了系統化的分析,從而一定程度上為智能變電站的實現提供了堅實的基礎。

參考文獻

[1]朱利鵬,彭曉濤,楊軍.多ARM協同架構的智能合并單元設計[J].中國電力,2015(01):146-152.

[2]何小慶.基于FPGA的數字化牽引變電所合并單元研究與設計[D].成都:西南交通大學,2014.

作者單位

南京航空航天大學金城學院自動化系 江蘇省南京市 211156