胚胎型仿生自修復(fù)系統(tǒng)硬件消耗分析

孟亞峰 朱賽 韓春輝

摘 要: 胚胎型仿生自修復(fù)系統(tǒng)具有實時自修復(fù)能力,可用于高可靠性電子系統(tǒng)的設(shè)計。在設(shè)計過程中,其硬件消耗是工程師十分關(guān)心的問題。在分析胚胎型仿生自修復(fù)系統(tǒng)結(jié)構(gòu)基礎(chǔ)上,根據(jù)自修復(fù)過程特征,建立了其系統(tǒng)硬件消耗模型。并以三模冗余自修復(fù)系統(tǒng)為對比,對胚胎型仿生自修復(fù)系統(tǒng)的硬件消耗進行了仿真分析。分析表明,胚胎型仿生自修復(fù)系統(tǒng)在大規(guī)模、高自修復(fù)能力的電路設(shè)計中具有優(yōu)越性,且通過電子細胞輔助電路的優(yōu)化設(shè)計,可以降低自修復(fù)過程中的硬件消耗。

關(guān)鍵詞: 電子細胞輔助電路; 胚胎電子陣列; 硬件消耗; 自修復(fù)能力

中圖分類號: TN911?34; TP302.8 文獻標(biāo)識碼: A 文章編號: 1004?373X(2017)06?0129?04

Abstract: The embryonic bio?inspired self?repairing system has the real?time self?repairing ability, and can be used in the design of the electronic system with high reliability. On the basis of analyzing the structure of the embryonic bio?inspired self?repairing system, the system hardware consumption model was established according to the characteristics of the self?repairing process. In comparison with the triple?modular redundancy self?repairing system, the simulation analysis for the hardware consumption of the embryonic bio?inspired self?repairing system was performed. The analysis results show that the embryonic bio?inspired self?repairing system has superiority in the design of the large?scale circuit with high self?repairing capacity, and can reduce the hardware consumption in the self?repairing process by means of the optimization design of the electronic cell auxiliary circuit.

Keywords: electronic cell auxiliary circuit; embryonic array; hardware consumption; self?repairing ability

0 引 言

胚胎型仿生自修復(fù)系統(tǒng)是受多細胞生物體結(jié)構(gòu)和胚胎發(fā)育過程啟發(fā)提出的一種仿生硬件[1?2],與生物體類似,具有自檢測、自修復(fù)能力,可用于航空、航天等領(lǐng)域及復(fù)雜電磁環(huán)境下高可靠性電子設(shè)備的設(shè)計。

胚胎型仿生自修復(fù)系統(tǒng)自提出以來,研究者對其系統(tǒng)結(jié)構(gòu)[3?5]、自修復(fù)機制[6?7]、自修復(fù)實驗[8]等方面進行了深入研究,提出了多種系統(tǒng)結(jié)構(gòu)框架[9?12],并實現(xiàn)了小規(guī)模電路的自修復(fù)實驗。利用胚胎型仿生自修復(fù)系統(tǒng)進行電路設(shè)計時,在一定自修復(fù)能力下,系統(tǒng)硬件消耗是電子工程師十分關(guān)心的問題。學(xué)者對胚胎型仿生自修復(fù)中的硬件消耗研究較少,缺少系統(tǒng)層面的硬件消耗分析,無法指導(dǎo)胚胎型仿生硬件的應(yīng)用及研究。

本文根據(jù)胚胎型仿生自修復(fù)系統(tǒng)結(jié)構(gòu)及其自修復(fù)原理,建立了系統(tǒng)自修復(fù)實現(xiàn)中的硬件消耗模型,并與經(jīng)典的三模冗余系統(tǒng)進行了硬件消耗對比。通過分析,明確了胚胎型仿生自修復(fù)系統(tǒng)的應(yīng)用范圍,對胚胎型仿生自修復(fù)系統(tǒng)的設(shè)計和應(yīng)用具有指導(dǎo)意義。

1 胚胎型仿生自修復(fù)系統(tǒng)基礎(chǔ)知識

1.1 胚胎型仿生自修復(fù)系統(tǒng)

胚胎型仿生硬件是由結(jié)構(gòu)相同的電子細胞排列而成的均勻二維陣列,因此也被稱為胚胎電子陣列,其結(jié)構(gòu)如圖1所示[13]。胚胎電子陣列中的每個電子細胞都是具有一定數(shù)據(jù)處理能力的邏輯單元,由地址產(chǎn)生器、基因庫、I/O單元、邏輯單元和自檢測單元(Build?In Test, BIT)組成。地址產(chǎn)生器用來計算細胞在電路中的位置,產(chǎn)生細胞在電路中的惟一標(biāo)識,細胞通過該標(biāo)識表達對應(yīng)基因,執(zhí)行特定的功能;基因庫存儲整個電路的所有基因,不同的基因代表不同的電路功能及細胞連接方式;I/O單元進行細胞與周圍細胞的連接控制,在表達基因配置下控制細胞與陣列中其他細胞的信號交互;邏輯單元執(zhí)行細胞的邏輯功能,在不同的表達基因配置下執(zhí)行不同的邏輯功能;BIT在細胞運行過程中實時檢測細胞狀態(tài)。

陣列中每個細胞根據(jù)自身位置表達基因庫中的特定基因,確定I/O單元連接方式及邏輯塊執(zhí)行的邏輯功能,整個陣列的細胞一起完成目標(biāo)電路功能。運行過程中,細胞內(nèi)的BIT模塊實時檢測細胞狀態(tài),檢測到細胞故障時,對外發(fā)出細胞故障信號觸發(fā)修復(fù)機制,移除故障細胞,消除故障對目標(biāo)電路的影響。剩余細胞重新計算位置并更新表達基因,執(zhí)行新的細胞功能及連接。通過故障細胞的移除和正常細胞的替代,陣列上目標(biāo)電路功能得以維持,完成胚胎電子陣列上目標(biāo)電路的自修復(fù)。

1.2 自修復(fù)過程及自修復(fù)能力

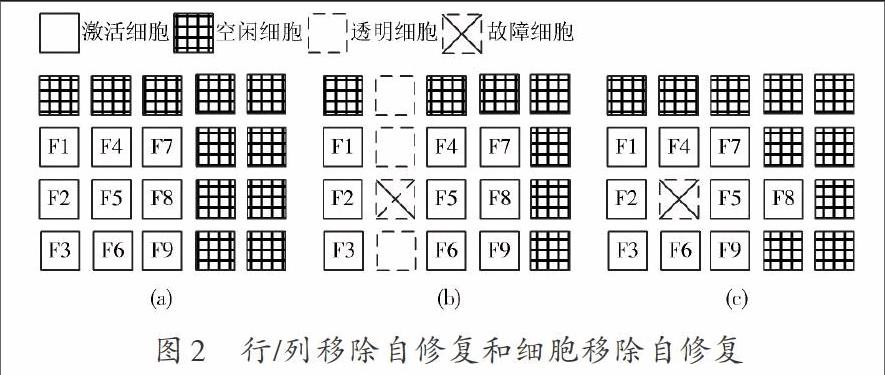

胚胎型仿生自修復(fù)系統(tǒng)通過移除故障細胞,消除故障對目標(biāo)電路的影響,從而完成自修復(fù)。根據(jù)移除故障細胞的方式不同,其自修復(fù)方式主要為行/列移除自修復(fù)和細胞移除自修復(fù),如圖2所示。

行/列移除自修復(fù)指當(dāng)胚胎電子陣列中某個電子細胞發(fā)生故障后,移除故障電子細胞所在的整行/列電子細胞,故障細胞所在行/列及其后所有激活行/列的功能向后移一行/列,直至最后使用一個空閑的行/列,如圖2(b)所示。細胞移除自修復(fù)指當(dāng)陣列中某個細胞單元故障后,移除該故障細胞,并將該行/列內(nèi)故障單元細胞及位于故障單元后的細胞單元的功能后移,直至使用該行/列內(nèi)的空閑細胞,如圖2(c)所示。電路的自修復(fù)能力(Self?Repair Capacity,SRC)是系統(tǒng)自修復(fù)的重要指標(biāo),表征了電路能夠從故障狀態(tài)修復(fù)到正常狀態(tài)的能力。對于移除自修復(fù)模式來說,電路的自修復(fù)能力即為胚胎電子陣列中冗余行/列資源的數(shù)目。

2 硬件消耗建模

根據(jù)胚胎電子陣列和經(jīng)典的N模冗余自修復(fù)特點,考慮自修復(fù)過程中自修復(fù)能力指標(biāo),進行了硬件消耗的建模。

2.1 胚胎電子陣列與FPGA結(jié)構(gòu)比較

FPGA與胚胎電子陣列結(jié)構(gòu)相似,由許多獨立的可編程邏輯模塊CLB(Configurable Logic Block)排成陣列組成,用戶通過可編程的互連資源將這些模塊連接起來構(gòu)成任何復(fù)雜的邏輯電路。

當(dāng)前使用FPGA進行目標(biāo)電路設(shè)計時,電路映射到FPGA基本單元CLB上。CLB中包含多個Slice,每個Slice中包括兩個LUT、兩個觸發(fā)器和相關(guān)邏輯,不同的CLB間通過開關(guān)盒進行連接。

胚胎電子陣列進行目標(biāo)電路的實現(xiàn)時,與FPGA類似,目標(biāo)電路映射到電子細胞上,電子細胞由LUT,F(xiàn)F,開關(guān)盒和基因存儲模塊、自檢測模塊等組成。在硬件消耗上,相當(dāng)于在FPGA基本單元上增加了基因存儲模塊、自檢測模塊及控制模塊。

為了在相同級別上驗證目標(biāo)電路的硬件消耗,分別在設(shè)計的FPGA陣列上和胚胎電子陣列上進行目標(biāo)電路的實現(xiàn)。兩種陣列的功能模塊、開關(guān)盒結(jié)構(gòu)相同,陣列上目標(biāo)電路實現(xiàn)方式相同。

2.2 硬件消耗模型

假設(shè)某電路由m×n個基本單元組成,每個單元消耗為ω。電子細胞在每個功能單元的基礎(chǔ)上增加了基因存儲、自檢測及修復(fù)控制電路,設(shè)所增加的輔助電路與原電路的硬件消耗比為α,其值大小取決于電路設(shè)計水平及自檢測中故障覆蓋率。則電路由基本邏輯單元組成時,其硬件消耗為mnω;電路由電子細胞實現(xiàn)時,其硬件消耗為mnω(1+α)。

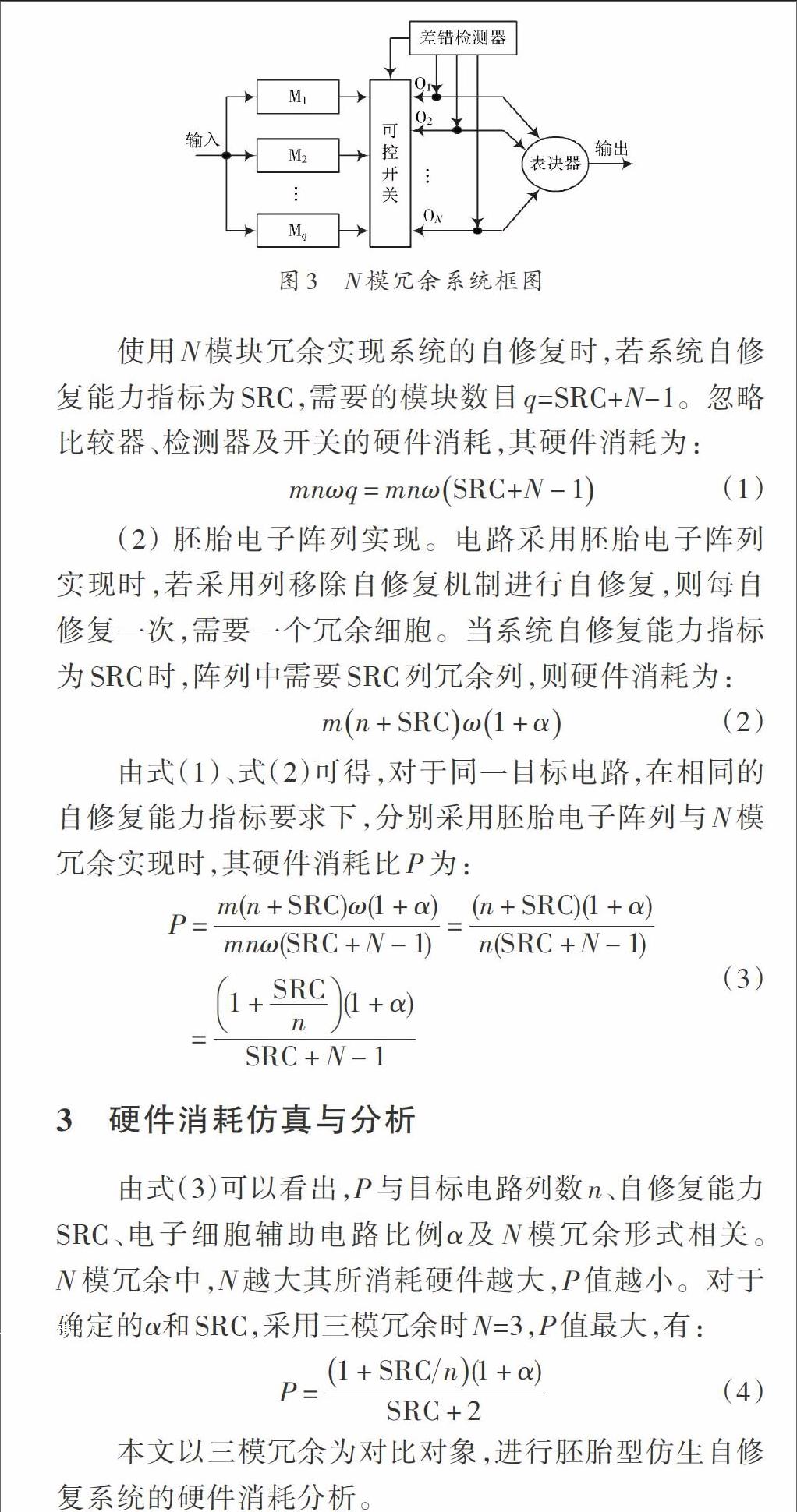

(1) N模冗余實現(xiàn)。電路采用N模冗余實現(xiàn)時,q個完全相同的模塊M1,M2,…,Mq通過可控開關(guān)選擇N個模塊工作,工作模塊的輸出O1,O2,…,ON通過差錯檢測器檢測模塊狀態(tài),并使用表決器確定系統(tǒng)的輸出,其結(jié)構(gòu)如圖3所示。當(dāng)檢查到N個工作模塊中存在故障模塊時,可控開關(guān)將故障模塊斷開,使故障模塊不影響電路的最終輸出,并選擇冗余模塊進行工作,保證同時有N個正常模塊工作。

使用N模塊冗余實現(xiàn)系統(tǒng)的自修復(fù)時,若系統(tǒng)自修復(fù)能力指標(biāo)為SRC,需要的模塊數(shù)目q=SRC+N-1。忽略比較器、檢測器及開關(guān)的硬件消耗,其硬件消耗為:

[mnωq=mnωSRC+N-1] (1)

(2) 胚胎電子陣列實現(xiàn)。電路采用胚胎電子陣列實現(xiàn)時,若采用列移除自修復(fù)機制進行自修復(fù),則每自修復(fù)一次,需要一個冗余細胞。當(dāng)系統(tǒng)自修復(fù)能力指標(biāo)為SRC時,陣列中需要SRC列冗余列,則硬件消耗為:

[mn+SRCω1+α] (2)

由式(1)、式(2)可得,對于同一目標(biāo)電路,在相同的自修復(fù)能力指標(biāo)要求下,分別采用胚胎電子陣列與N模冗余實現(xiàn)時,其硬件消耗比P為:

[P=m(n+SRC)ω(1+α)mnω(SRC+N-1)=(n+SRC)(1+α)n(SRC+N-1) =1+SRCn(1+α)SRC+N-1] (3)

3 硬件消耗仿真與分析

由式(3)可以看出,P與目標(biāo)電路列數(shù)n、自修復(fù)能力SRC、電子細胞輔助電路比例α及N模冗余形式相關(guān)。N模冗余中,N越大其所消耗硬件越大,P值越小。對于確定的α和SRC,采用三模冗余時N=3,P值最大,有:

[P=1+SRCn(1+α)SRC+2] (4)

本文以三模冗余為對比對象,進行胚胎型仿生自修復(fù)系統(tǒng)的硬件消耗分析。

3.1 固定輔助電路比的硬件消耗

當(dāng)目標(biāo)電路列數(shù)n在[10,100]上、自修復(fù)能力SRC在[1,20]上變化,電子細胞輔助電路比例α分別為0.2,1.0,2.0,3.0,4.0,5.0時,P隨n和SRC的變化如圖4所示。由圖4可以看出,胚胎電子陣列與N模冗余實現(xiàn)同一目標(biāo)電路時,硬件消耗比P隨著電子細胞輔助電路比例α的增加而增加,隨著目標(biāo)電路列數(shù)n和自修復(fù)能力SRC的增加而降低。在相同的電子細胞設(shè)計水平下,目標(biāo)電路規(guī)模越大、自修復(fù)能力越大,P值越小,胚胎電子陣列的優(yōu)勢越明顯,這是由于胚胎電子陣列與N模冗余的自修復(fù)特點不同決定的。N模冗余中將故障模塊整塊移除,而胚胎電子陣列中只移除故障細胞所在列,因此胚胎電子陣列在大規(guī)模、大自修復(fù)能力要求的環(huán)境下優(yōu)勢更加突出。對于相同規(guī)模和自修復(fù)能力要求的目標(biāo)電路,α越大,P值越大,且對規(guī)模較小、自修復(fù)能力要求較低的電路影響較大。當(dāng)[α≥2.0]時,對于規(guī)模[n≤20]、自修復(fù)能力[SRC≤5]的目標(biāo)電路有[P≥1.0],此時,胚胎電子陣列的硬件消耗大于三模冗余的硬件消耗。但是對于規(guī)模[n≥20]、自修復(fù)能力[SRC≥10]的目標(biāo)電路,即使[α=5.0],即電子細胞中輔助電路是細胞功能電路的5倍,P值依然小于1,即胚胎電子陣列與三模冗余相比依然具有優(yōu)勢。

3.2 固定電路規(guī)模的硬件消耗

為了進一步研究電子細胞輔助電路比例α對P的影響,當(dāng)α在[1,20]上、自修復(fù)能力SRC在[1,20]上變化,目標(biāo)電路列數(shù)n分別為10,20,30,50,100,200時計算胚胎電子陣列和三模冗余消耗硬件比例P,計算結(jié)果如圖5所示,圖5中黑色線條為[P=1.0]對應(yīng)位置。

由圖5可以看出,在相同的輔助電路比α和電路自修復(fù)能力SRC要求下,目標(biāo)電路規(guī)模n越大,P值越小。同時,n越大,使[P<1.0]的α和SRC取值范圍越大。當(dāng)[n=200]時,即使輔助電路比[α=20],即電子細胞中檢測、基因存儲、修復(fù)控制電路規(guī)模是邏輯功能規(guī)模的20倍,對于自修復(fù)能力[SRC>20]的應(yīng)用場合,胚胎電子陣列實現(xiàn)依然有硬件優(yōu)勢。

當(dāng)目標(biāo)電路規(guī)模較小時,如[n=10],使[P<1.0]的α和SRC取值范圍較小。此時若[α>5],即電子細胞中檢測、基因存儲、修復(fù)控制電路規(guī)模是邏輯功能規(guī)模的5倍,則胚胎電子陣列相對于三模冗余沒有硬件優(yōu)勢。

通過對圖4和圖5的分析可知,對于大規(guī)模、自修復(fù)能力要求高的目標(biāo)電路,使用胚胎電子陣列實現(xiàn)時更具有優(yōu)勢。同時,電子細胞中檢測、基因存儲、修復(fù)控制等輔助電路的設(shè)計影響胚胎電子陣列的硬件消耗和應(yīng)用范圍,輔助電路比越低,胚胎電子陣列可應(yīng)用范圍越大。在胚胎電子陣列設(shè)計過程中,應(yīng)盡量優(yōu)化電子細胞設(shè)計,降低輔助電路比。

4 結(jié) 語

根據(jù)胚胎型仿生自修復(fù)系統(tǒng)中基本單元——電子細胞的結(jié)構(gòu)特點,并結(jié)合其列移除自修復(fù)機制,建立了系統(tǒng)硬件消耗模型。在該模型基礎(chǔ)上,對基于胚胎型仿生自修復(fù)系統(tǒng)的電路硬件消耗進行了分析。分析表明胚胎型仿生自修復(fù)系統(tǒng)適用于大規(guī)模目標(biāo)電路、可靠性要求高的應(yīng)用環(huán)境。對于目標(biāo)電路規(guī)模較小、自修復(fù)能力要求較低的應(yīng)用,胚胎型仿生自修復(fù)系統(tǒng)與傳統(tǒng)的三模冗余相比,在硬件消耗上沒有優(yōu)勢。另外,仿生電子系統(tǒng)的硬件消耗與電子細胞的設(shè)計水平緊密相關(guān),通過優(yōu)化電子細胞設(shè)計,可以有效降低系統(tǒng)硬件消耗。

參考文獻

[1] DE GARIS H. Genetic programming: artificial nervous systems, artificial embryos and embryological electronics [C]// Proceedings of the 1st Workshop on Parallel Problem Solving from Nature. London: Springer, 1990: 117?123.

[2] DE GARIS H. Artificial embryology: the genetic programming of an artificial embryo [M]. New York: Wiley, 1992: 373?393.

[3] MANGE D, SANCHEZ E, STAUFFER A, et al. Embryonics: a new methodology for designing field?programmable gate arrays with self?repair and self?replicating properties [J]. IEEE transactions on very large scale integration (VLSI) systems, 1998, 6(3): 387?399.

[4] THOMA Y, TEMPESTI G, SANCHEZ E, et al. POEtic: an electronic tissue for bio?inspired cellular applications [J]. Biosystems, 2004, 76(1): 191?200.

[5] BREMNER P, LIU Y, SAMIE M, et al. SABRE: a bio?inspired fault?tolerant electronic architecture [J]. Bioinspiration & biomimetics, 2013, 8(1): 1?17.

[6] 張砦,王友仁.基于可靠性分析的胚胎硬件容錯策略選擇方法[J].系統(tǒng)工程理論與實踐,2013,33(1):236?242.

[7] ZHU S, CAI J Y, MENG Y F. A novel embryonics system with evolutionary ability [J]. WSEAS transactions on circuits and systems, 2015, 14: 164?173.

[8] 朱賽,蔡金燕,孟亞峰,等.用于胚胎電子陣列的實驗系統(tǒng)[J].電光與控制,2015,22(4):70?74.

[9] YANG I, JUNG S H, CHO K H. Self?repairing digital system with unified recovery process inspired by endocrine cellular communication [J]. IEEE transactions on very large scale integration (VLSI) systems, 2013, 21(6): 1027?1040.

[10] 李岳,王南天,錢彥嶺.原核細胞仿生自修復(fù)電路設(shè)計[J].國防科技大學(xué)學(xué)報,2012,34(3):154?157.

[11] 徐佳慶,竇勇,呂啟,等.電子組織:一種具有自適應(yīng)能力的可重構(gòu)仿生硬件結(jié)構(gòu)[J].計算機研究與發(fā)展,2012,49(9):2005?2017.

[12] 郝國鋒,王友仁,張砦.可重構(gòu)硬件芯片級故障定位與自主修復(fù)方法[J].電子學(xué)報,2012,40(2):384?388.

[13] ZHU S, CAI J Y, MENG Y F, et al. A novel embryonics electronic cell array structure [J]. WSEAS transactions on circuits and systems, 2014, 13: 224?232.