Simulink環(huán)境下的SAR ADC行為建模與仿真分析

韓笑 孫玲 吳秀山

摘 要: 逐次逼近型模/數(shù)轉(zhuǎn)換器由于電路復(fù)雜度較低,且功耗和速度等性能可以隨著集成電路工藝的進(jìn)步而不斷提升,在高速、高精度ADC設(shè)計中被廣泛應(yīng)用。借助Matlab軟件環(huán)境下的Simulink工具,該文以14位SAR ADC為例給出了電路的行為級建模方法,分析了SAR ADC采樣頻率、輸入信號頻率以及內(nèi)部時鐘之間的關(guān)系,充分討論了Simulink下各模塊的具體實現(xiàn)并給出了仿真結(jié)果。該分析為SAR ADC的晶體管極電路設(shè)計與實現(xiàn)提供了重要參考依據(jù)。

關(guān)鍵詞: 模/數(shù)轉(zhuǎn)換器; 逐次逼近型結(jié)構(gòu); 行為級建模; Simulink

中圖分類號: TN911?34; TN492 文獻(xiàn)標(biāo)識碼: A 文章編號: 1004?373X(2017)06?0136?04

Abstract: The analog?to?digital converter (ADC) of the successive approximation register (SAR) has been widely used in the design of the high?speed and high?precision ADC because its circuit complexity is low, and its performances such as power dissipation and speed can be constantly improved with the improvement of the integrated circuit technique. By virtue of the Simulink tool under Matlab software environment, the 14?bit SAR ADC is taken as an example to give the behavior modeling method of the circuit, and the relationship among the sampling frequency, input signal frequency and internal clock of SAR ADC is analyzed. Each module implemented with Simulink is discussed, and the simulation results are given. The simulation analysis provides an important reference for the design and implementation of the transistor circuit of SAR ADC.

Keywords: ADC; successive approximation register; behavioral modeling; Simulink

近年來電子技術(shù)發(fā)展迅猛,隨處可見的電子產(chǎn)品不僅使人們的日常生活變得更加便捷,還豐富了人們的娛樂生活。模/數(shù)轉(zhuǎn)換器(Analog?to?Digital Converter,ADC)作為連接數(shù)字世界和模擬世界的橋梁,是現(xiàn)代電子信息系統(tǒng)中必不可少的一個重要電路單元[1?2]。目前常用的ADC有全并行結(jié)構(gòu)(FLASH)、分級型結(jié)構(gòu)(Subranging)、流水線結(jié)構(gòu)(Pipeline)、折疊插值型結(jié)構(gòu)(Folding and Interpolating)、∑?Δ型結(jié)構(gòu)和逐次逼近型結(jié)構(gòu)(SAR: Successive Approximation Register)等實現(xiàn)方式[3?4]。其中,SAR ADC由于電路復(fù)雜度較低,且功耗和速度等性能隨著集成電路工藝的進(jìn)步而不斷提升,在高速、高精度ADC設(shè)計中被廣泛應(yīng)用[5?8]。

盡管SAR ADC的電路結(jié)構(gòu)相對簡單,但卻有多種不同的晶體管級實現(xiàn)方法[9?10]。深刻掌握該電路的工作原理,及其采用、量化以及編碼這一工作流程,對晶體管級的實現(xiàn)將起到事半功倍的作用。本文借助Matlab軟件環(huán)境下的Simulink工具完成了一個14位SAR ADC的行為級建模,在分析SAR ADC采樣頻率、輸入信號頻率以及內(nèi)部時鐘之間關(guān)系的基礎(chǔ)上詳細(xì)仿真分析了電路的工作原理和各模塊間的工作流程,具體介紹如下。

1 SAR ADC工作原理分析與建模

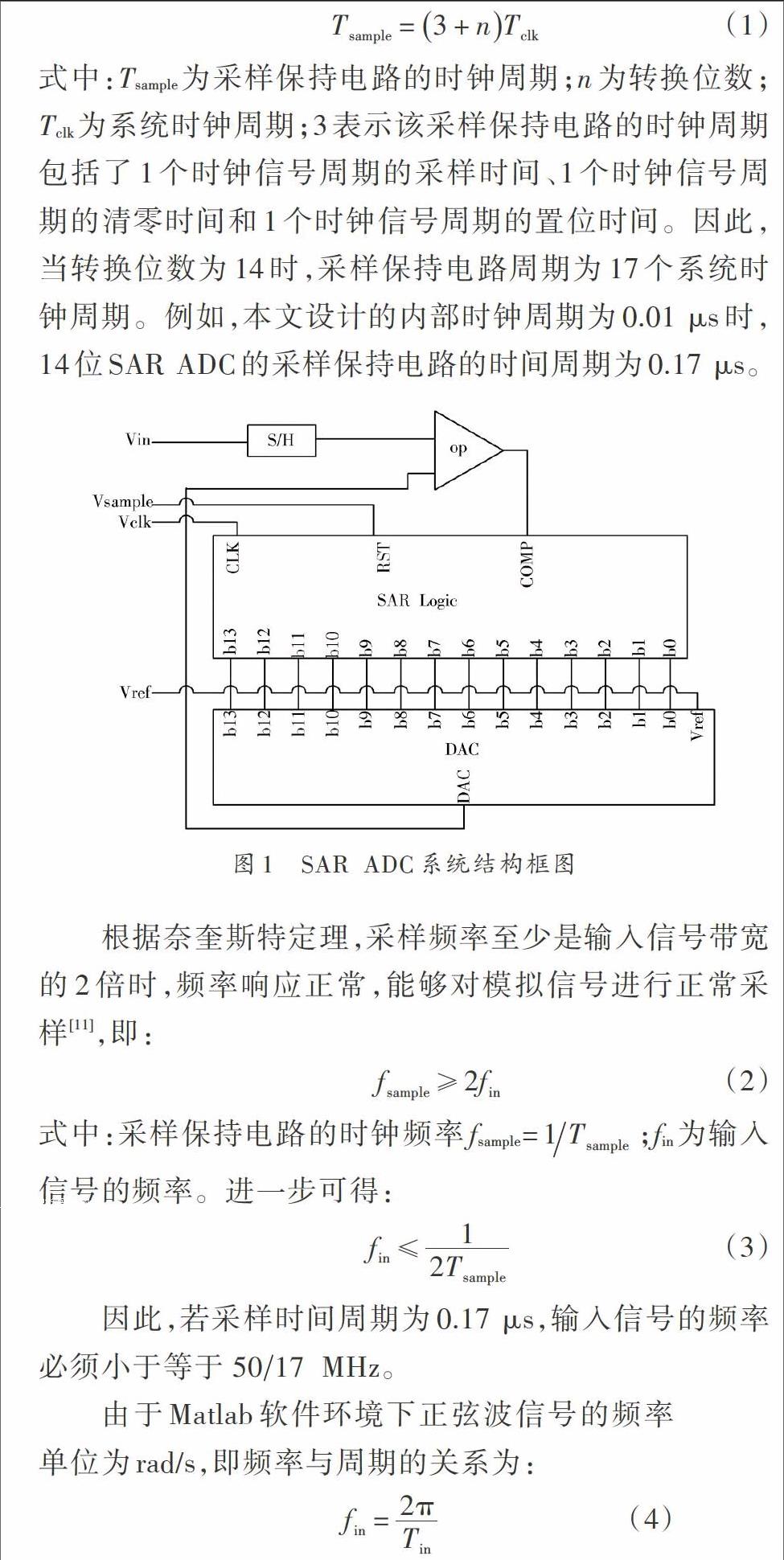

本文設(shè)計的14位SAR ADC系統(tǒng)結(jié)構(gòu)如圖1所示,它主要包括采樣保持電路(Sample and Hold)、比較器電路(Operator)、逐次逼近寄存器(SAR Logic)以及數(shù)/模轉(zhuǎn)換電路(DAC)四個單元模塊。下面分別給出各模塊的分析與設(shè)計實現(xiàn)。

1.1 采樣保持電路

采樣保持電路是整個SAR ADC電路轉(zhuǎn)換的起始點,其作用是采集當(dāng)前時刻模擬信號的電壓值,并使該電壓值保持一定時間以供后續(xù)電路進(jìn)行量化處理。考慮到從該電壓值的采集到量化過程結(jié)束所需的時間,并結(jié)合后續(xù)移位寄存器的清零和置位要求,本文將采樣保持電路時鐘周期與系統(tǒng)時鐘周期的關(guān)系設(shè)置為:

1.2 比較器電路

比較器電路用來比較采樣保持電路輸出電壓與DAC電路輸出電壓,當(dāng)采樣保持電路輸出電壓大于DAC電路輸出電壓時,比較器輸出為高電平;當(dāng)采樣保持電路輸出電壓小于等于DAC電路輸出電壓時,比較器輸出為低電平。

1.3 逐次逼近寄存器

1.3.1 D觸發(fā)器設(shè)計

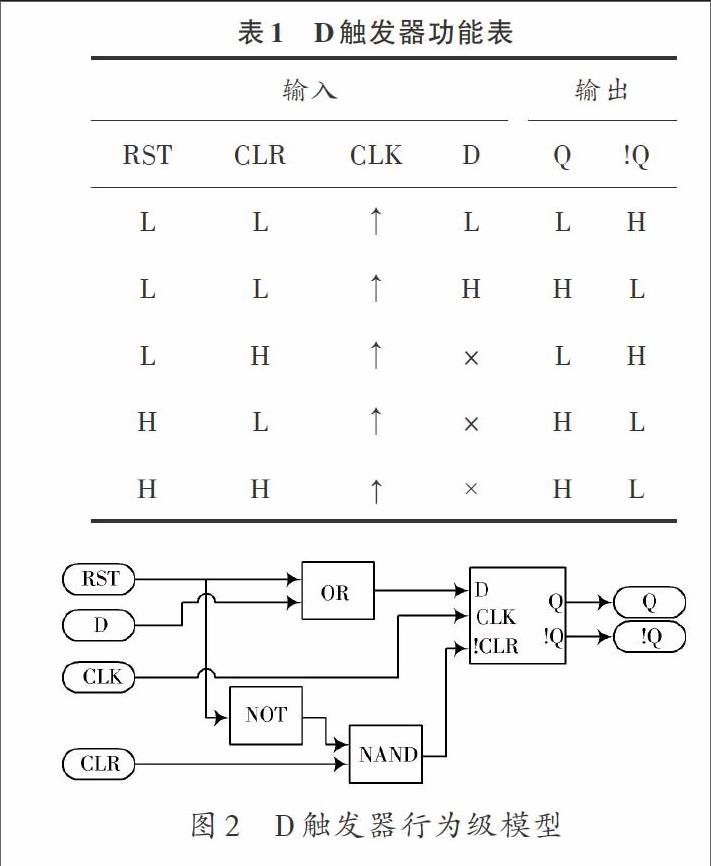

逐次逼近寄存器主要由D觸發(fā)器構(gòu)成。由于Simulink工具自帶的D觸發(fā)器僅有清零功能,而逐次逼近寄存器還需要有復(fù)位功能以使得一次采用過程結(jié)束后能夠為下一次采用過程做好準(zhǔn)備。為了使D觸發(fā)器具有如表1所示的功能,本文設(shè)計了如圖2所示的帶有清零和置位功能的D觸發(fā)器行為級模型,圖2中的清零端和置位端都為高電平有效。當(dāng)置位端為高電平時,輸出為1;當(dāng)置位端為低電平,清零端為高電平時,輸出為0。

1.3.2 寄存器設(shè)計

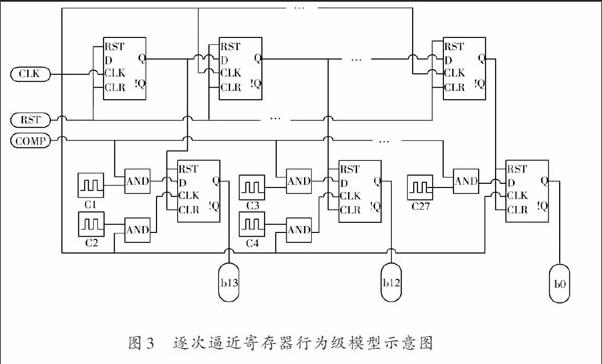

圖3給出了本文設(shè)計的逐次逼近寄存器行為級模型的結(jié)構(gòu)示意圖。圖3主要分為上下兩部分,上半部分由14個如圖2所示的D觸發(fā)器構(gòu)成,用來在時鐘周期下將信號1從最高位移至最低位;下半部分也是由14個D觸發(fā)器構(gòu)成,用以讀取來自比較器的輸出信號COMP。表2為整個寄存器工作的轉(zhuǎn)換流程。

由表2可見,本文設(shè)計的寄存器工作流程為:第1個時鐘周期下,圖3中上半部分左邊第1個觸發(fā)器置位;第2個時鐘周期下,圖3中下半部分所有觸發(fā)器清零;第3個時鐘周期下,圖3下半部分左邊第1個觸發(fā)器開始置位;第4個時鐘周期開始寄存器輸出COMP結(jié)果并保持到采用過程結(jié)束。

由于寄存器的每個輸出端對應(yīng)的保持時間不同,因此,本文在圖3下半部分所有觸發(fā)器的CLK端和D端設(shè)計了專門的電路。以下半部分左邊第1個觸發(fā)器為例,由于該觸發(fā)器僅需要前兩個系統(tǒng)時鐘周期完成清零,隨后的兩個系統(tǒng)時鐘周期完成比較輸出,之后的13個系統(tǒng)時鐘周期內(nèi)始終保持輸出不變,所以設(shè)計中增加了C1信號和C2信號。其中,C1信號在觸發(fā)器完成比較輸出所對應(yīng)的兩個系統(tǒng)時鐘周期內(nèi)為高電平,即第3和第4個系統(tǒng)時鐘周期內(nèi)為高電平,其余時刻為低電平;C2信號在前4個系統(tǒng)時鐘周期內(nèi)為高電平,其余時刻為低電平。同理,圖3中的C3信號在第4和第5個系統(tǒng)時鐘周期內(nèi)為高電平,其余時刻為低電平;C4信號在前5個系統(tǒng)時鐘周期內(nèi)為高電平,其余時刻為低電平。以此類推直到最后一個D觸發(fā)器。

1.4 DAC電路設(shè)計

DAC電路的主要功能是將數(shù)字信號轉(zhuǎn)化為模擬信號,圖4為設(shè)計的DAC電路行為級模型,主要由14個乘法器和一個加法器構(gòu)成,其輸出模擬電壓值與輸入數(shù)字信號的關(guān)系為:

[vo=Vref214i=013Di?2i] (5)

式中:Vref為參考電壓值,本例中該參考電壓設(shè)置為2 V;Di為輸入的14位數(shù)字量。

2 行為級仿真分析

本設(shè)計中采用正弦波信號作為SAR ADC的輸入信號,該輸入信號的周期設(shè)置為3.4 μs,采樣保持電路周期為0.17 μs,仿真時間設(shè)為4 μs,使用示波器模塊scope來觀測Simulink下的行為級仿真波形。圖5為仿真時間內(nèi)采樣保持電路的輸出波形,相應(yīng)時間下DAC電路的輸出波形如圖6所示。

選取采樣保持電路輸出為1 V時,放大對應(yīng)的DAC電路輸出波形,得到如圖7所示結(jié)果。此時,逐次逼近寄存器14位數(shù)字輸出結(jié)果為10 000 000 000 000,即1 V輸入電壓對應(yīng)的輸出數(shù)字量。

3 結(jié) 語

由于SAR ADC在精度、速度、功耗和成本等方面的綜合優(yōu)勢,使得其仍然是工業(yè)界與學(xué)術(shù)界在實現(xiàn)高速、高精度ADC時可選的主流結(jié)構(gòu)之一。本文以14位SAR ADC為例,介紹了Simulink工具下SAR ADC的行為級建模方法,詳細(xì)討論了各單元模塊的設(shè)計實現(xiàn),分析了輸入輸出信號間的關(guān)系,給出了仿真結(jié)果。為深刻學(xué)習(xí)掌握SAR ADC的工作原理,全面了解各模塊間的相互關(guān)系,為后續(xù)更好地進(jìn)行SAR ADC的晶體管設(shè)計奠定了堅實的基礎(chǔ)。

注:本文通訊作者為孫玲。

參考文獻(xiàn)

[1] 王祁鈺.8位納米級高速SAR A/D轉(zhuǎn)換器設(shè)計[D].西安:西安電子科技大學(xué),2014.

[2] 楊明,趙毅強(qiáng),夏璠.基于混合編碼DAC的低功耗SAR ADC設(shè)計[J].微電子學(xué)與計算機(jī),2013,30(7):92?94.

[3] 居水榮,魏天堯,朱樟明.超低功耗逐次逼近寄存器型模數(shù)轉(zhuǎn)換器的設(shè)計[J].半導(dǎo)體集成電路,2015,40(3):174?180.

[4] 李現(xiàn)坤,張瑛,郭宇鋒,等.一種10 bit MS/s SAR ADC的設(shè)計實現(xiàn)[J].計算機(jī)技術(shù)與發(fā)展,2014,24(8):211?214.

[5] SONG Yan, XUE Zhongming, YAN Pengcheng, et al. A 0.6?V 8.3?ENOB asynchronous SAR ADC for biomedical applications [J]. Journal of semiconductors, 2014, 35(8): 158?164.

[6] WANG Ya, XUE Chunying, LI Fule, et al. A low power 11?bit 100 MS/s SAR ADC IP [J]. Journal of semiconductors, 2015, 36(2): 1?5.

[7] 萬鑫,談熙.一種非二進(jìn)制權(quán)重的高能效比逐次比較型模數(shù)轉(zhuǎn)換器[J].固體電子學(xué)研究與進(jìn)展,2013,33(4):383?388.

[8] WONG S S, CHIO U F, ZHU Y, et al. A 2.3 mW 10?bit 170 MS/s two?step binary?search assisted time?interleaved SAR ADC [J]. IEEE journal of solid?state circuits, 2013, 48(8): 1783?1794.

[9] 李文石.可編程采樣率的超低功耗逐次逼近型模數(shù)轉(zhuǎn)換器的設(shè)計[D].蘇州:蘇州大學(xué),2013.

[10] 黃玲.一種12位1 MSps全差分SAR ADC的研究與設(shè)計[D].北京:北方工業(yè)大學(xué),2014.

[11] 李慶山.一種帶數(shù)字校準(zhǔn)電路的10位SAR ADC設(shè)計[D].長沙:湖南大學(xué),2013.