基于CPLD實現FPGA的SPI Flash配置

曹鵬飛

摘要:FPGA在電子通信領域是一種用途廣泛的可編程邏輯器件,能否選擇合適的程序配置方式是一個重要的問題,關系到FPGA上電后能否快速可靠地進入到工作狀態。通過設置FPGA為從串配置模式,利用SPI Flash芯片作為外置存儲器,CPLD作為程序加載控制器可以對FPGA進行可靠配置。實踐證明,這種配置方式操作方便,可實施性強,具有一定的參考價值。

關鍵詞:FPGA CPLD SPI Flash 配置

中圖分類號:TP206.1 文獻標識碼:A 文章編號:1007-9416(2016)12-0092-02

1 引言

現場可編程門陣列(FPGA)技術在當前許多領域都得到了大規模的廣泛應用,包括通信、網絡、工業、醫療、汽車等各個領域都發揮了重要作用,滿足了對電子產品高性能、高可靠性和高靈活性的要求。

FPGA基于芯片內部的SRAM技術完成其邏輯功能,并具有可重復編程的特點,但是SRAM存在易失性,掉電則數據丟失,因此需要將配置程序存入外部存儲芯片中,上電進入對應的管理模式即可進行程序加載。FPGA的程序配置有多種選擇方式,既可以選擇FPGA公司提供的配置芯片,也可以選擇通用存儲芯片,還可以選擇在線配置模式。而選用通用存儲芯片在性價比方面具有一定的優勢,通過CPLD進行數據讀寫控制操作,即可實現對FPGA的程序配置,操作簡單靈活。

2 配置原理

按照數據接口進行劃分,FPGA的配置模式可以分為并行模式和串行模式。按照是否由FPGA提供時鐘源又可以分為主模式和從模式,由FPGA提供配置時鐘CCLK信號的模式稱為為主模式,反之由外部器件給FPGA提供配置時鐘的模式稱為從模式。因此配置模式主要包括主并、主串、從并、從串以及JTAG配置方式。具體模式由FPGA模式管腳M2、M1、M0設定。外部SPI Flash芯片是一種串行芯片,CPLD作為主控制器,選擇從串配置模式。M(2:0)信號設為“111”。

FPGA選用Xilinx公司的Virtex 6芯片XC6VLX130T。Virtex 6系列芯片采用40nm工藝制造,是一種高性能的現場可編程門陣列。Virtex 6 FPGA系列包括高性能邏輯、高性能DSP以及高速串行收發器三個面向應用領域而優化的FPGA平臺,分別提供了不同的功能和特性組合來滿足不同客戶應用的需求。

CPLD芯片選用的是Xilinx公司的CoolRunner-Ⅱ系列的XC2A64A。具有高性能、低功耗的特點,并且具有封裝尺寸小的特點,可以有效節約電路板的布局面積。

SPI FLASH存儲芯片選擇的是意法半導體的M25P128,存儲容量為128M比特。SPI接口最大傳輸速率為50Mhz。M25P128具有多種操作指令。

CPLD執行對SPI Flash芯片的讀操作時,操作指令為0x03。當開始讀取數據時,首先將片選信號CS由高電平拉為低電平,SPI Flash芯片在數據輸入管腳(D)讀取讀操作指令,然后讀取3字節的存儲單元的首地址。隨后SPI Flash芯片在數據輸出管腳(O)輸出該地址的存儲數據字節。讀取地址自動加1,再跳至下一地址,存儲字節可以依次輸出到數據輸出管腳(O)。該Flash芯片為128Mbit,最大存儲單元為16777216字節。當到達最高地址時,地址計數器清零。在此期間CS信號一直保持低電平。一旦CS信號重新拉高,即可中止對數據的讀取操作。

SPI Flash芯片內部按頁分塊進行地址空間的劃分,可以存儲多個FPGA的配置文件。當需要配置FPGA時,CPLD根據配置文件的具體保存地址進行數據的讀取操作,從而可以實現在不同功能要求下的不同FPGA文件的動態可重配置,具有一定的靈活性。

3 功能實現

FPGA配置系統平臺主要由3部分組成:FPGA芯片、CPLD芯片和SPI Flash芯片。由CPLD提供配置參考時鐘CCLK給FPGA,同時提供SPI工作時鐘給SPI Flash芯片。

FPGA配置電路圖如圖1所示。

接口信號功能說明如下:

MSCK: SPI工作時鐘。

CS: 配置芯片選擇信號,低電平有效。

MOSI: Flash數據信號串行輸入。

MISO: Flash數據信號串行輸出。

CCLK: FPGA配置時鐘,和SPI工作時鐘反相。

PROG: 低電平FPGA異步復位信號,從低電平重新拉高后才可以進行編程。

INIT: FPGA初始化完成信號,當為低電平時,FPGA清除配置寄存器。當FPGA采集配置模式信號M2、M1、M0狀態完成后,由低電平變為高電平。

DONE: FPGA配置完成信號。

CPLD按照不同功能主要包括3個模塊:信號檢測模塊,計數器模塊,SPI信號產生模塊。

信號檢測模塊完成對PROG、INIT、DONE等信號的檢測判斷。

計數器模塊完成符合SPI時序要求的計數以及復位計數器等計數器的計數。

SPI信號產生模塊主要完成符合SPI時序要求的CS、MOSI、MISO等信號的輸出。

CPLD上電后可以實現對FPGA的重復配置。CPLD完成對FPGA的配置操作是通過對SPI Flash的讀操作和對FPGA的寫操作兩個過程來實現的。FPGA在沒有完成編程之前,INIT和DONE信號為低電平,PROG信號為高電平。

CPLD在兩種條件下選擇是否對FPGA進行程序配置。首先,當電路板上電時,CPLD即進入FPGA程序加載編程模式。其次,CPLD對來自上位機或電路板CPU的FPGA程序加載使能信號進行判斷,使能信號為脈沖信號,脈寬為一個SPI工作時鐘周期,高電平有效。判斷信號有效時則進入程序加載編程模式。

FPGA選用V6芯片,而V6芯片是多電源供電,在FPGA各路電源按照上電順序供電正常后,電源管理模塊輸出給CPLD一個power-complete高電平信號,才可以對FPGA進行程序配置。

在電路板上電后,CPLD檢測power-complete信號和加載使能信號,一旦信號有效,CPLD內部的的4位PROG計數器開始計數,產生一個不小于250us的PROG低電平信號,然后PROG信號重新拉高。

CPLD開始檢測FPGA的INIT信號,在PROG信號由低電平變為高電平最多5ms 的時間之內,INIT信號應該由低電平變為高電平,CPLD可以開始對Flash芯片的讀操作,否則進入無效狀態。

Flash芯片的存儲容量為128Mbit,即16M字節。數據讀寫計數器包括3位計數器mcnt(2:0)和24位計數器mcnt1(23:0)。mcnt1(23:0)最大計數值為0xFFFFFF,一旦計滿停止計數,除非計數器重新復位。

CPLD產生CS信號和MOSI輸出信號,一旦進入Flash讀操作模式,CS信號電平即拉低為低電平。MOSI信號首先輸出1個字節的操作指令,由于是對FLASH的讀操作,因此輸出指令為0x03,然后輸出3個字節的地址。由于程序是從Flash芯片的第0字節開始寫入,因此讀取的初始地址設為0X000000。Flash芯片在收到正確的指令后,從第5個字節周期開始,FLASH芯片的MISO管腳開始輸出配置文件的數據,并同時送給FPGA芯片和CPLD芯片。FPGA開始執行配置數據的寫操作,接收MCS配置文件碼流。

同時CPLD芯片開始檢測FPGA的DONE信號,一旦檢測到DONE信號為高電平,說明配置碼流傳輸正常結束,CS信號需要重新拉高,表示FPGA配置完成。

利用VHDL語言編寫代碼,完成CPLD的邏輯電路設計。

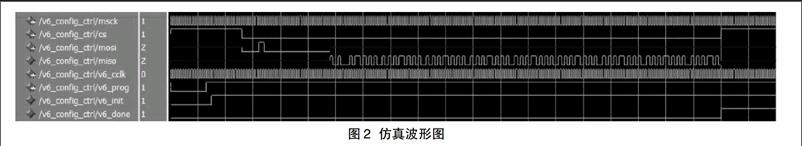

在仿真軟件里得到的仿真波形圖如圖2所示。

4 功能驗證

為了對本文設計的FPGA配置系統進行驗證,按照圖1設計了系統驗證平臺。SPI Flash芯片通過配置接口寫入FPGA配置程序MCS文件,然后由CPLD進行數據讀取,再寫入到FPGA XC6VLX130T芯片進行程序配置。經過驗證,CPLD可以成功實現FPGA的配置。

5 結語

本文提供了一種通過CPLD配置FPGA的方法,對于其它類似的FPGA和SPI Flash芯片的配置,可以進行同樣的電路和程序設計,具有一定的參考價值。

參考文獻

[1]候伯亨,劉凱,顧新.VHDL硬件描述語言與數字邏輯電路設計(第四版)[M].西安電子大學出版社,2014.

[2]何賓.EDA原理及VHDL實現[M].清華大學出版社,2011.

[3]李春雨,夏敏磊.基于CPLD的SPI Flash程序在線加載方案[J].自動化與儀器儀表,2015.

[4]陸禮紅,尹煥亭.基于CPLD 技術的FPGA 快速加載方案研究[J].電子技術與軟件工程,2015.

[5]Xilinx.Virtex-6 FPGA Configuration User Guide UG360 (v3.9) [R] November 18,2015.