雙核SoC芯片掃描鏈測試設計與實現

劉廣東,石國帥,徐浩然

(北京計算機技術及應用研究所,北京 100854)

雙核SoC芯片掃描鏈測試設計與實現

劉廣東,石國帥,徐浩然

(北京計算機技術及應用研究所,北京 100854)

針對芯片生產過程中可能引入短路和斷路等制造缺陷的問題,實現了基于掃描鏈測試的雙核SoC芯片可測性設計電路;根據雙核SoC中DSP硬核、CPU軟核特點采用不同的掃描鏈設計方案:利用DSP硬核中已有掃描鏈結構,將DSP測試端口復用到芯片頂層端口,在CPU軟核和其它硬件邏輯中插入新的掃描鏈電路;掃描鏈測試支持固定型故障測試和時延相關故障測試;針對時延故障測試,設計了片上時鐘控制電路,利用PLL輸出高速時鐘脈沖進行實速測試;采用自動測試向量生成工具產生測試向量,結果表明,芯片固定型故障的測試覆蓋率可以達到97.6%,時延故障測試覆蓋率可以達到84.9%,滿足芯片測試覆蓋率要求。

可測性設計;掃描鏈測試;雙核;片上時鐘控制

0 引言

在芯片制造過程中,各種隨機因素及生產線自身缺陷都可能導致芯片制造故障,使芯片不能正常工作,故需要對生產出的芯片進行測試[1]。單個芯片上可以集成多個處理器核,內部IP越來越多,其時序結構也更加復雜,對芯片的測試難度大大增加。為了達到測試目標,必須采用可測性設計(DFT)技術,通過增加測試邏輯和測試引腳,解決芯片的有效和自動測試問題。可測性設計技術主要包括掃描鏈測試(Scan),存儲器內建自測試(MBIST)和邊界掃描測試(BSD)等[2]。可測性設計關系到芯片的測試成本及良率,需要以較短的測試時間和較低的測試成本來獲得較高的測試覆蓋率和測試質量[3]。在0.13 μm工藝和以下,與時序相關故障所占比例越來越大,而通常由測試機提供慢速時鐘的測試無法覆蓋時序相關的故障,由于這些原因,實速(at-speed)測試已成為一種必需的測試手段。

1 掃描鏈測試的基本原理

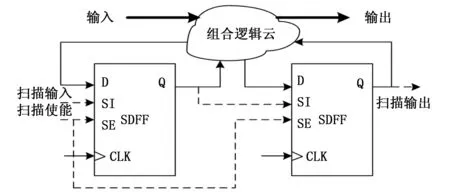

SoC芯片為一個大規模的時序電路,其電路可以通過組合網絡和觸發器的反饋建模,如圖1所示。這些觸發器的值代表電路的狀態,但由于很難控制或觀測觸發器值,故難以直接對時序電路產生測試向量。掃描鏈測試技術就是把普通觸發器修改為掃描觸發器,并通過掃描輸入端口將觸發器串聯成掃描鏈。根據是否將所有觸發器替換成掃描觸發器,掃描設計分為“全掃描設計”和“部分掃描設計”。掃描鏈測試向量通過掃描鏈測試輸入管腳輸入,對掃描觸發器值進行控制,掃描測試結果通過芯片掃描輸出管腳輸出,可以觀測掃描測試結果。通過掃描移位,掃描觸發器值既是測試數據的輸入,又可以作為測試響應的輸出。掃描鏈測試分為掃描移位階段、捕獲階段和掃描輸出階段,掃描移位階段是將測試向量通過掃描觸發器串行地輸入掃描鏈,捕獲階段是通過觸發器捕獲組合邏輯輸出的狀態,掃描輸出階段是將捕獲的組合邏輯輸出值通過掃描鏈輸出,通過比較掃描鏈輸出與期望結果判斷芯片內部是否出現故障。

圖1 時序電路模型圖

掃描鏈測試分為基于固定型故障的測試(stuck-at測試)和基于時延故障的測試(實速測試),兩者的區別僅在于捕獲階段不同,stuck-at測試捕獲階段使用的時鐘為慢速的掃描移位時鐘,時鐘頻率通常為數十MHz,只需要一個時鐘脈沖,而實速測試捕獲階段使用高速功能時鐘脈沖,通常為數百兆赫茲甚至數吉赫茲,捕獲階段需要2個及以上捕獲時鐘脈沖。

2 掃描鏈設計方案

異構雙核SoC芯片是一款系統級超大規模集成電路,芯片架構框圖如圖2所示。SoC芯片內部集成了CPU軟核,DSP硬核、存儲器、總線系統、數據處理和通信模塊及多種IO接口,各模塊通過片內互聯總線通信。由于SoC芯片內部模塊的類型及來源多種多樣,需要采用不同的可測性設計方法。SoC芯片需采用的DFT測試方法包括:掃描鏈測試[5]、存儲器內建自測試和邊界掃描測試[6],本文主要針對掃描鏈測試進行研究。

圖2 異構雙核SoC架構框圖

綜合生成網表后即需要進行掃描鏈測試插入掃描鏈設計,由于雙核SoC中的DSP采用的是硬核設計,硬核內部已經插入掃描鏈結構,掃描測試的端口也已經引出到硬核端口上,故不需要對DSP硬核進行專門的插掃描鏈設計,只需要將硬核的掃描端口通過pad復用或分配專用pad的方式引出到SoC的頂層端口上即可。對于CPU軟核和硬件邏輯,采用掃描鏈插入工具采用自頂向下的方式插入掃描鏈。

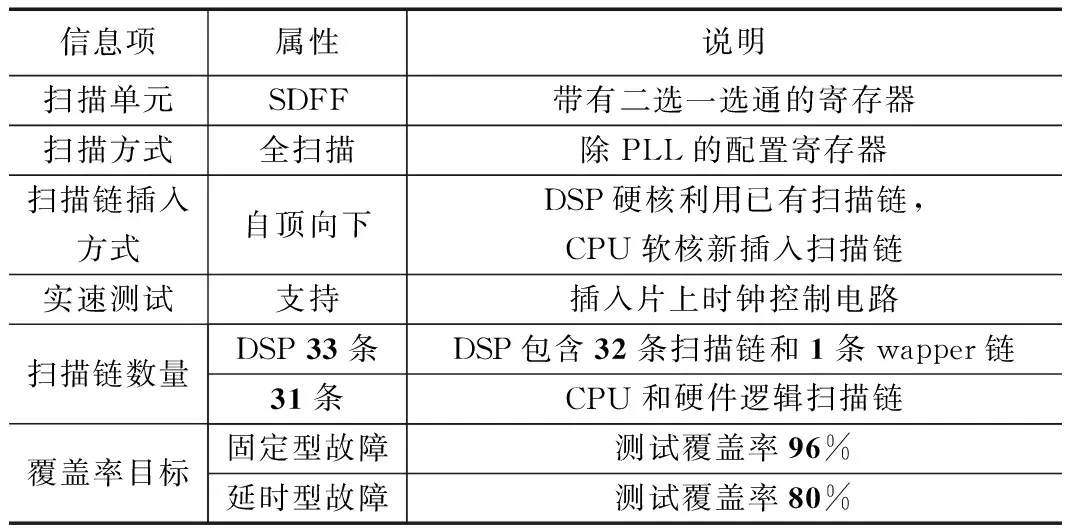

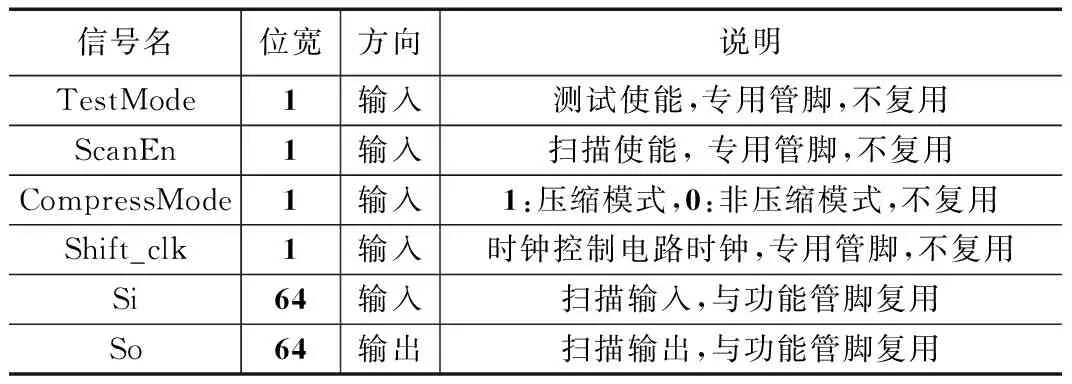

由于實速測試需要使用較高的測試時鐘頻率,而一般測試機提供的時鐘無法達到要求的頻率,使用可以提供高頻時鐘的測試機又往往成本昂貴,故需要設計一種專門的時鐘結構電路,使實速測試不必由測試機提供高速時鐘,而是使用芯片內部PLL輸出的高速時鐘。芯片可測性設計中采用一個專用片上時鐘控制電路(OCC)解決實速測試的時鐘問題。掃描鏈測試采用全掃描設計,合理劃分可測性設計的控制端口和掃描鏈數目,通過掃描測試模式選擇信號控制時鐘和復位信號的可控性。同時,通過增加掃描寄存器,將內部不可控和不可觀測的陰影邏輯修改為可控和可觀測邏輯,增加內部邏輯的可控性和可觀測性,可以提高掃描鏈測試的覆蓋率。SoC芯片內部的高速時鐘域包括CPU時鐘,DSP時鐘和AXI總線時鐘,在每個時鐘源處插入一個OCC控制電路可以實現全芯片的實速測試,SoC芯片掃描鏈設計信息和控制接口設計分別見表1和表2。

表1 掃描鏈設計信息表

表2 掃描鏈控制接口表

3 掃描鏈測試設計實現

3.1 固定型故障測試掃描鏈設計實現

3.1.1 DSP掃描鏈測試設計

DSP硬核內部已經包含有掃描鏈結構,將DSP集成到SoC內部時將DSP的掃描鏈控制接口復用到芯片頂層的端口實現掃描控制和測試向量輸入,測試使能信號、掃描使能信號、壓縮模式信號和Shift_clk時鐘采用芯片專用管腳,掃描鏈輸入和輸出管腳通過復用芯片頂層功能管腳實現。管腳復用完成后將頂層端口的控制端口信息加入到DSP的測試向量中,即可實現用SoC端口和DSP硬核自身的測試向量實現DSP的掃描鏈測試。

3.1.2 CPU掃描鏈測試設計

CPU和其余硬件邏輯的掃描鏈測試設計包括兩部分內容:掃描鏈插入和測試矢量生成[4]。其中,掃描鏈插入具體的步驟為:

1)讀入設計文件:讀入的文件可以是DC綜合后的Verilog格式或DDC格式的網表文件。

2)創建測試協議:創建測試協議需要定義測試相關的信號,包括定義時鐘信號、復位信號、常量、測試模式、測試壓縮信號、掃描端口信號(SI,SO,SE等)和掃描單元類型等,采用DFT Compiler工具腳本創建spf格式的測試協議文件。

3)設計規則檢查(DRC):掃描鏈測試要求電路中的每個節點處于可控制和可觀測狀態,只有這樣才可以保證其可替換為相應的掃描單元,并且保證故障覆蓋率。為了保證電路中的每個節點都符合設計需求,在掃描鏈插入前會進行掃描設計規則的檢查并根據DRC檢查結果修改設計。基本設計規則包括:

(1)使用同種類掃描單元進行替換,選擇帶多路選擇器的掃描觸發器;

(2)在原始輸入端必須能夠對所有觸發器的時鐘端和異步復位端進行控制;

(3)時鐘信號不能作為觸發器的輸入信號;

(4)三態總線在掃描輸入模式處于非活躍狀態;

(5)ATPG無法識別的邏輯應加以屏蔽和旁路;

(6)門控時鐘或者門控異步輸入端設計規則。

除了以上基本規則,其它設計規則還包括:

(7)盡量避免異步時鐘設計;

(8)限制不同時鐘域的數量;

(9)對于多時鐘域的設計,處于同一時鐘域的觸發器最好連接在同一根掃描鏈上;

(10)對于扇出比較多的端口,如ScanEn信號,在綜合的時候需要注意;

(11)對于存儲器,模擬電路等不可綜合的邏輯加入適當的隔離旁路結構;

(12)避免過長的掃描鏈,設置加入掃描壓縮電路;

(13)盡量減少額外邏輯帶來的面積、功耗的增大;

(14)通過復用引腳,減少掃描測試對引腳的要求。

4)插入掃描鏈:為了使得掃描鏈長度更加均衡,設計對掃描鏈鏈加入mix_clock功能;

5)插入掃描鏈后執行DRC檢查;

6)生成測試協議文件和網表文件,用于后續的自動測試向量生成。

3.2 實速測試掃描鏈設計實現

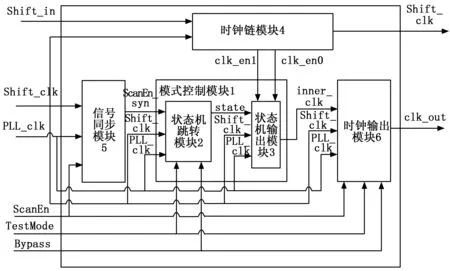

實速測試用于檢測時延故障,其掃描鏈結構和測試流程與普通的掃描鏈測試一致,不同之處在于在掃描鏈捕獲階段的時鐘不同。SoC芯片內部主要包含CPU時鐘、DSP時鐘、AXI時鐘和APB時鐘4個時鐘域,其中CPU時鐘、DSP時鐘和AXI時鐘為高速時鐘,APB為48MHz低速時鐘。為實現實速測試,在異構雙核SoC芯片內部高速時鐘設計片上時鐘控制電路。片上時鐘控制電路的作用為在掃描鏈的捕獲階段輸出2個或多個高速的捕獲脈沖,寄存器通過高速捕獲脈沖寄存組合邏輯的輸出值并通過掃描鏈輸出,在掃描輸出端口與期望測試結果比較即可判斷芯片內部是否存在時延故障。片上時鐘電路的結構如圖3所示。

圖3 片上時鐘控制電路的結構圖

片上時鐘控制電路包括:模式控制模塊、時鐘鏈模塊、信號同步模塊和時鐘輸出模塊。信號同步模塊輸入移位時鐘shift_clk和高速時鐘PLL_clk,shift_clk時鐘由芯片外部輸入,用于實速測試中掃描寄存器的移位,PLL_clk時鐘由芯片內部PLL產生,用于芯片功能時鐘或實速測試捕獲時鐘。通過寄存器同步方式對掃描使能信號ScanEn進行同步化,為保證同步后的ScanEn_syn信號可以正確的被shift_clk和PLL_clk時鐘的上升沿采樣,采用下降沿同步的方式。由于移位時鐘Shift_clk的頻率較低,故采用Shift_clk時鐘對ScanEn信號進行一級寄存器同步,而PLL輸出的時鐘頻率較高,采用PLL_clk時鐘對ScanEn信號進行三級寄存器同步。

時鐘鏈模塊通過移位寄存器移位的方式將高速時鐘使能信號移入由10個觸發器組成的移位寄存器組,當觸發器輸入ATPG工具生成的二進制測試向量‘0’表示不產生高速時鐘使能信號,‘1’表示產生高速時鐘使能信號。測試向量中1的個數控制時鐘鏈模塊輸出的高速時鐘脈沖使能信號的個數。由于實速測試捕獲階段至少需要一個發射時鐘和一個捕獲時鐘,測試向量中1的個數為2-10個,故時鐘鏈模塊可以產生2到10個高速時鐘使能信號。

模式控制模塊包括狀態機跳轉模塊和狀態機輸出模塊。狀態機跳轉模塊根據3個控制信號決定當前電路的時鐘模式,3個控制信號分別為測試模式信號TestMode,旁路信號Bypass和掃描使能信號ScanEn。只要信號TestMode=0時,電路就處于功能模式;當信號TestMode=1并且Bypass=1時,電路處于旁路模式;當信號TestMode=1、Bypass=0、ScanEn=1時,電路處于移位模式;當信號TestMode=1、Bypass=0、ScanEn=0時,電路處于捕獲模式。狀態機跳轉模塊控制狀態機產生state狀態信號,狀態機輸出模塊根據state值輸出內部時鐘inner_clk信號。

時鐘輸出模塊根據當前的時鐘模式,控制選擇器輸出相應的時鐘。當TestMode為0時,輸出高速時鐘PLL_clk;當TestMode為1,Bypass 為0,ScanEn為1時,輸出shift_clk;當TestMode為1,Bypass 為0,ScanEn為0時,輸出inner_clk;當TestMode為1,Bypass 為1時,輸出移位時鐘shift_clk。

通過片上時鐘控制電路,可以產生芯片實速測試需要的高速時鐘,進而實現芯片的實速測試,檢測芯片的時延故障。

3.3 自動測試向量生成設計實現

異構雙核SoC掃描鏈的ATPG設計的目的是產生測試向量并進行覆蓋率評估。ATPG使用synopsys公司的tetramax軟件,版本為J-2014.09;通過tetramax工具可以查看掃描鏈是否插入成功,另外,通過對測試覆蓋率的評估,可以評判可測試性設計的優劣。ATPG設計實現過程如下:

1)讀取測試協議spf文件:其中,對于剛剛從design_compiler中生成的spf而言,需要在test_seup階段啟動時鐘信號,通常還會配置復位信號;

2)讀取帶掃描鏈的網表設計文件;

3)讀入tetramax使用的庫文件:讀取工藝廠的庫文件,變成tetramax可以識別的庫文件;

4)構造ATPG模型;

5)DRC檢查,如果DRC檢查沒有通過,通過tetramax可以分析原因,通常的原因是時鐘、異步復位和測試控制信號不受控;

6)設置故障類型,覆蓋率目標等參數;

7)運行ATPG,生成測試向量和對應的測試激勵;

8)通過VCS仿真生成的測試向量。

4 掃描鏈測試結果

異構雙核SoC采用全掃描測試設計,芯片共含有83000多個觸發器,另外,異構雙核SoC內部共有64條掃描鏈,平均長度約為1 296。通過ATPG工具生成測試向量,stuck-at測試向量個數為9 352個,固定型故障測試覆蓋率為97.6%;實速測試生成測試向量個數10 380個,時延故障測試覆蓋率為84.9%,滿足芯片的測試故障覆蓋率要求。

5 結束語

針對雙核SoC的特點,給出了一種有效的掃描鏈測試方案,并設計了片上時鐘控制電路,實現了芯片實速測試。結果表明,芯片的固定故障和時延相關故障測試覆蓋率滿足要求。

同時,設計的片上時鐘控制電路可以方便的移植到不同的芯片掃描鏈測試設計中。

[1] 周 妮,喬 飛,譚斯斯,等.32位MIPS處理器可測性設計與實現[J].微電子學,2010, 40(6):782-791.

[2] 成 立,王振宇,高 平,等.VLSI電路可測性設計技術及其應用綜述[J].半導體技術,2004,29(5):21-23.

[3] IEEE Standard Test Access Port And Boundary-Scan Architecture,IEEE Std 1149.1-1990[S].

[4] 徐勇軍,張 伸,張志敏,等.SoC設計中的掃描測試技術[S].計算機輔助設計與圖形學學報,2005,17 (12): 2685-2689.

[5] Steininger A. Testing and built-in self-test A survey[J]. Journal of Systems Architecture, 2000,46:721-747.

[6] 徐智偉,張盛兵.SoC的可測性設計策略[J].計算機測量與控制,2008,16(8):1095-1098.

Design and Implementation of Scan Based Test for Dual-core SoC

Liu Guangdong, Shi Guoshuai, Xu Haoran

(Institute of Beijing Computer Technology and Application,Beijing 100854, China)

In order to detect the defect of manufacturing such as short and open circuit, the scan based DFT circuit of dual core SoC is realized. The scan structure has been inserted into the hard-core DSP, so the DSP’s test ports are connected to the SoC chip leads. Scan chains are inserted into the CPU core and other hardware logic. Scan based test supports stuck-at fault and transition fault test. According to the transition fault, an on-chip clock control circuit is designed to use high speed PLL clock for at-speed test. The ATPG tool is used to generate test vectors, the result shows that the stuck-at fault test coverage rate can reach 97.6%, transition fault test coverage rate can reach 84.9%, meet the test coverage requirements of the chip.

design for testability; scan based test; dual-core ; on chip clock

2016-10-24;

2016-11-22。

劉廣東(1985-),男,山東省單縣人,碩士研究生,工程師,主要從事SoC可測性設計方向的研究。

1671-4598(2017)04-0015-03

10.16526/j.cnki.11-4762/tp.2017.04.005

TN407

A