基于DSP+FPGA的新型彈載計算機設計與實現

胡 博,李 毅,邢廣義,張 拓,王 蕊

(中國航天科技集團公司 第四研究院第四十一研究所,西安 710025)

基于DSP+FPGA的新型彈載計算機設計與實現

胡 博,李 毅,邢廣義,張 拓,王 蕊

(中國航天科技集團公司 第四研究院第四十一研究所,西安 710025)

以某型號導彈飛行試驗為研制背景,設計出一款精度高、通用性強的新型彈載計算機。該彈載計算機以高性能DSP和FPGA為系統框架,通過其豐富的外圍接口和強大的處理能力,結合AD5764轉換模塊、MAX3490通信模塊、ADUM1401四通道數字隔離器和ULN2801達林頓管驅動器組成的離散量輸出等模塊,解決了彈載計算機與彈上飛控部件之間復雜的并行數據處理以及多種控制算法實時解算問題,具有體積小、重量輕、精度高、實時性好等特點;經過多次飛行試驗表明,該彈載計算機具有較高的可靠性和穩定性,應用前景非常廣泛。

彈載計算機; DSP; FPGA

0 引言

精度高、體積小的精確制導武器已經逐漸成為當今世界戰爭中取得主動權的重要武器,作為精確制導導彈核心部件之一的彈載計算機,其性能將直接決定導彈的穩定性和精確度。彈載計算機不僅需要對彈體的位置和姿態進行控制,還需要和各個分系統進行實時通訊,保證控制系統的控制精度和實時性。目前由于數字信號處理器(DSP)和可編程邏輯門陣列(FPGA)芯片的快速發展,以這兩個芯片為核心的彈載計算機是現在計算機研究的主流方向和發展趨勢[1]。

本文設計一種基于高性能DSP和FPGA為框架的彈載計算機,解決了彈載計算機與彈上其他設備之間復雜的并行處理以及多種控制算法實時解算問題,該計算機已參與多次導彈閉環飛行試驗,試驗結果表明,該彈載計算機具有控制精度高、可靠性高、實時性好等優點。

1 彈載計算機系統組成

彈載計算機內部主要由DSP和FPGA來實現控制算法以及與各部件之間的通信,并通過串口通信模塊實現對各個部件的控制,彈載計算機系統組成及與各部件之間的連接示意圖如圖1所示。DSP核心處理模塊主要包括DSP、FLASH、SDRAM, FPGA接口模塊主要包括多路帶FIFO的串行接口、I/O接口以及其它外圍電路。彈載計算機系統核心模塊DSP和FPGA功能如下:

1)DSP核心處理器模塊主要功能:完成控制算法的解算;根據飛行時序的要求,實時輸出時序控制指令。

2)FPGA核心處理器模塊主要功能:通過D/A轉換模塊,將模擬信號轉換為數字信號發給舵機,控制導彈的姿態;通過離散量輸出模塊,對多路點火信號進行準確的控制;通過串行通訊模塊,實現彈載計算機與其他部件之間的通信,完成與各部件之間的收發功能。

圖1 彈載計算機系統組成及與各部件連接示意圖

2 主處理器選型

數字信號處理器(DSP)具有哈佛結構、流水線操作、高速硬件乘法器等特點,因此非常適用于高速采集、實時信號處理以及實時控制系統。目前國內主流的彈載計算機常用的芯片是C3X和C2000系列DSP[2],但由于現在導彈技術不斷地升級,對彈載計算機的精度要求不斷提升,再綜合考慮到控制性能要求、處理速度、硬件資源等要求,我們選用TI公司更高一級的DSP芯片,C6000系列TMS320C6713B型DSP[3]。

TMS320C6713B是一款32位高性能浮點型DSP,最高主頻可以達到300 MHz,內置256 KB存儲器,具有16通道EDMA協處理器,EMIF總線接口,2個McBSP,支持4路外部中斷,還具有BOOT、ENDIAN、HPI等功能配置模式。豐富的內部和外部資源可以很好的提高控制算法的精確度和速度[4]。

FPGA芯片選用Microsemi公司新型的SmartFusion2[5],該款芯片是一款獨特的Flash架構FPGA,這種架構使該款芯片具有無與倫比的安全性、可靠性和低功耗,非常適合用于軍事、航天、航空等領域。SmartFusion2這款高性能FPGA,具有從5k到120k LUT(look-up table)的密度范圍;多達181個400MHz雙端口SRAM;多達185個三端口SRAM以及多達185個快速乘法單元,能很好的滿足彈載計算機所需要的通信并行處理需求。

3 系統主要硬件設計

彈載計算機硬件結構如圖1所示,除主處理器外還包括EMIF總線模塊、D/A輸出模塊、串行通信模塊、離散量輸出模塊、電源模塊、外部存儲器模塊等。

3.1 EMIF總線模塊

本系統設計的外部存儲器主要由SDRAM和FLASH組成,通過DSP的EMIF總線實現對兩者的管理[6]。

本設計SDRAM數據存儲器選用Micron公司生產的MT48LC4M32B2。SDRAM設計在DSP的EMIF接口的CE0空間,地址范圍為0x8000 0000~0x80FF FFFF(SDRAM容量為16Mbyte),SDRAM與DSP的EMIF總線接口連接如圖2所示,外部時鐘信號經ECLKIN輸入后經過鎖相環電路PLL會產生EMIF接口的時鐘信號ECLKOUT,供SDRAM使用。

圖2 SDRAM與DSP的EMIF總線連接示意圖

3.2 D/A輸出模塊

制導系統對導彈方向的精確控制是通過控制舵機的偏轉角度實現的,因此彈載計算機需要實時的將控制指令發送給舵機,但是由于彈載計算機輸出的控制指令為數字信號,而舵機控制采用的是模擬信號,因此必須采用D/A轉換芯片來實現數字信號到模擬信號的轉換。

根據系統實際需要,本系統選用AD公司的AD5764芯片,該芯片為完整的4通道、16位、雙極性輸出型DAC,采用±11.4±16.5 V電源供電,標稱滿量程輸出范圍為±10 V,采用的是串行的SPI接口,芯片內部共集成了4路獨立的D/A轉換電路,對應著4路模擬量輸出,內置輸出放大器。5 V基準源由REF50提供。D/A原理如圖3所示。

圖3 D/A輸出原理圖

3.3 串行通訊接口設計

彈載計算機系統在工作時需要和各個部件實時的進行通信。與發控裝置通信完成對導彈的實時控制;與慣導裝置通信完成對制導系統的實時解算;與記錄裝置通信完成對解算數據的實時記錄;與數據鏈通信完成對數據的實時傳輸;與導引頭通信完成對目標的精確制導,因此串行通信接口在彈載計算機系統中非常的重要。

我們利用TMS320C6713B 的EMIF接口可以方便地連接多種擴展器件的特點,將FPGA芯片連接在EMIF接口上完成多串口的擴展。本系統所采用的都是RS422串行通信接口,為了滿足設計的需要,我們選用MAX3490芯片完成RS422的電平轉換。MAX3490是一款工作在3.3 V電壓下,傳輸速率可達到10 Mbps的RS422發送接收器。串行通信接口電路如圖4所示。

圖4 RS422串行通信接口電路

3.4 離散量輸出模塊設計

制導導彈中除了大量的電子裝置外,還有必要的火工品裝置,為了能在導彈的飛行過程中對火工品點火時序進行準確的控制,在設計此款彈載計算機的時候充分地考慮了點火的需求。

考慮到每路點火信號的安全性和輸出穩定性,本設計選用ADUM1401四通道數字隔離器和ULN2801達林頓管驅動器作為點火信號輸出的主器件,ADUM1401最大的優點就是具有簡單的iCoupler數字接口和穩定的性能特征,可消除光耦合器通常具有的電流傳輸不確定性、非線性傳遞函數以及溫度和使用壽命影響等問題;ULN2801則非常適用于TTL電平接口和需要較高的電流/電壓要求輸出的電路。因此選用此兩種器件可以有效地將采集到的每一路點火信號進行隔離,同時還可以輸出穩定的點火脈沖。離散量輸出模塊如圖5所示。

圖5 離散量輸出模塊原理圖

3.5 其他模塊設計

其他模塊主要包括電源模塊、外部存儲器模塊等。彈載計算機由外部電源板提供±15 V,以及5 V電壓。板上設計電源芯片TPS70345,分別為DSP及FPGA供電。外擴FLASH主要完成彈載計算機數據的存儲,實現掉電保存功能,芯片采用AMD公司的AM29LV160D,該芯片提供2M*8Bit存儲空間,數據訪問時間最快達到70 ns,FLASH 存儲器設計在 DSP 的 EMIF 接口的 CE1 空間,地址空間為 0x90000000~0x90FFFFFF,滿足設計要求。

4 彈載計算機軟件設計

系統軟件包括DSP軟件及FPGA軟件[7]。FPGA程序主要完成與各個部件的通信,DSP程序主要完成時序控制、控制率的解算。在主程序工作流程中,彈載計算機以中斷方式10ms接收發控裝置的指令以及與各個部件之間的通信信息,彈載計算機工作流程如圖6所示。

圖6 彈載計算機工作流程圖

5 試驗結果分析

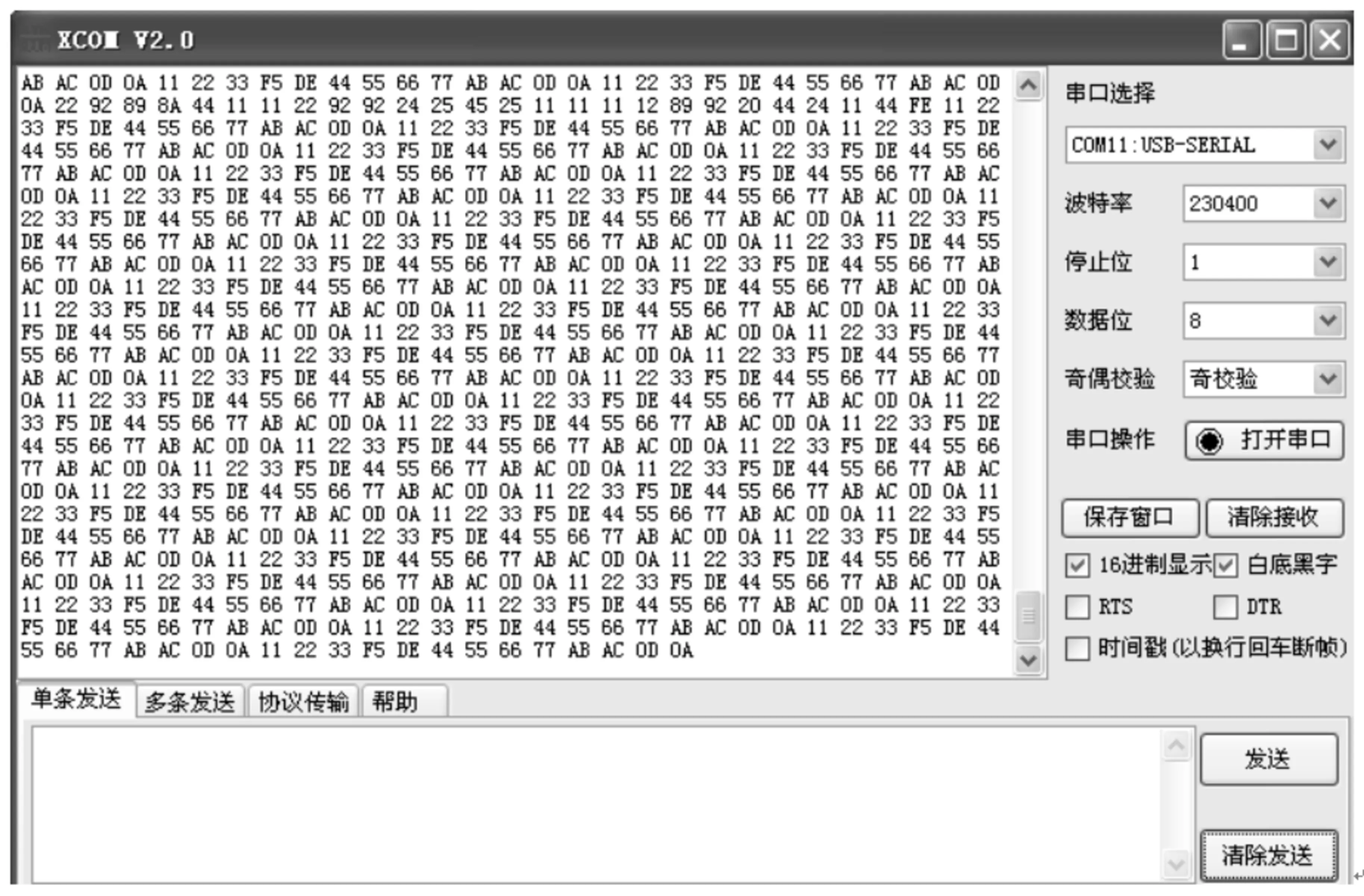

該彈載計算機已經經過多次試驗驗證,舵機舵1的指令與反饋曲線如圖7所示,可以看出彈載計算機輸出的舵機指令和舵機自身的反饋基本吻合,舵指令解算誤差小于5 mV,滿足導彈控制系統控制精度要求。慣導裝置和記錄裝置接收數據結果如圖8、圖9所示,可以看出彈載計算機與慣導裝置和記錄裝置之間的通信完全正常。

圖7 舵機舵1指令與舵反饋曲線

圖8 慣導裝置數據接收示意圖

圖9 記錄裝置數據接收示意圖

6 結束語

本文采用DSP+FPGA主協處理器方案設計了一款工程實用的彈載計算機,該計算機結構緊湊、可靠性強、控制精度高,目前已通過多次飛行試驗考核,試驗結果表明,彈載計算機工作正常、性能穩定,滿足導彈控制系統設計要求。

[1] 緱利敏,景德勝,等.基于DSP+FPGA的但在綜合控制計算機設計與實現[J].電子技術,2013(7):43-45.

[2] 劉軍虎,吳學森.基于DSP的新型彈載控制計算機[J].炸彈與航天與在技術,2002:25-30.

[3] 李方慧,王 飛,何佩琨.TMS320C6000系列原理與應用[M].北京:電子工業出版社,2005.

[4] 三恒星科技.TMS320C6713DSP原理與應用實例[M].北京:電子工業出版社,2009.

[5] SmartFusion2 SoC Family Data Sheet[Z]. 2012.

[6] 孟英杰.基于DSP的彈載計算機系統設計[D].哈爾濱工業大學,2012.

[7] 胡海龍,彭啟宗.TMS320C6713基于DSP/BIOS的二級BootLoader開發[J].現代電子技術,2005:74-76.

Design and Implementation of a New Missile-Borne Computer Based on DSP+FPGA

Hu Bo, Li Yi,Xing Guangyi,Zhang Tuo,Wang Rui

(41st Institute, Academy of China Aerospace Science and Technology Corporation, Xi’an 710025,China)

Based on the development of a certain type of missile flight test, a new missile-borne computer which has high precision and high universality has been designed. The missile-borne computer with high performance DSP and FPGA as the system framework, through its rich peripheral interface and powerful processing capabilities, combined with the AD5764 conversion module, MAX3490 communication module, the discrete output module with ADUM1401 four channel digital isolator and ULN2801 Darlington tube etc, which solved the problem of the complex parallel date processing between the missile-borne computer and other flight control components, while solved the problem of real-time calculation of a variety of control algorithms, also it has the advantages of small volume, light weight, high precision, good real-time characteristic and so on. The missile-borne computer has passed many flight experiments, the results show that it has high reliability and stability, while the prospect of application is very extensive.

missile-borne computer; DSP; FPGA

2016-11-02;

2016-11-22。

胡 博(1988-),男,西安人,碩士,工程師,主要從事彈載計算機和彈上軟件方向的設計和研究。

1671-4598(2017)04-0110-03

10.16526/j.cnki.11-4762/tp.2017.04.031

TP27

A