基于FPGA的DDS設(shè)計與實現(xiàn)

靳成一+肖蕾

摘 要

DDS在電信和電子儀器方面的應(yīng)用已經(jīng)非常廣泛,是完成設(shè)備數(shù)字化的重要技術(shù)。筆者設(shè)計、利用ISE10.0軟件實現(xiàn)三相矩形波信號、正弦波信號以及調(diào)頻調(diào)相信號的波形仿真,同時用Xilinx的FPGA核心板SPARTAN3AN,與性能很好的MCU—ATMEGA128相結(jié)合,進行DDS的設(shè)計和實現(xiàn)。

【關(guān)鍵詞】FPGADDS設(shè)計 實現(xiàn)

由于直接數(shù)字頻率合成技術(shù)(簡稱DDS)有高分辨率、低功耗、低成本、全數(shù)字化接口、快速轉(zhuǎn)換時間以及容易跟微處理器結(jié)合等諸多優(yōu)勢,最近這些年的發(fā)展十分迅速。盡管現(xiàn)在不少的芯片制造企業(yè)研發(fā)出專用DDS芯片,但在一些特殊的場合,其輸出的波形帶寬、種類以及精度等均不能滿足設(shè)計需求。故而,把DDS和高性能數(shù)字器件有機結(jié)合就成為現(xiàn)在的熱點課題。

1 DDS的原理

DDS主要是運用正弦信號的相位和時間成線性關(guān)系這一特征,借助查表的方法獲取信號的瞬時值,以達到頻率合成。相位累加器是通過N位加法器和累加寄存器級聯(lián)而成。每當(dāng)進行一時鐘脈沖Fs,加法器都會把頻率控制字K和累加寄存器所輸出的累加相位數(shù)加到一起,把所得到的結(jié)果送到累加寄存器的數(shù)據(jù)輸入端。累加寄存器會把上一時鐘脈沖所得到的相位數(shù)反饋至加法器的輸入端,從而使加法器在下一時鐘脈沖繼續(xù)跟頻率控制字K進行相加。把相位累加器所輸出的數(shù)據(jù)當(dāng)作波形存儲器的相位取樣的地址,如此就能將存于存儲器中的波形抽樣值通過表查出,以實現(xiàn)從相位至幅值的轉(zhuǎn)換。該存儲器的輸出數(shù)據(jù)先送至D/A轉(zhuǎn)換器中,而后由D/A轉(zhuǎn)換器把用數(shù)字量表示的波形幅值轉(zhuǎn)換為合成頻率的模擬量形式信號。

2 基于FPGA的DDS設(shè)計

2.1 系統(tǒng)整體設(shè)計

運用Xilinx的XC3S400FPGA,盡量達到設(shè)計的數(shù)字化與集成化。在實現(xiàn)的時候,運用VHDL語言將DDS進行封裝,以有效達到資源的復(fù)用和及靈活配置。加之單片機的控制、液晶顯示和數(shù)據(jù)的轉(zhuǎn)換,能夠比較理想的達到設(shè)計要求。系統(tǒng)的框圖如圖1中所示。

2.2 DDS核心設(shè)計

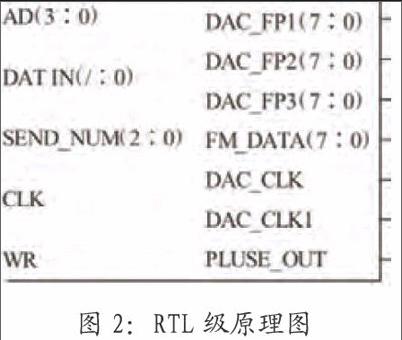

DDS的核心就在FPGA電路方面的設(shè)計。在FPGA電路實現(xiàn)以后,就可以在FPGA中生成波形數(shù)字信號。在設(shè)計過程里用VHDL語言,可構(gòu)建一標(biāo)準(zhǔn)正弦波產(chǎn)生和FM調(diào)制功能的DDS模塊,同時還構(gòu)建起一矩形波產(chǎn)生模塊。這一部分設(shè)計在ISE綜合以后的RTL級原理見圖2中所示。DDS其核心就是累加器和查表兩個模塊。

2.3 對累加器進行設(shè)計

DDS核心是相位累加器,輸出正弦波的頻率是由DDS與參考時鐘等所決定。即DDS輸出的信號頻率=(fclk×Kf)/2N,其中,累加器位數(shù)由N表示,累加時鐘頻率用fclk表示,控制字用Kf表示,因為耗時隨著位數(shù)N的變化而變化,所以,保證輸出頻率前提下,可以利用參考頻率的降低來提高其分辨率,本文N=32。

3 基于FPGA的DDS實現(xiàn)

3.1 設(shè)計實現(xiàn)在ISE中的DDS模塊

本設(shè)計利用的是ISE10.0軟件,其中各個小模塊要利用VHDL語言進行設(shè)計,結(jié)合DDS的原理,連接軟件中的各個模塊,最后實現(xiàn)在FPGA中DDS模塊的設(shè)計。

3.2 實現(xiàn)MODESIM中的仿真

在MODESIM中,對正弦波、方波和調(diào)頻波仿真,然后再檢驗仿真生成的波形。為了檢驗是否能夠符合設(shè)計要求,分別對各個波形進行如下測試,一是相位是0°、225°、315°,正弦波頻率是1KHz;載波頻率是10KHz,F(xiàn)M調(diào)制信號頻率是1KHz;占空比是0.5,方波頻率是50MHz等等。結(jié)果是都能滿足其要求。

4 基于FPGA的DDS硬件實現(xiàn)

4.1 硬件設(shè)計的實現(xiàn)

FPGA被作為是DDS的模塊載體,利用的核心板是SPARTAN3AN,速度高,穩(wěn)定性強。在本系統(tǒng)中,MCU利用的是ATMEGA128單片機,此單片機是ATMEL公司開發(fā)的。而系統(tǒng)的主控芯片完成參數(shù)輸入是借助于4*4的薄膜按鍵,操作狀態(tài)和數(shù)據(jù)由OCMJ4x8C液晶顯示器可以顯示出來,其顯示器與DDS模塊通信,能夠?qū)敵龅牟ㄐ芜M行控制。

4.2 進行數(shù)據(jù)測試和相關(guān)分析

表1匯總了對三相正弦波信號頻率進行測試的結(jié)果,其中,測試數(shù)據(jù)大多間隔1分鐘。多次測量與分析發(fā)現(xiàn)頻率的精度要高于0.1%,而穩(wěn)定度要高于10至6,同時輸出信號的峰峰值要大于等于20V,可以任意調(diào)整三相正弦信號的相位。另外,測試并且分析矩形波信號與調(diào)頻波信號,都能符合設(shè)計指標(biāo)。

5 結(jié)語

綜上,利用FPGA器件,本設(shè)計采用了DDS技術(shù)進而研制了全數(shù)字波形信號發(fā)生器。通過仿真與實測說明,頻率小則切換速度快,而且頻率也容易得到控制,設(shè)計電路也較簡單。因此, 本系統(tǒng)可據(jù)其實際,輸出多種波形圖,功能多樣,有調(diào)頻、調(diào)相與調(diào)幅等,實用性良好。

參考文獻

[1]張厥勝,曹麗娜.鎖相與頻率合成技術(shù)[M].成都:電子科技大學(xué)出版社,1995:140-147.

[2]姜萍,王建新,吉訓(xùn)生.FPGA實現(xiàn)的直接數(shù)字頻率合成器[J].電子技術(shù)應(yīng)用,2002,28(05):43-44.

[3]劉晨,王森章.直接數(shù)字頻率合成器的設(shè)計及FPGA實現(xiàn)[J].微電子與計算機,2004,21(05):63-65.

[4]宋陽,孫肖子,仁愛鋒.基于DDS和FPGA的虛擬智能信號源的研究[J].數(shù)據(jù)采集與處理,2001,16(專輯):124-126.