TMS320C6678中的高速串行接口RapidIO研究

盧建章,劉洋

(1.中航工業雷華電子技術研究所,無錫 214063;2.江南計算技術研究所)

TMS320C6678中的高速串行接口RapidIO研究

盧建章1,劉洋2

(1.中航工業雷華電子技術研究所,無錫 214063;2.江南計算技術研究所)

本文從嵌入式多核處理器之間高速數據通信的應用出發,結合對TI的TMS320C6678多核DSP的認識,開展了對RapidIO(SRIO)接口協議和TMS320C6678 SRIO模塊結構的研究。并在此基礎上,工程實現了TMS320C6678片間SRIO通信的詳細配置過程,并對其通信性能進行了評測分析,為多核DSP系統級通信的設計提供了一定的參考。

TMS320C6678;RapidIO;處理器間通信

引 言

為了實現高性能的嵌入式系統,由Mercury和Freescale共同研發的RapidIO互連技術發展起來,其具有高傳輸效率、低系統成本和高可靠性等特點,RapidIO協議為嵌入式系統各器件之間提供高帶寬、低延時的數據傳輸,并且可以支持板到板、芯片到芯片間的通信。

2010年11月,TI公司發布了KeyStone結構的8核DSP處理器TMS320C6678,其每個C66x內核主頻最高達1.25 GHz,可以提供每秒高達40 GB MAC定點運算和20 GB FLOP浮點運算能力[1];該芯片中集成了一個兼容于RapidIO互聯規范REV2.1.1的4通道的SRIO模塊,可配置成1x, 2x, 4x模式,每通道支持1.25 Gbps、2.5 Gbps、3.125 Gbps和5 Gbps的傳輸速率[1]。SRIO的數據格式默認采用大端格式,支持8b/16b的設備ID、組播ID,同時額外支持錯誤管理、阻塞控制,為實現系統級的互聯提供了可行方案。適用于諸如雷達信號處理等對定浮點運算能力以及大數據通信有較高要求的超高性能計算應用。

基于以上分析,本文針對TMS320C6678多核處理器,首先介紹了SRIO的傳輸協議,分析TMS320C6678的SRIO收發模型和配置過程,并對其傳輸帶寬進行了評測,為多處理器系統的設計提供了一定的參考。

1 SRIO協議簡介

RapidIO技術是一種基于協議包格式的互聯技術,在TMS320C6678芯片手冊中,通常把RapidIO稱為SRIO,為DSP之間提供一種高帶寬、低延遲、低系統成本的通信,是系統互連的最佳選擇之一,下面分析SRIO的協議構成。

1.1 SRIO協議概述

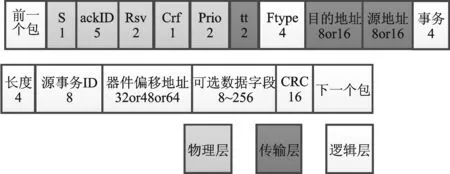

圖1 SRIO協議層次結構圖

為了滿足靈活性和可擴展性的要求,SRIO協議可分為三層:邏輯層、傳輸層和物理層,如圖1所示。邏輯層位于頂層,定義了在應用程序中如何通信、包格式、為端點器件發起完成事務提供信息,它支持DirectI/O、消息傳遞和全局共享存儲。傳輸層位于中間層,數據傳輸的地址空間和傳輸包所需的路由信息由它來定義。物理層位于底層,定義了設備級接口、報文傳輸、流量控制、電氣特性、底層錯誤處理等[2]。

1.2 SRIO協議包

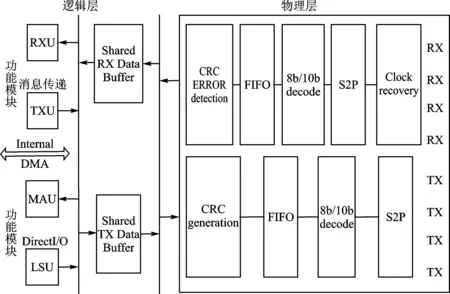

SRIO是基于包交換的數據傳輸協議。一個傳輸包由屬于邏輯層、傳輸層和物理層的數據域組成。邏輯層域由包頭(定義入口類型)和有效載荷(即數據)組成。傳輸層域從物理布局上來說,在某種意義上是獨立的,由發送和接收設備的源ID號和目的ID號等組成。物理層在物理接口上是獨立的,包含優先級、信息確認和錯誤檢測域。SRIO協議包如圖2所示。

圖2 SRIO協議包

圖3 SRIO的數據流圖

數據包最外層為物理層字段,最內層為邏輯層字段,中間的為傳輸層字段,圖2中的數字為字節數。其中S字段用來表示該包是一個數據包還是一個控制符號。ackID是鏈路級包鑒定符,即包序列號,每發送一個包,ackID加1。Prio為優先級字段,tt、目的地址和源地址表示傳輸地址的類型,即包接收和產生地址是8位還是16位。Ftype代表被請求的事務類型,不同類型的SRIO包協議也略有不同。長度為編碼后的事務長度,SRIO最多允許256個待完成事務。在源事務ID之后是器件偏移地址。后面接著有效數據載荷,再以16位循環冗余校驗碼(CRC)結束,接收端通過CRC校驗碼來判斷這個包是否正確。

2 TMS320C6678中SRIO實現

TMS320C6678是一款處理能力很強的新型高性能多核DSP,相比于之前的芯片,集成了豐富的外設,如PCI總線端口、千兆以太網端口、64位無縫外部存儲器端口、HyperLink端口等,最重要的是增加了對SRIO支持的模塊。

2.1 SRIO模塊簡介

TMS320C6678芯片的SRIO接口是一個外部驅動的從設備模塊,同時能夠在DSP芯片內作為一個主設備。這意味著外部設備可以根據需求傳輸(突發寫入)數據到DSP內部,而無需向CPU發送中斷或依賴DSP 芯片的EDMA資源。這種機制既降低了系統的中斷個數,又減少了與只讀外設的握手操作,同時還釋放了 EDMA資源以便其他任務使用。

SRIO外設模塊的數據流如圖3所示。當接收數據包時,高速數據包在物理層依次進行時鐘恢復、串并轉換、8b/10b解碼,并將之緩存在各個端口的緩存區,最后進行 CRC 錯誤檢測;相反,當發送數據包時,數據包首先進行 CRC 生成,經過各個端口的緩存區后依次進行8b/10b編碼、并串轉換,最后到達發送端口。數據包在邏輯層與物理層間通過發送共享緩存區和接收緩存區進行過渡,最后到達邏輯層的數據包,整個包已被解碼,負載數據已被緩存,根據接收的數據包類型的不同,包的進一步操作通過功能模塊來實現,其中LSU(Load/Stone Unit)負責控制發送DirectI/O模式的數據包,MAU(Memory Access Unit)負責控制接收DirectI/O模式的數據包,TXU負責控制發送消息傳遞模式的數據包,RXU負責控制接收消息傳遞模式的數據包。這4個單元通過內部DMA與DSP芯片的存儲器進行通信,通過緩存區和接收發送端口與外部設備通信。

2.2 SRIO操作實現

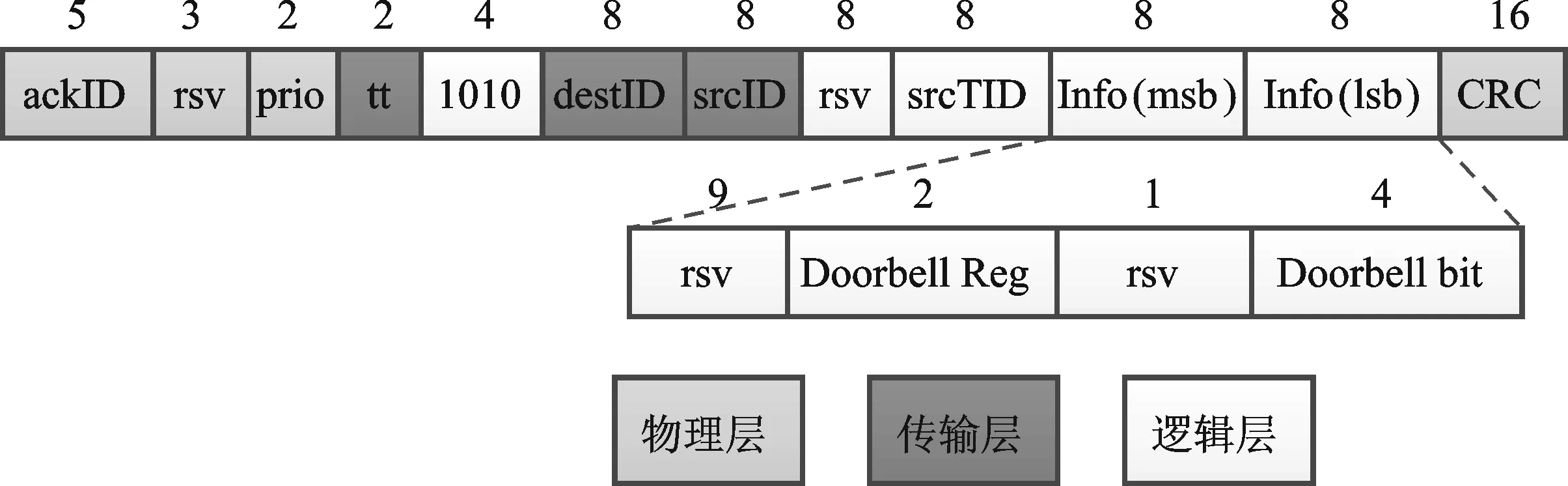

SRIO操作是通過包的傳輸完成的。在C6678中關于SRIO的操作主要分為DirectI/O和Doorbell這兩大類。通過對LSU寄存器進行配置,從而完成操作。DirectI/O包括了NREAD、NWRITE、NWRITE_R、SWRITE、Maintenance Read和Maintenance Write這幾種協議。對于DirectI/O而言,數據傳輸和DMA傳輸是結合的。此DMA為SRIO模塊中的內部引擎,當發起SRIO操作時,DMA將會自行啟動。DirectI/O操作分為主、從兩種模式。當DSP工作在主模式下時,DSP需要知道外部相連器件的ID號以及存儲器地址映射情況,從而發起讀/寫操作。若DSP工作在從模式下,DSP無需知道其他外部芯片的邏輯地址情況,讀寫操作都由主設備發起,通過DMA完成。Doorbell 協議包不包含數據負載,是一種用于器件間響應中斷的協議,如圖4所示。

圖4 Doorbell包結構

在Doorbell操作中,存在著一個Drbll_Info的結構,Drbll_Info分為16位,由Doorbell的發送方置位。Doorbell的接收方可以在中斷服務程序中,讀取ICCR寄存器的值,此時ICCR中的值會根據 Drbll_Info的值,在相應的位上進行置位。這樣通過 Drbll_Info便可以發送不同的指令。

TMS320C6678的SRIO模塊設計以寄存器為基礎,通過調用TI公司軟件開發工具PDK中的底層庫(CSL)驅動和SRIO模塊驅動進行程序設計。SRIO模塊的驅動程序初始化按以下步驟設置[3-4]:

① 端口使能:使能內部發送(LSU,TXU)與接收(MAU,RXU)模塊。

② SerDes初始化:參考時鐘以及傳輸速度初始化,相連器件間需要配置相同的參考時鐘,傳輸速度有1.25 Gbps、2.5 Gbps、3.125 Gbps和5 Gbps。

③ 傳輸模式初始化:Lane可以配置為1x、2x或4x,設置鎖相環PLL和設備ID。

④ 中斷初始化:初始化Doorbell中斷,將其映射到核內中斷向量上。

按照上述步驟完成配置后,在SRIO接收到Doorbell中斷時,接收DSP即跳入中斷服務程序,完成門鈴響應。

3 性能測試

本節對SRIO傳輸的性能進行實測評估,并提供在不同的操作條件下獲得的性能測試數據。大部分測試是在最理想的測試條件進行,以評估可以獲得的最大吞吐量。處理器運行的頻率設置為1 GHz,DDR配置成64位,位寬1333 M,采用的編譯環境是TI公司的CCSv5.0。

圖5 SRIO的傳輸帶寬

圖5表述SRIO在不同類型的存儲空間之間的傳輸速率隨著數據塊的增大,一直呈現上升趨勢。

表1是DSP核以DirectI/O模式的SWRITE方式通過SRIO從本地LL2、SL2和DDR3分別訪問遠端LL2、SL2和DDR3,每次發送數據量為8 KB,發送多次取平均所得的傳輸帶寬。由于SRIO本身具備硬件糾錯功能,當檢測到數據傳輸錯誤后會自動重傳,造成帶寬的損耗,另外,背板的硬件電氣特性也會直接影響到實測的帶寬,這些因素均會造成實測帶寬與理論帶寬的差距。

表1 DSP核通過SRIO實現8 KB數據傳輸帶寬

結 語

[1] Texas Instruments Inc.Multicore design overview,2011.

[2] Sam Fuller.RapidIO:The embedded system interconnect[M].Hoboken:John Wiley&Sons,2005.

[3] Texas Instruments Inc.TMS320C6678 data manual,2011.

[4] Texas Instruments Inc.KeyStone Architecture Serial RapidIO User Guid,2012.

盧建章(工程師),主要研究方向為雷達信號處理、嵌入式信號處理系統;劉洋(工程師),主要研究方向為信息安全。

Research on High-speed Serial Interface RapidIO in TMS320C6678

Lu Jianzhang1,Liu Yang2

(1.AVIC Leihua Electronic Technology Research Institute,Wuxi 214063,China;2. Jiangnan Computing Technology Research Institute)

Based on the application of high-speed data communication between embedded multi-core processors and the knowledge of TMS320C6678 multi-core DSP,the research on RapidIO interface protocol and TMS320C6678 SRIO module structure is carried out.The detailed configuration process of SRIO communication between TMS320C6678 chips is achieved,and its communication performance is analyzed and evaluated.It provides some reference for multi-core DSP system-level communication design.

TMS320C6678;RapidIO;inter-processor communication

TN915.04

A

?士然

2017-02-13)