用于2.5D封裝技術的微凸點和硅通孔工藝

周 剛,曹中復

(中國電子科技集團公司第四十研究所,沈陽110032)

用于2.5D封裝技術的微凸點和硅通孔工藝

周 剛,曹中復

(中國電子科技集團公司第四十研究所,沈陽110032)

過去幾十年里,微電子器件尺寸按照摩爾定律持續減小,已經進入到真正的納米時代。盡管集成電路的特征尺寸已經進入20nm之下,但是在特定領域,尤其是存儲器、FPGA等對資源要求極高的領域,僅僅依靠摩爾定律已經不能滿足市場需求。市場永無止境地對在可控功耗范圍內實現更多的資源以及更高的代工廠良率提出迫切要求。針對一種新的2.5D封裝技術,介紹了其中使用的微凸點(microbump)和硅通孔(through-silicon vias,TSV)等兩項關鍵工藝,并進行了分析。

硅通孔;堆疊硅互連;微凸點;凸點下金屬化層;封裝;電沉積

1 引言

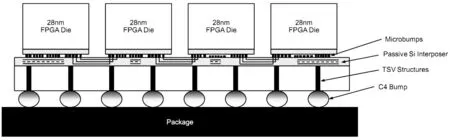

3D封裝作為目前國內外比較熱門的研究領域,有很多研究機構都在開展相關研究,而真正產業化的應用并不多見,目前主要集中于存儲器的生產。業界將多個不同芯片并排堆疊的技術稱為2.5D封裝,如FPGA廠商賽靈思2011年發布的堆疊硅片互聯(SSI)技術就是典型的2.5D封裝技術。該技術將四個不同的FPGA芯片在無源硅中介層上并排互聯堆疊,構建了相當于容量達2000萬門ASIC的可編程邏輯器件。

圖1 XILINX的2.5D封裝示意圖

通過圖1的XILINX的2.5D封裝示意圖可以看出,該結構包括微凸點(microbump)、硅通孔(through-silicon vias,TSV)、無源硅介質(Passive Si interposer)和C4 BUMP。這類新的2.5D封裝技術區別于以往的特點在于微凸塊和硅通孔等技術的共同應用,各芯片通過微凸塊引出信號,多塊芯片通過無源硅介質(Passive Si interposer)實現互連,硅通孔技術和C4 BUMP實現基板封裝。論文后續部分將分別對微凸點(microbump)和硅通孔(through-silicon vias,TSV)這兩項工藝進行研討。

2 微凸點(m i crobum p)工藝介紹

同黏著鍵合、金屬/焊料微凸點鍵合、直接氧化物鍵合、陽極鍵合和玻璃介質鍵合等鍵合技術相比,微凸點鍵合(如圖2所示)由于既可以作為結構支撐也可以作為疊層間的電氣互連線[1],具有易于實現高可靠性低溫互連等優勢而倍受關注。微凸點工藝來源于BGA形式,BGA形式封裝1980年由富士通公司提出,在日本IBM公司與CITIZEN公司合作的OMPAC芯片中誕生[2]。隨著電路規模的發展,BGA逐漸不能滿足電子產品向更小型、更多功能、更高可靠性發展的要求,更不能滿足硅集成技術發展對進一步提高封裝效率和進一步接近芯片本征傳輸速率的要求[3]。在這種背景下,日本富士通公司又提出了芯片級封裝(CSP)。其結構與BGA結構基本一樣,錫球直徑和球中心距縮小,這樣在相同封裝尺寸時可容納更多的I/O數,使組裝密度進一步提高。隨著三維封裝的發展,研究者根據前面幾種封裝形式的一些思路提出了微凸塊工藝并予以實現。

圖2 微凸塊鍵合示意圖

根據具體需求,純金屬(Au,Cu,Sn,In等)、共晶或者高熔點合金(PbSn,AuSn,AgSn,SnCu,AgSnCu等)均可用來制作微凸點。不過目前無鉛化成為業界選擇凸點材料的普遍共識。

目前主要的微凸點制作方法包括:電沉積(electrodepositing)、絲網/模版印刷(screen/stencil printing)、焊料噴射(solder jetting)、C4NP、置球(placing performed solder spheres)、釘頭凸點(stud bumping)以及蒸發(evaporation)等。

根據穩定性和精度要求,電沉積方法較適合制作本文中的微凸點。電沉積方法采用光刻掩膜技術通過電沉積來獲得形狀尺寸精確的凸點,該技術由Hitachi開發并首先提出[4]。電沉積相對進程比較慢,根據沉積材料的不同,沉積速率從每分鐘0.2微米至幾微米不等。電沉積技術可以采用恒電位(Potentiostatic)、恒電流(Galvanostatic)以及脈沖(Pulse)方式進行。晶圓表面電場分布決定了實際沉積電流,因此在電沉積過程中是影響凸點高度、焊料成分和表面形貌均勻性的最關鍵因素。為保證晶圓表面電場分布均勻,電壓應該施加在晶圓圓周的多點上。除此以外,電沉積面積與晶圓面積的比率以及晶圓表面凸點分布的均勻性也會影響沉積電流的均勻性。電沉積方法可以精確復制光刻膠圖案,并且適用于不同尺寸的晶圓,不同的鈍化材料以及不同的光刻圖案。所有的半導體材料(如硅、SiGe、GaAs、InP等)以及陶瓷和石英基底都可以用電沉積方法來制作凸點。

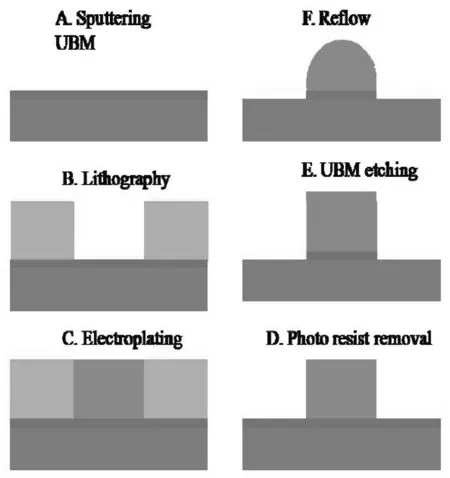

如圖3所示電沉積方法制備凸點的基本流程包括:濺射凸點下金屬化層(UBM,Under Bump Metallization)、形成光刻圖案、電沉積凸點、去除光刻膠以及UBM刻蝕。

第一步是在晶圓表面濺射UBM層;

第二步,旋涂光刻膠,接下來對光刻膠進行曝光刻蝕;

第三步,在圖案中沉積金屬或焊料;

第四步,去除光刻膠;

第五步,刻蝕凸點之間的UBM層。

第六步,進行回流,使焊料變成球狀,并在焊料與UBM界面處形成金屬間化合物。

圖3 電沉積法制作凸點流程圖

電沉積方法可以方便地制備純金屬凸點以及一些析出電位接近的二元甚至三元合金焊料。但是采用含有多種金屬離子的鍍液制備合金焊料時往往得到的凸點成分不均勻,利用二步法可以解決這一問題,即采用先沉積一種金屬而后再沉積另一種金屬,最后對得到的凸點進行退火來得到成分均勻的合金焊料。利用二步法還可以制備一些因沉積電位相差很遠而不能在單一鍍液中制備的合金凸點。

利用電沉積方法制作小尺寸凸點,首先要保證鍍液完全潤濕光刻微孔,而由于光刻膠潤濕較差等諸多因素,這一點并不容易實現。不完全的潤濕會導致氣泡殘留在光刻微孔中致使最終制備的凸點內部含有孔洞以及凸點體積不一致。現有的技術水平可提供真空浸漬、表面改性、鍍液中添加潤濕劑等手段改善鍍液在光刻微孔中的潤濕性能。

3 硅通孔((t hrough-si l i con vi as,TSV)工藝介紹

相比于其他3D封裝技術,TSV技術具有四方面的優勢[5-6]:

(1)能提供更短的電路連接,大幅提高信號的傳輸速度;

(2)能實現高密度、高深寬比連接,擁有更多的信號通道;

(3)能替代效率低下的引線鍵合方式,使信號傳輸速度更快、功率消耗更少,同時,可以保證傳遞功率的一致性;

(4)能使高密度堆疊成為可能,擁有更高的封裝密度,有效降低成本。

因此,TSV封裝技術是整個電子封裝產業的技術主流,更多的研究機構和封裝公司已將TSV技術看作IC(IntegrityCircuit)互連危機的一種解決方案,也被譽為繼引線鍵合(WB,Wire Bonding)、載帶鍵合(TAB,Tape Automated Bonding)和倒裝芯片(FC)之后的第四代封裝技術[7]。

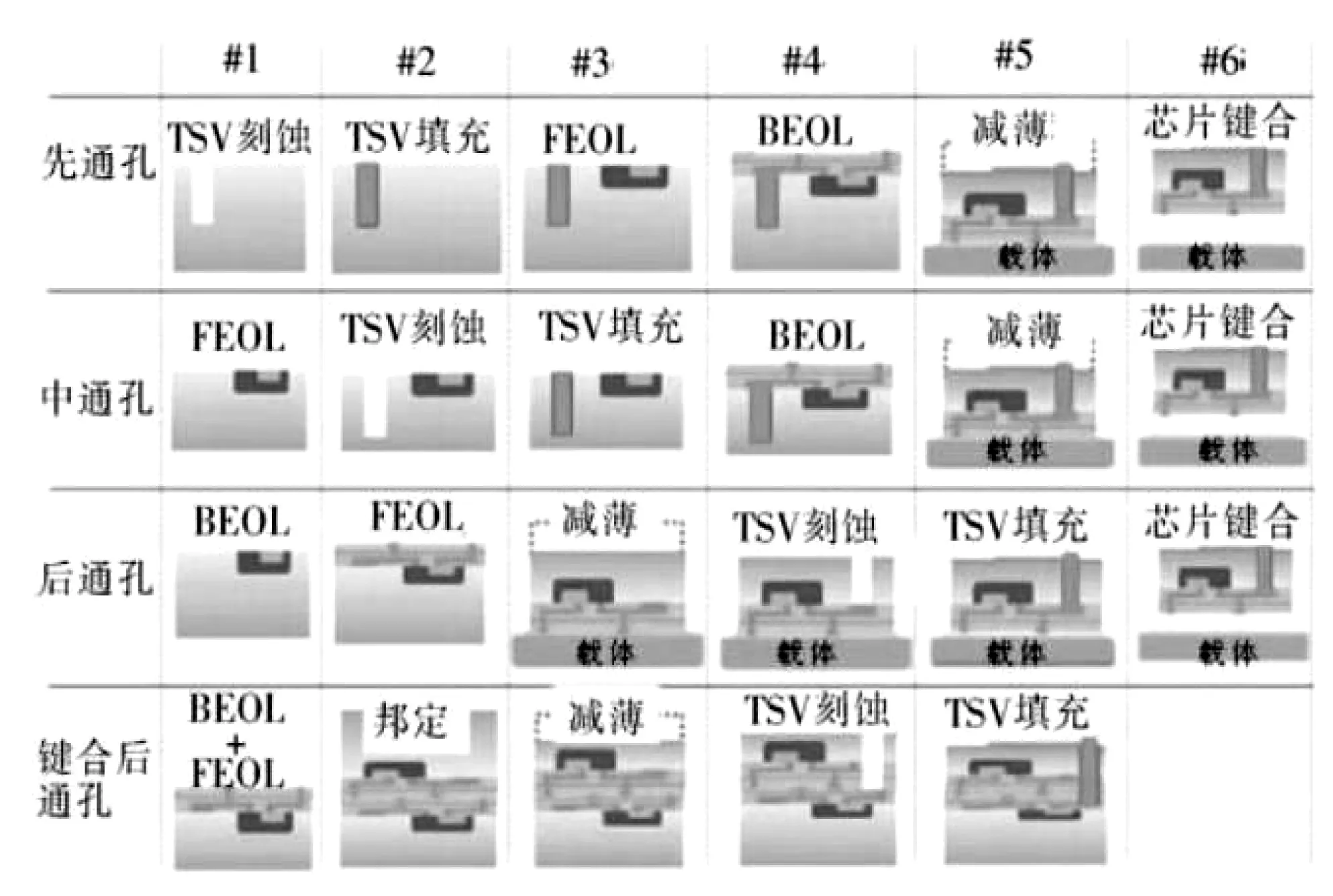

按照通孔制作在整個工藝流程中所處的時間點不同,TSV集成方式可以分為以下四類[5]:

先通孔工藝:CMOS之前制作硅孔;

中通孔工藝:在CMOS和BEOL(Back End of Line)之間制作硅孔;

后通孔工藝:在BEOL之后制作硅孔;

鍵合后通孔工藝:在硅片減薄、鍵合后制作硅孔。

四種3D-TSV集成方式的工藝流程圖如圖4所示[9]。

圖4 四種不同的TSV集成方式工藝流程圖

后面對減薄技術、通孔工藝這兩個TSV主要工藝步驟進行簡要介紹。

減薄目前比較主流的做法是一體化減薄,即將硅片的機械打磨、拋光、保護膜的去除和粘貼劃片膜等工藝集合在一臺設備之內。利用精密的機械式傳送系統,硅片從開始打磨一直到粘貼劃片膜為止始終被吸在真空吸盤上,這樣能夠有效保持硅片的平整,也給硅片提供了支撐。當硅片被粘貼到劃片膜上后,硅片會順從劃片膜的形狀從而保持平整,不會再發生翹曲、斷裂等問題,使后續工藝可以有效進行,保證了產率。

比較成熟的通孔制作工藝步驟如下:

(1)通過深層離子反應刻蝕(DRIE)或激光在硅片上刻蝕出通孔;

(2)通過PECVD工藝淀積絕緣層;

(3)通過PVD、PECVD或MOCVD工藝淀積金屬粘附層/阻擋層/種子層;

(4)通過化學電鍍的方法在硅通孔中填充銅金屬;

(5)通過化學機械拋光工藝對硅片進行減薄露出硅通孔另一端。

在整個硅通孔((through-silicon vias,TSV)工藝中減薄和通孔制作這兩個步驟關系TSV工藝的質量,應持續開展研究。

根據ITRS預測[8],TSV封裝技術,將在硅孔直徑、硅晶圓厚度、孔間引腳間距、垂直方向堆疊層數等方面,繼續向更加微細化的方向發展。預測顯示,TSV的硅孔直徑將由4微米縮小到1.6微米,引腳間距將由10微米縮小到3.3微米,垂直方向上的堆疊層數將由5層上升到12層,減薄(Wafer Thinning)的硅晶圓厚度將由40微米進一步縮小到8微米。

4 結束語

首先對 2.5D封裝技術采用的微凸點(mi-crobump)工藝進行介紹,列舉了電沉積、絲網/模版印刷、焊料噴射、C4NP、置球、釘頭凸點以及蒸發等制作方法,重點介紹了適用于微凸點工藝的電沉積方法及其具體流程。接著對TSV工藝及其分類進行了介紹,并對TSV工藝中的主要工藝步驟——減薄技術、通孔工藝進行了論述。通過對微凸點工藝和TSV工藝的掌握,我們可結合其他工藝將其應用于大規模FPGA、大容量存儲器等大尺寸、高密度電路的實現。

[1]羅馳,練東,電鍍技術在凸點制備工藝中的應用[J].微電子學,2006,36(4):467-472. LUO Chi,LIAN Dong,Application of Electroplating Technology to Solder Bumping Formation[J].Microelectronics, 2006,36(4):467-472.

[2]葉冬,劉欣,劉建華,曾大富,芯片級封裝技術研究[J].微電子學,2005,35(4):349-356. YE Dong,LIU Xin,LIU Jian-hua,ZENG Da-fu.A Study on Chip Scale Package Technology[J].Microelectronics, 2005,35(4):349-356.

[3]K.N.Tu.Reliability challenges in 3D IC packaging technology[J].Microelectronics Reliability,2011,51(3):517-523.

[4]TKawanobe,KMiyamoto,Y Inaba.Solder Bump Fabrication by Electrchemical Method for FE Interconnection[J].IEEE Publication CH1671-7/0000,1981:149.

[5]吳向東.三維集成封裝中的TSV互連工藝研究進展[J].電子與封裝,2012,12(9):1-5. WU Xiang-dong.Research Status of Through-Silicon Via Interconnection for 3DIntegration Technology[J].ELECTRONICS&PACKAGING,2012,12(9):1-5.

[6]蔡積慶.導通孔電鍍銅填充技術[J].印制電路信息,2012 (5):28-32. CAI Ji-qing,Copper plating via filling technology[J].Printed Circuit Information,2012(5):28-32.

[7]朱健,吳璟,賈世星,姜國慶.基于MEMS圓片級封裝/通孔互聯技術的SIP技術 [J].固體電子學研究與進展,2011,31(2):213. Zhu Jian,Wu Jing,Jia Shixing,Jiang Guoqing.3D SIP by WLP/TSV[J].Research&Progress ofSSE Solid State Electronics,2011,31(2):213.

[8]Feng Z V,Li X,Gewirth A A.Inhibition due to the interaction of polyethylene glycol,chloride,and copper in plating baths:A surface-enhanced Raman study[J].The Journal of Physical ChemistryB,2003,107(35):9415-9423.

[9]鄧丹,吳豐順,周龍早,劉輝,安兵,吳懿平.3D封裝及其最新研究進展[J].微納電子技術,2010,47(7):443-450. Deng Dan,Wu Feng-shun,Zhou Long-zao,Liu Hui,An Bing,Wu Yi-ping.3D Package and Its Latest Research[J]. Micronanoelectronic Technology,2010,47(7):443-450.

Technics of Microbump and TSV for 2.5D Package Technology

Zhou Gang,Cao Zhongfu

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Over the past decade,the micro-electronics device's size continuously scaled down according to Moor's Law,and had already got into a real nano ages.Though the characteristic size of integrated circuits has already got under 20nm,but in such particular fields as memory,FPGA,etc., Moor's Law can't meet the request of market which always makes an urgent request for more resource and higher foundary yield within the controllable power.Microbump and TSV as two key technologies applied to a new 2.5D package technology are discussed and analyzed in this paper.

TSV;SSI;Microbump;UBM;Package;Electrodepositing

10.3969/j.issn.1002-2279.2017.02.004

TN911

A

1002-2279-(2017)02-0015-04

周剛(1978-),男,遼寧省法庫縣人,高級工程師,工學學士,主研方向:集成電路設計方向,目前關注領域,集成電路3D封裝、可靠性設計、可編程器件。

2015-11-04