基于FPGA的LFM信號匹配濾波的時域實現*

張唯,楊維明,沈怡彥,趙楠博,彭菊紅,周民

(湖北大學計算機與信息工程學院,武漢430062)

基于FPGA的LFM信號匹配濾波的時域實現*

張唯,楊維明*,沈怡彥,趙楠博,彭菊紅,周民

(湖北大學計算機與信息工程學院,武漢430062)

為解決頻域法實現信號匹配濾波時硬件開銷較大的問題,采用時域法實現線性調頻(LFM)信號的匹配濾波。設計了一款針對LFM信號的8階分布式結構的時域匹配濾波器;利用FPGA的ROM宏模塊構建查找表,實現分布式濾波算法;基于FPGA器件完成了濾波器的設計與集成。仿真結果顯示,濾波器占用170個邏輯單元、109個寄存器、3 kbyte存儲器,邏輯資源開銷較小。與傳統FIR結構的乘累加算法相比,分布式濾波算法運算速度更快。

匹配濾波器;時域實現;FPGA;線性調頻信號;分布式算法

在線性調頻(LFM)脈沖壓縮雷達系統中,發射端采用線性調頻脈沖時,其回波信號一般要經過匹配濾波完成脈沖壓縮后,再進行后續的信號處理[1]。匹配濾波處理分為時域卷積法和頻域FFT法兩種方式。頻域法實現時速度較快,但頻域法要多次用到快速傅里葉變換(FFT)和逆快速傅里葉變換(IFFT),硬件實現開銷較大;采用時域法實現時電路結構簡單,為了提高系統的運算速度,本文采用分布式結構的濾波器完成線性調頻信號的匹配濾波,分布式濾波算法(DA)在實現乘累加運算時,將每一組輸入數據的各對應位與系數相乘形成部分積進行預先相加,再對各部分積進行累加,形成最終結果,而傳統FIR結構的乘法累加運算是等到全部的乘積產生之后,最后再相加來完成乘加運算功能。與傳統的乘累加算法相比,分布式濾波算法能減小FPGA邏輯資源和存儲資源開銷,提高系統的可靠性和運算速度。

1 分布式濾波器設計原理

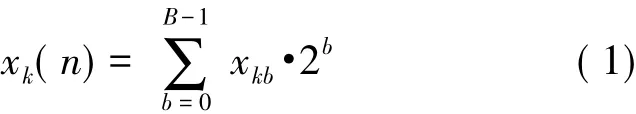

分布式濾波算法(DFA)在實現乘累加運算時,將每一組輸入數據的各對應位與系數相乘形成部分積進行預先相加,再對各部分積進行累加,形成最終結果;而傳統FIR結構的乘法累加運算是等到全部的乘積產生之后,最后再相加來完成乘加運算功能。與傳統的乘累加算法相比,分布式算法能大大減少FPGA存儲器資源的消耗,提高系統的運算速度[2]。分布式濾波算法推導過程如下:設Ak是濾波器系數,Xk(n)是輸入變量,可以看作第n次采樣的第k個輸入數據,y(n)為對應的系統響應:式中,B為數據位寬,xkb為輸入變量的二進制的k位,于是:

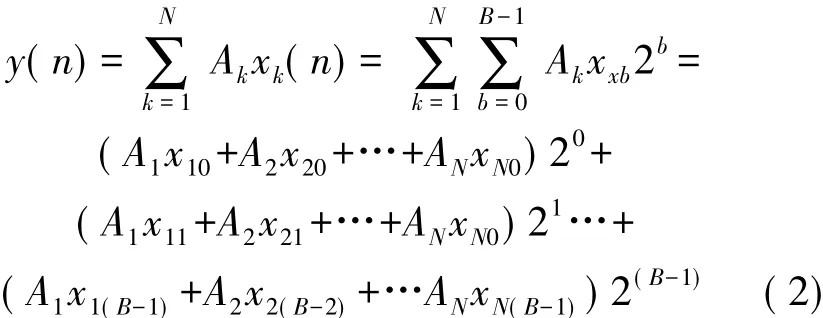

圖1所示是分布式濾波器的硬件實現框圖,圖中,N表示濾波器階數。

圖1 分布式濾波器結構框圖

利用查找表(LUT)實現映射關系,各個映射結果都由相對應的二次冪加權累加而成,此時利用移位加法器就能夠實現累加了[3]。在FPGA中乘法器會占用大量的邏輯資源,DFA只使用加法器沒有用到乘法器,它采用ROM存儲器實現乘法運算,消耗的硬件資源較少,且容易實現流水線處理,提高電路的執行速度[4]。

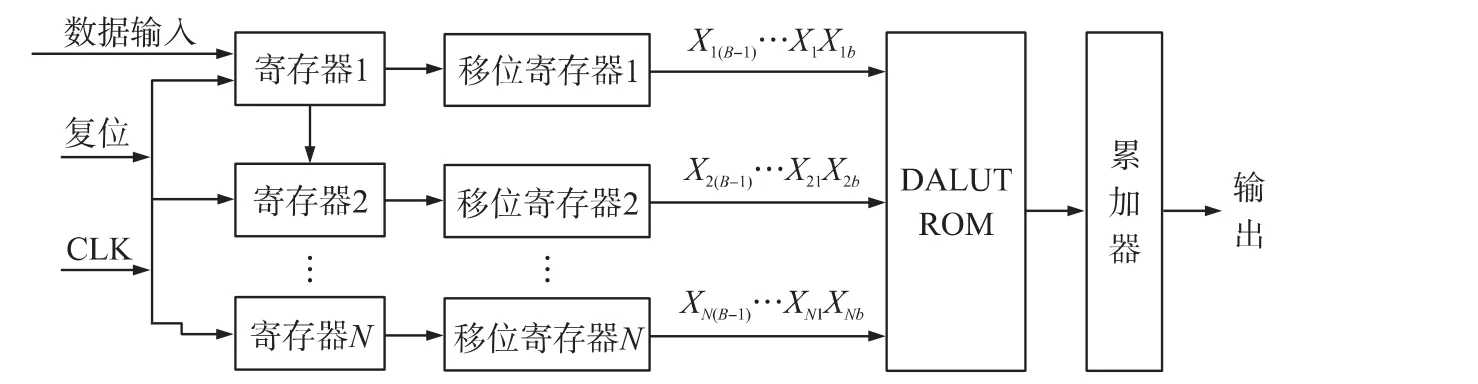

由于查找表的乘積部分需要大容量的存儲器,這就要求占用較多的資源,增加了功耗,降低了運算速度,此時,為了減小設計規模,可以將一個大的查找表分為幾個小的來實現。八位地址x(i)=xb[7]xb[6]xb[5]xb[4]xb[3]xb[2]xb[1]xb[0]相對應查找表如表1所示。

表1 分布式濾波器地址映射關系表

2 線性調頻(LFM)信號匹配濾波器設計與實現

2.1 線性調頻(LFM)信號匹配濾波

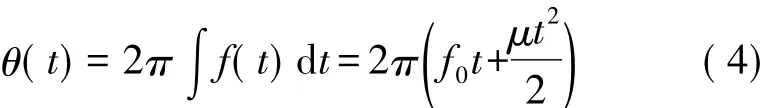

線性調頻信號的信號頻率對于時間的導數應為常數[5],即:

式中,f(t)是瞬時頻率,μ是調頻斜率,得到的相應瞬時相位函數為:時間寬度為T的LFM信號表達式:時間寬度T的復數信號:

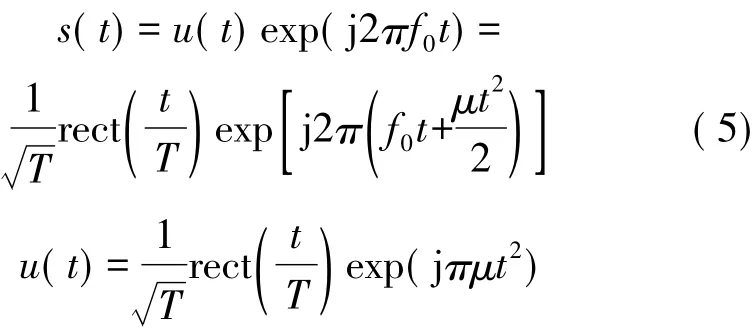

設線性調頻信號脈沖寬度為10μs、頻帶寬度為30 MHz,在線性調頻信號中加入高斯白噪聲,設信噪比SNR為10 dB。MATLAB仿真波形如圖2所示。

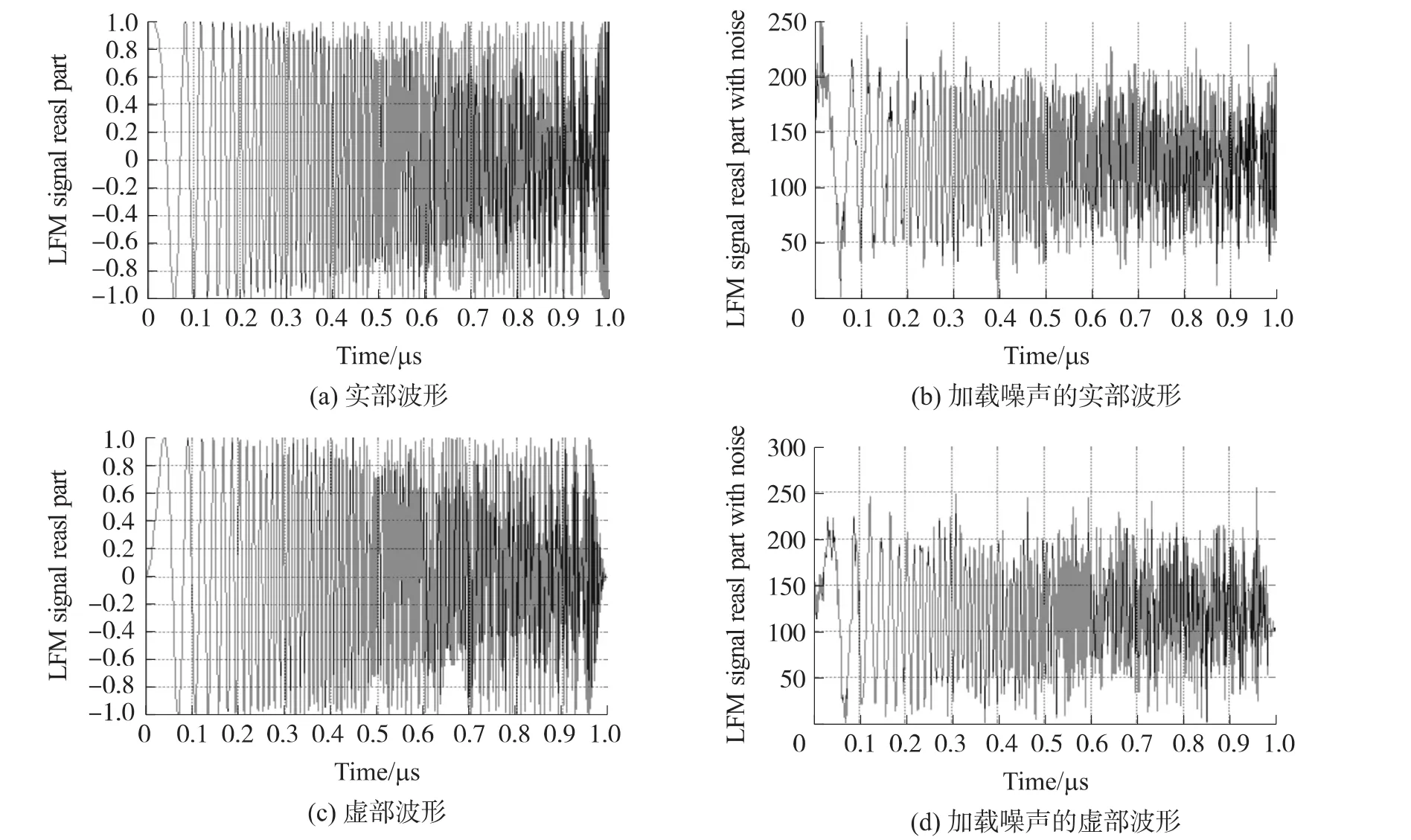

本文的匹配濾波器由MATLAB中的fdatool進行設計,以給出的線性調頻信號實部為例,設計出8階濾波器系數如下:

圖2 線性調頻信號仿真波形

由于得到的系數均為介于[-l,1〕區間的浮點數,而FPGA上只能進行定點數乘法,故將生成的FIR系數量化為整數[6],從而得到本系統設計的8階濾波器系數分別為:h(0)=9,h(1)=49,h(2)=168,h(3)= 286,h(4)=286,h(5)=168,h(6)=49,h(7)=9。

2.2 分布式匹配濾波器實現

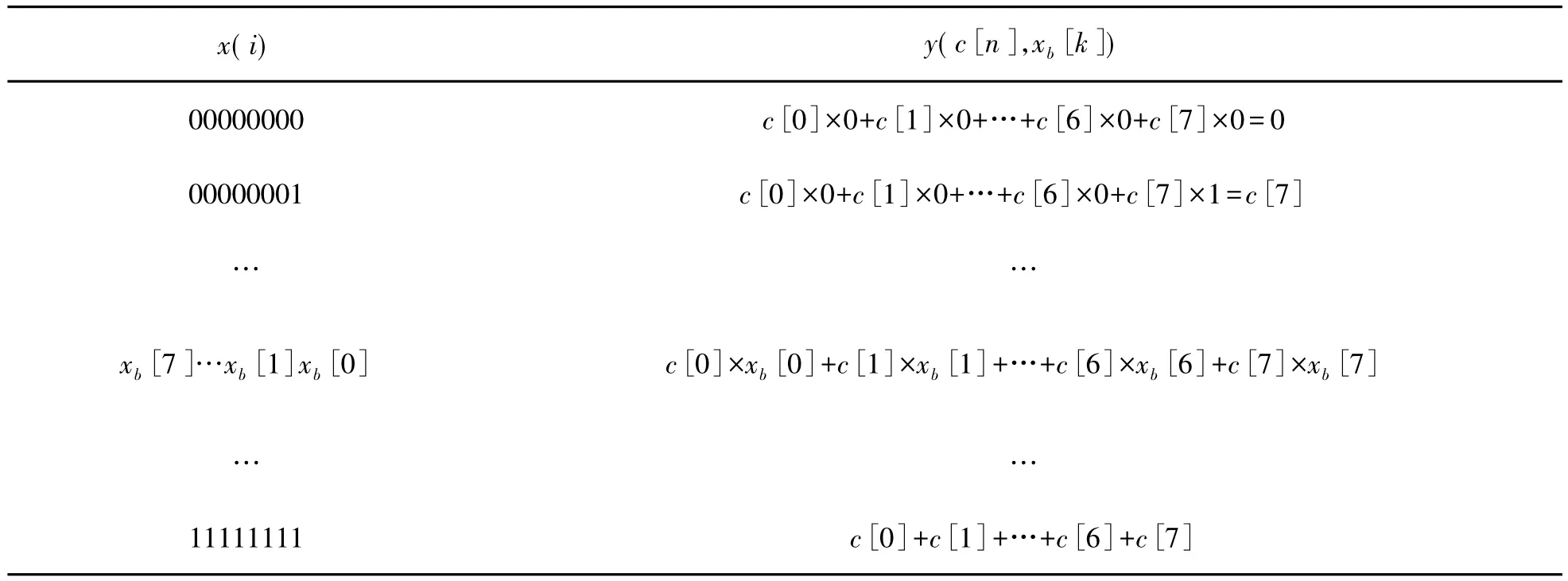

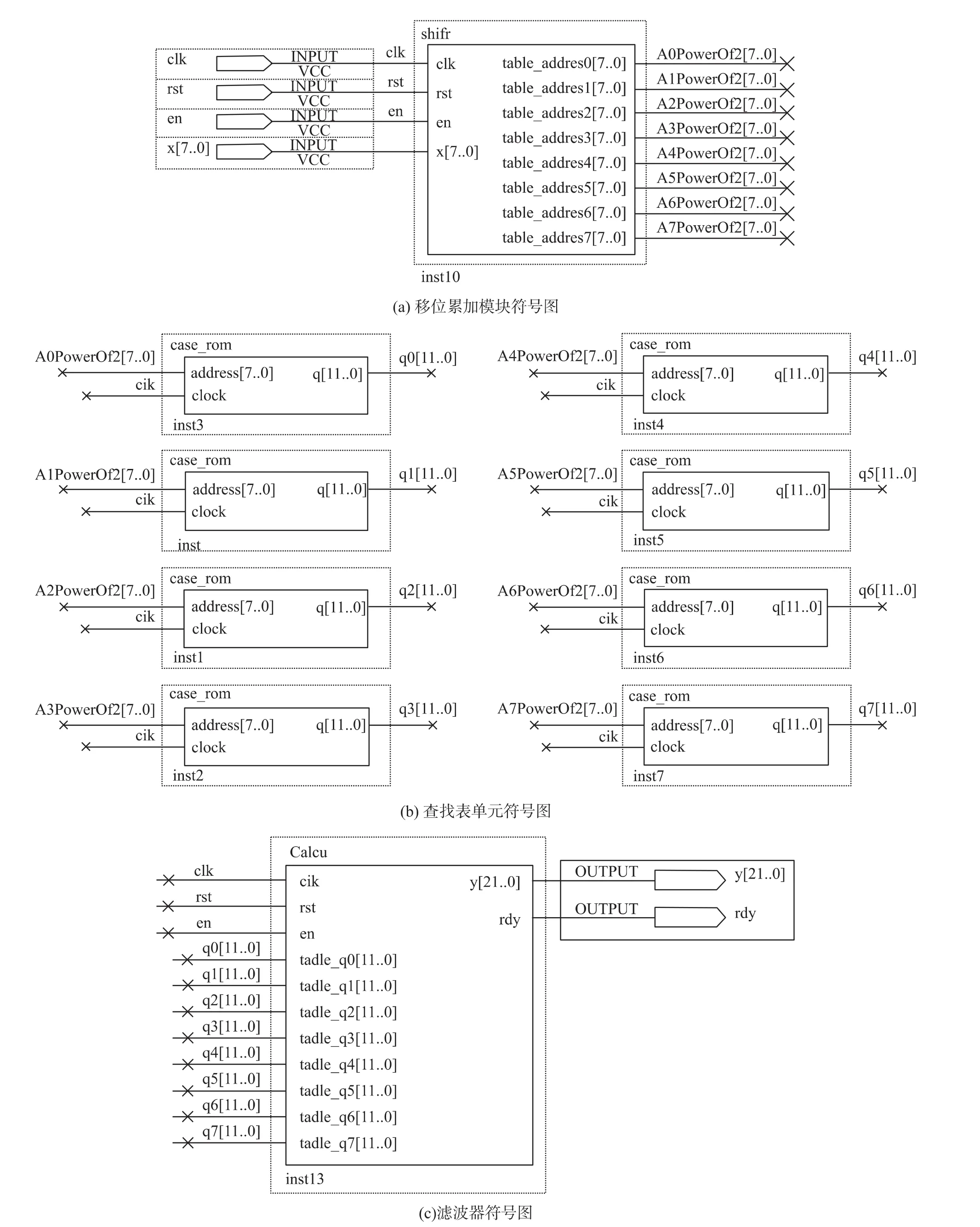

8階FIR濾波器主要由移位寄存器、查找表以及累加器組成,查找表中有256個存儲單元,隨著濾波器階數的增加,查找表規模按指數遞增,因此在實現階數較高的濾波器時可采用分割查找表的方式來節省存儲資源[6-7]。在完成8階FIR濾波器如果采用的是有符號數據的運算時;在完成數據的計算(如輸入、串/并轉換、查找表和加權累加)時,需要考慮到累加最高位運算符號;在用FPGA設計時,查找表模塊的實現較為關鍵[7-8]。8個查找表單元分別由8個ROM實現,ROM存放的是信號00000000~11111111與濾波器系數(9,49,168,286,286,168, 49,9)卷積的結果,輸出Y(補碼形式)即為濾波器的輸出結果。在QUARTUS仿真平臺上設計的主要模塊符號圖如圖3所示。

2.3 QuartusⅡ仿真結果

上述FIR濾波器邏輯電路采用ALTERA公司FPGA器件EP4CE6E22A7進行設計集成,通過在QuartusⅡ平臺加載modelsim-Altera 14.0進行仿真,仿真輸入數據為圖2的LFM信號,仿真輸出結果如圖4所示,由圖可知,輸出結果濾除了高斯噪聲,與輸入的LFM信號波形相匹配;仿真結果顯示,該濾波器占用170個邏輯單元、109個寄存器、3 kbyte存儲器。

圖3 QUARTUS平臺設計的主要模塊符號圖

3 結束語

結合verilog語言和QuartusⅡ平臺,采用FPGA成功實現了針對LFM信號的分布式結構的時域匹配濾波器。分布式結構的乘累加算法與傳統FIR結構的乘累加算法相比較,大大降低了運算量,提高了執行效率;與頻域實現的匹配濾波器相比,時域匹配濾波器硬件開銷大幅減少,成本明顯降低。若對匹配濾波后的信號采取加窗處理,系統的性價比還可進一步提升。

[1]丁智泉.線性調頻信號的脈沖壓縮系統設計與FPGA實現[D].成都:電子科技大學,2007:1-30.

[2]程遠東,鄭晶翔.一種用于數字下變頻的高階分布式FIR濾波器及FPGA實現[J].北京:電子技術應用,2011,37(2):57-59.

[3]崔亮,張芝賢.基于FPGA設計的FIR濾波器的實現與對比[J].西安:電子設計工程,2012,20(20):168-170.

[4]魏靈,楊日杰,崔旭濤.基于分布式算法的數字濾波器設計[J].北京:儀器儀表學報,2008,29(10):2100-2104.

[5]朱雙兵,楊維明,吳恙.基于CORDIC算法的線性調頻信號產生[J].電子器件,2013,36(4):497-501.

[6]王旭東,潘明海.數字信號處理的FPGA實現[M].第1版.北京:清華大學出版社,2011:92-108.

[7]王一海,俞筱楠,姜志鵬.并行分布式算法FIR濾波器的FPGA實現[J].電子器件,2012,35(5):545-548.

[8]謝海霞,孫志雄.可編程FIR濾波器的FPGA實現[J].電子器件,2012,35(2):233-235.

張唯(1991-),女,漢族,湖北武漢人,湖北大學電子與通信工程專業碩士研究生,主要研究方向為數字信號處理,wh_zhangwei@163.com;

楊維明(1969-),男,漢族,湖北赤壁人,博士,教授,湖北大學計算機與信息工程學院碩士生導師,主要研究方向為電路與系統,20040416@hubu.edu.cn。

Implementation in Time Domain on LFM Signal M atched Filter based on FPGA*

ZHANGWei,YANGWeiming*,SHEN Yiyan,ZHAO Nanbo,PENG Juhong,ZHOU Min

(Faculty of Computer and Information Engineering,Hubei University,Wuhan 430062,China)

To solve the problem that the signalmatching filter hardware overhead is largewhen realized in frequency domain,the time domain method was used to realize thematching filter of linear frequencymodulated(LFM)signal in this paper.A 8th-order distributed filter is designed for the given LFM signal.The lookup table(LUT)was built to realize the distributed filter algorithm by using ROM macro-module of FPGA.The logic circuit of the filter was designed and integrated in FPGA device.The simulated results indicate that the filter consumes 170 logic cells,109 registers and 3 kbyte memory.The logic expense is small.Moreoever,the operation speed of the distributed multiply-accumulate algorithm is faster than the traditional one.

matched filter;implement in time domain;FPGA;linear frequency modulation signal;distributed algorithm

C:1270

10.3969/j.issn.1005-9490.2017.01.013

TN713

:A

:1005-9490(2017)01-0066-05

項目來源:湖北大學國家級大學生創新實驗訓練項目(201310512029)

2016-02-05修改日期:2016-03-19