晶振失效故障分析

文/張富堯

晶振失效故障分析

文/張富堯

本文通過對無輸出晶振的失效分析,確定了失效原因。由于該晶振內(nèi)部鎖相倍頻集成芯片性能不良導(dǎo)致。使用有延時(shí)的DC-DC電源對晶振進(jìn)行加電測試,發(fā)現(xiàn)失效問題,可在早期解決這一問題。

晶體振蕩器 振蕩電路 鎖相倍頻芯片

1 引言

50MHz溫補(bǔ)晶振在隨模塊試驗(yàn)時(shí),出現(xiàn)常溫上電偶有無輸出的故障,對模塊進(jìn)行反復(fù)測試,發(fā)現(xiàn)晶振偶有無輸出的情況發(fā)生,故障復(fù)現(xiàn)。

2 故障定位

2.1 晶振復(fù)測情況

2.1.1 晶振單獨(dú)測試

為了對故障晶振無輸出的現(xiàn)象進(jìn)行準(zhǔn)確分析定位,對從模塊電路板上取下的晶振進(jìn)行了單獨(dú)故障復(fù)現(xiàn)試驗(yàn)。在常溫下通過對晶振單獨(dú)進(jìn)行多次加電測試,未出現(xiàn)晶振無輸出的情況。進(jìn)一步改變晶振的負(fù)載(使用50Ω負(fù)載)以及電源(使用2.7V和3.9V電源電壓),多次加電測試,故障晶振也未出現(xiàn)無輸出的情況。隨后,使用S&A2800晶振自動(dòng)測試系統(tǒng)對故障晶振進(jìn)行了高低溫測試,測試溫度-55℃~+85℃,晶振電性能指標(biāo)測試正常。

2.1.2 晶振在模塊電路中的測試

故障晶振在模塊中,常溫下給模塊多次反復(fù)上電,晶振偶爾出現(xiàn)無輸出的情況,多次上電出現(xiàn)無輸出故障的幾率不到5%。模塊內(nèi)部的3.3V電源在上電時(shí)存在一定的延時(shí)(實(shí)測約為3ms)。而對晶振單獨(dú)上電測試時(shí),采用直流穩(wěn)壓電源進(jìn)行上電試驗(yàn),其上電延時(shí)較小(約為0.5ms),所以問題不能得到復(fù)現(xiàn)。由上述試驗(yàn)可知,故障晶振在3.3V工作電源存在一定延時(shí)的情況下,常溫多次上電偶爾會(huì)出現(xiàn)無輸出的情況。

2.2 故障分析及定位

該晶振采用表貼封裝形式,封裝為SMD7×5×2mm3。內(nèi)部電路主要由3個(gè)部分組成:溫補(bǔ)晶振芯片、鎖相倍頻芯片、SMD石英晶體諧振器。

SMD晶體諧振器(25MHz)與溫補(bǔ)晶振集成芯片連接,產(chǎn)生高精度和高穩(wěn)定度的25MHz頻率信號(hào),鎖相倍頻芯片將25MHz頻率通過鎖相倍頻的方式合成到50MHz,實(shí)現(xiàn)晶振最終的50MHz頻率輸出。晶振的2個(gè)部分集成電路,任意一個(gè)工作不正常均會(huì)對晶振的電性能指標(biāo)造成很大影響甚至造成晶振不工作無輸出的故障。另外如果晶體諧振器參數(shù)漂移,造成晶振起振困難,也會(huì)引起無輸出的故障情況。

晶振各組成部分:兩顆芯片(IC1:溫補(bǔ)晶振芯片;IC2:鎖相倍頻芯片)綁定灌封在基座內(nèi)部;1個(gè)電阻和2個(gè)電容用于信號(hào)耦合以及電源濾波;石英晶體諧振器封裝為SMD6×3.5×1.1mm3,頻率為25MHz。

2.2.1 電連接故障排查

2.2.1.1 外觀檢查

對故障晶振進(jìn)行了外觀檢查,產(chǎn)品表面形貌完整,晶振基座的4個(gè)功能焊盤均未見損傷。通過外觀檢查,可以排除因晶振基座焊盤損壞而造成的晶振無輸出的情況。

2.2.1.2 對晶振進(jìn)行鏡檢

對晶振進(jìn)行了鏡檢。采用40倍放大鏡對晶振表面的各元器件以及各焊點(diǎn)進(jìn)行了檢查,同時(shí)對晶振安裝在模塊上的各焊點(diǎn)進(jìn)行了檢查。通過檢查,晶振表面的晶體、電容、電阻各焊點(diǎn)正常,沒有出現(xiàn)虛焊、漏焊的情況,元器件的焊接滿足工藝要求。同時(shí)晶振在模塊上的焊接點(diǎn)也正常。因此可以排除由于焊點(diǎn)接觸不良造成的晶振無輸出的情況。

2.2.1.3 對晶振進(jìn)行X光檢測

為了排除晶振內(nèi)部芯片鍵合不良的情況,對故障晶振進(jìn)行了X光檢測,檢測其基座內(nèi)部芯片的情況。故障晶振內(nèi)部芯片的各鍵合線均連接良好沒有斷裂或者脫離的情況,可以基本排除由于鍵合線斷裂而造成的晶振無輸出的情況。

2.2.2 晶振內(nèi)部元器件故障的排查

由于晶振內(nèi)部有兩個(gè)集成芯片(溫補(bǔ)晶振芯片和鎖相倍頻芯片),兩個(gè)集成電路的輸出和輸入通過一個(gè)耦合電容連接,所以可以使用高頻探頭對晶振內(nèi)部溫補(bǔ)晶振芯片的輸出信號(hào)進(jìn)行單獨(dú)檢測,以便對元器件進(jìn)行逐一排故。

2.2.2.1 內(nèi)部芯片故障排查

當(dāng)模塊在常溫下反復(fù)上電,晶振故障復(fù)現(xiàn)時(shí),用探頭對晶振內(nèi)部的溫補(bǔ)晶振芯片的輸出端進(jìn)行檢測,測得有25MHz信號(hào)且輸出波形、幅度正常,此時(shí)晶振最終輸出端無50MHz頻率輸出,而50MHz的頻率信號(hào)是由鎖相倍頻芯片輸出的。因此可以判定晶振無輸出是由于倍頻芯片工作不正常造成的,同時(shí)也排除了溫補(bǔ)晶振芯片異常造成的晶振停振的情況。

2.2.2.2 石英晶體諧振器故障排查

輸出端的25MHz頻率信號(hào)是石英晶體諧振器與溫補(bǔ)晶振芯片共同組成的振蕩電路的輸出信號(hào),若25MHz信號(hào)輸出正常則說明石英晶體諧振器參數(shù)正常,可以排除石英晶體參數(shù)異常造成的晶振停振的情況。

2.2.2.3 電源上電延時(shí)引起晶振故障的排查

為了進(jìn)一步驗(yàn)證電源延時(shí)對故障晶振的影響,設(shè)置了一個(gè)具有一定延時(shí)的電源模塊電路板檢測故障晶振多次上電的工作情況。

先使用8ms左右延時(shí)的DC-DC模塊電源供電對故障晶振進(jìn)行測試。在常溫下進(jìn)行20次上電測試,出現(xiàn)了偶有無輸出的情況(幾率約為5%)。

隨后,使用24ms左右延時(shí)的DC-DC模塊電源供電對故障晶振進(jìn)行測試。此時(shí)在常溫下進(jìn)行20次上電測試,出現(xiàn)了偶有無輸出的情況(幾率約為20%)。最后直接使用延時(shí)很小的直流穩(wěn)壓電源(延時(shí)小于0.5ms)對故障晶振供電進(jìn)行上電測試,此時(shí)在常溫下反復(fù)對晶振上電20次,故障晶振沒有出現(xiàn)無輸出的情況。

通過上述電源延時(shí)對故障晶振問題復(fù)現(xiàn)的試驗(yàn),可進(jìn)一步證明:當(dāng)模塊電源延時(shí)較大時(shí)會(huì)造成故障晶振在常溫下多次上電后偶有無輸出的情況,且電源延時(shí)越大故障現(xiàn)象就越明顯。

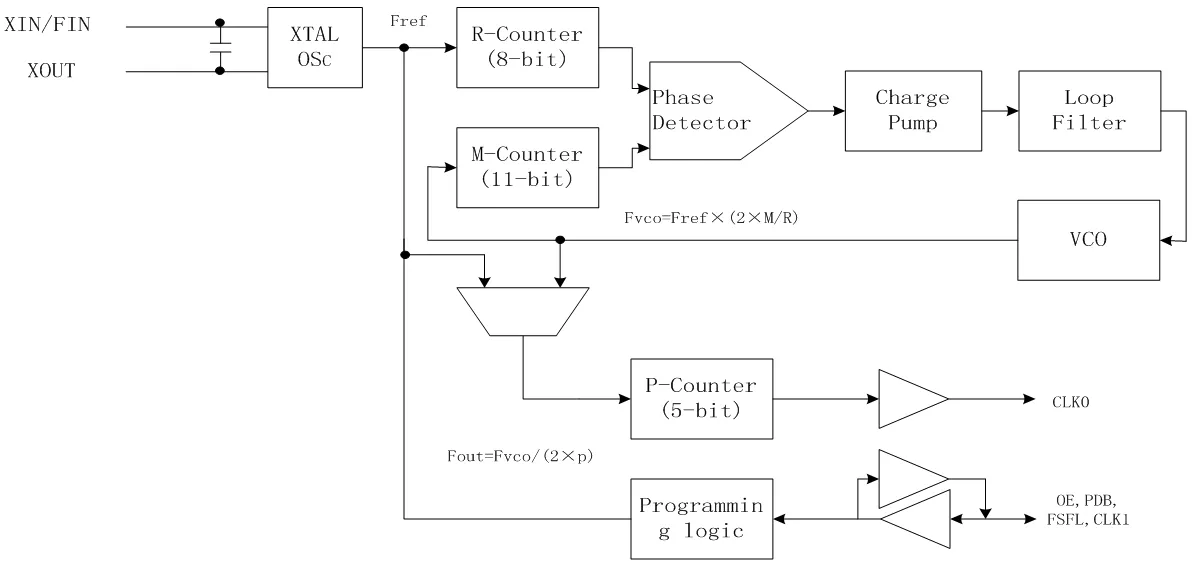

圖1:倍頻芯片的原理框圖

綜上所述,晶振在反復(fù)上電的情況下偶有無輸出的情況是由于內(nèi)部倍頻集成芯片性能缺陷,在上電電壓存在一定延時(shí),反復(fù)上電的情況下有時(shí)不工作,最終導(dǎo)致晶振無頻率輸出。

3 機(jī)理分析

3.1 晶振基本原理

該型號(hào)溫補(bǔ)晶振主要由3個(gè)部分組成:溫補(bǔ)晶振集成芯片、鎖相倍頻集成芯片、SMD晶體諧振器。溫補(bǔ)晶振集成芯片與SMD晶體諧振器(連接,產(chǎn)生高精度和高穩(wěn)定度的25MHz頻率信號(hào),鎖相倍頻芯片將25MHz頻率通過鎖相倍頻的方式合成到50MHz,從而實(shí)現(xiàn)晶振最終的50MHz頻率輸出。如果晶振內(nèi)部鎖相倍頻芯片異常或不工作,就會(huì)導(dǎo)致晶振最終無輸出。

3.2 鎖相芯片故障導(dǎo)致晶振無輸出原理

該型號(hào)溫補(bǔ)晶振內(nèi)部電路使用25MHz溫補(bǔ)晶振集成電路,通過鎖相倍頻芯片實(shí)現(xiàn)50MHz頻率輸出。晶振內(nèi)部的倍頻芯片的原理框圖如圖1所示,芯片內(nèi)部實(shí)際為一個(gè)集成鎖相環(huán)電路,芯片輸出與輸入的關(guān)系式見公式(1):

式中,M、R、P為倍頻芯片中的頻率設(shè)置數(shù)。

在該型號(hào)晶振中,芯片設(shè)置為50=25×2/(1×1),即M=2、R=1、P=1,晶振最終輸出為“CLK0”端輸出,“CLK0”端輸出頻率直接由VCO的振蕩頻率決定。芯片內(nèi)部VCO的輸出頻率范圍覆蓋較寬(1MHz~200MHz),針對不同輸出頻率,內(nèi)部電路需要對VCO振蕩頻率進(jìn)行分段切換,切換到覆蓋輸出頻率的頻段范圍內(nèi),最終實(shí)現(xiàn)需要的頻率輸出。

根據(jù)晶振的故障現(xiàn)象和鎖相倍頻芯片的運(yùn)行原理可推斷:故障晶振使用的鎖相倍頻芯片內(nèi)部VCO參數(shù)不良,在上電延時(shí)可能引起VCO內(nèi)部電路時(shí)序錯(cuò)誤,無法對VCO的振蕩頻率進(jìn)行選段切換,造成VCO不工作,最終造成芯片無輸出即晶振無輸出的故障現(xiàn)象。

由以上分析可知,根據(jù)晶振的故障現(xiàn)象和鎖相倍頻芯片的運(yùn)行原理可推斷,如果鎖相倍頻芯片內(nèi)部VCO參數(shù)不一致(參數(shù)臨界或偏移),在上電延時(shí)的情況下,芯片內(nèi)部的VCO偶爾會(huì)出現(xiàn)無法正常工作的情況,最終晶振無50MHz的頻率輸出。

3.3 鎖相芯片參數(shù)異常的原因

該芯片為進(jìn)口器件,由于芯片生產(chǎn)過程每個(gè)芯片產(chǎn)品存在一定的個(gè)體差異,存在個(gè)別芯片參數(shù)較臨界的情況。而故障晶振在經(jīng)過產(chǎn)品生產(chǎn)過程中的篩選試驗(yàn)以及使用過程中的篩選試驗(yàn)后,倍頻芯片內(nèi)部參數(shù)進(jìn)一步的漂移。在有上電延時(shí)以及多次上電時(shí),參數(shù)臨界的芯片內(nèi)部電路可能偶爾出現(xiàn)時(shí)序錯(cuò)誤,導(dǎo)致內(nèi)部VCO電路工作不良或不工作,造成晶振無輸出的故障現(xiàn)象。

4 改進(jìn)措施

為避免問題的再次發(fā)生,在元器件二次篩選過程中,設(shè)計(jì)篩選用的測試板對晶振進(jìn)行加電測試,擬將電源延時(shí)設(shè)置在24ms左右,晶振的上電檢測次數(shù)擬定為20次。

5 結(jié)論

50MHz溫補(bǔ)晶振出現(xiàn)的加電偶有無輸出的故障,是由于晶振內(nèi)部鎖相倍頻集成芯片性能不良導(dǎo)致,屬于偶然的個(gè)別現(xiàn)象。使用24ms延時(shí)的電源對晶振進(jìn)行20次加電測試,發(fā)現(xiàn)失效問題,可在早期解決這一問題。

[1]成都天奧電子股份有限公司.頻率器件產(chǎn)品手冊[Z].成都:成都天奧電子股份有限公司,2012.

作者單位 中國電子科技集團(tuán)公司第十研究所 四川省成都市 610036

張富堯(1986-),男,四川省隆昌縣人。大學(xué)本科學(xué)歷。助理工程師,從事于元器件檢測工作。