基于VPX的多DSP+FPGA紅外圖像處理系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

祝樹生,李晶,呂殿君,陳冉,仇公望

(1.中國運(yùn)載火箭技術(shù)研究院研究發(fā)展中心,北京,100076;2.西安北方光電股份有限公司,陜西西安,710043)

基于VPX的多DSP+FPGA紅外圖像處理系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

祝樹生1,李晶1,呂殿君1,陳冉2,仇公望1

(1.中國運(yùn)載火箭技術(shù)研究院研究發(fā)展中心,北京,100076;2.西安北方光電股份有限公司,陜西西安,710043)

針對(duì)大面陣紅外圖像快速處理要求及模塊化設(shè)計(jì)原則,本文采用了4片TI公司的DSP和1片Virtex7 FPGA設(shè)計(jì)了一個(gè)多DSP的紅外圖像實(shí)時(shí)處理系統(tǒng),試驗(yàn)表明該系統(tǒng)適用于復(fù)雜圖像處理算法的計(jì)算和實(shí)時(shí)圖像中跟蹤目標(biāo)的實(shí)時(shí)處理。

VPX;多DSP;紅外圖像處理系統(tǒng)

0 引言

隨著精確制導(dǎo)導(dǎo)彈對(duì)紅外末制導(dǎo)系統(tǒng)性能要求的不斷提高,紅外導(dǎo)引頭的成像焦平面由早期的256×256逐步升級(jí)為640×512和512×512,并且圖像的處理周期也越來越高。

針對(duì)大面陣紅外焦平面圖像的高速處理要求,采用“規(guī)范化、標(biāo)準(zhǔn)化、通用化”的設(shè)計(jì)原則,選用目前最流行的VPX總線,設(shè)計(jì)了基于VPX總線的多DSP+FPGA架構(gòu)的通用紅外圖像處理系統(tǒng),不但能滿足導(dǎo)引頭紅外圖像處理實(shí)時(shí)性、大數(shù)據(jù)量要求,還可建立基于VPX標(biāo)準(zhǔn)的通用高速圖像處理平臺(tái)。

1 系統(tǒng)設(shè)計(jì)

1.1 硬件設(shè)計(jì)

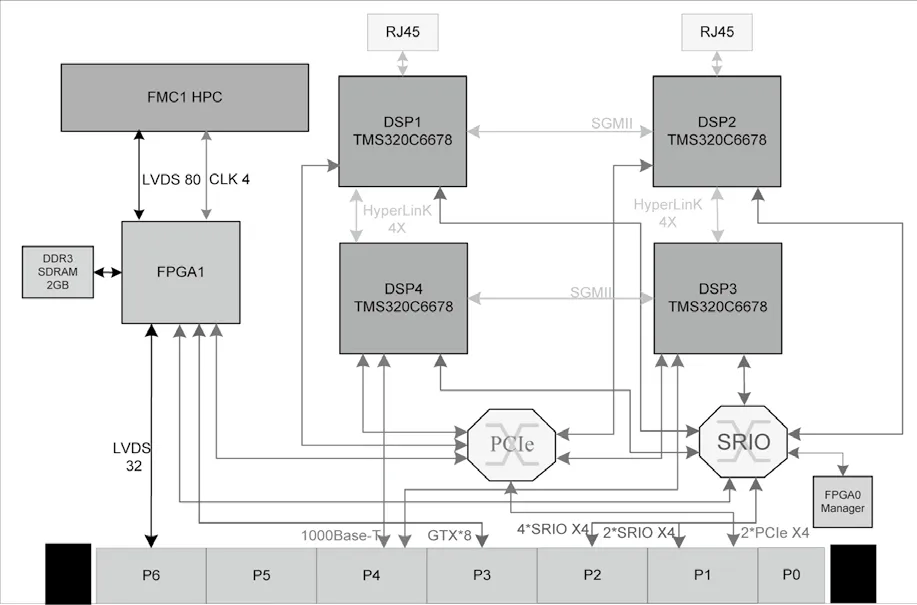

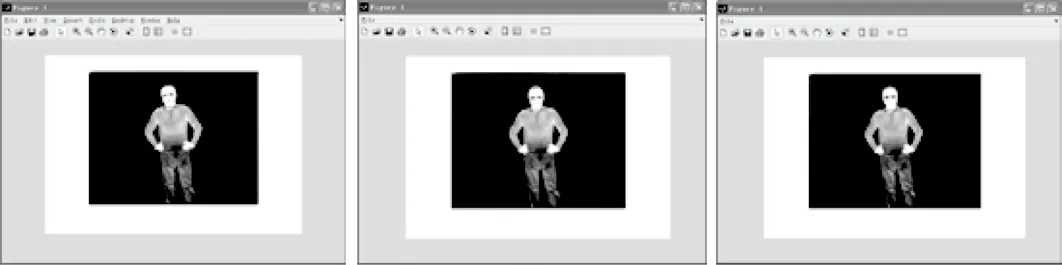

圖像處理系統(tǒng)采用基于VITA46標(biāo)準(zhǔn)的VPX模塊架構(gòu),以四片Ti公司C667x系列DSP和一片Xilinx公司7系列FPGA為核心節(jié)點(diǎn)。DSP處理器選用TI公司的TMS320C6678,該處理器有八個(gè)內(nèi)核,最高主頻1.25GHz,DSP外接DDR3 SDRAM,位寬64bit,時(shí)鐘666.7MHz,容量2GB。兩片DSP通過Hyper Link接口互聯(lián),每個(gè)DSP均設(shè)計(jì)一個(gè)千兆以太網(wǎng)接口。FPGA為Xilinx公司的XC7K325T,實(shí)現(xiàn)一個(gè)FMC接口,一個(gè)DDR3接口,一個(gè)SRIO 4×接口,一個(gè)PCIe 4×接口,兩個(gè)GTX 4×接口。板上通過IDT公司的SRIO交換片CPS-1848將四片6678和一片XC7K325T的SRIO互聯(lián),并擴(kuò)展六個(gè)SRIO 4×接口到VPX的P1連接器上。

處理系統(tǒng)的實(shí)現(xiàn)采用符合OpenVPX 6U平臺(tái)的標(biāo)準(zhǔn)板卡,滿足高帶寬高處理性能的需求。板卡原理框圖如圖 1所示。

1.2 目標(biāo)識(shí)別

目標(biāo)識(shí)別算法的輸入為紅外探測器實(shí)時(shí)成像的視頻數(shù)據(jù)和已裝訂的目標(biāo)圖像信息。圖像匹配過程中,將目標(biāo)圖像信息作為模板圖像,將實(shí)時(shí)成像的圖像作為搜索圖像。目標(biāo)識(shí)別算法的輸出是在當(dāng)前搜索圖像中,與模板圖像匹配度最高的子圖左上角所在的像素位置。

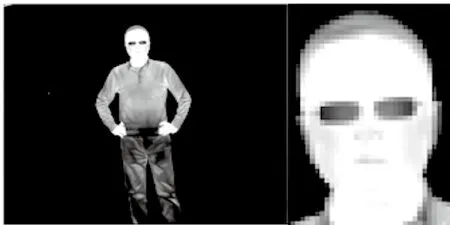

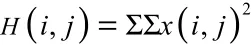

對(duì)于實(shí)時(shí)圖為640×512,采用基于歸一化互相關(guān)系數(shù)的方法實(shí)現(xiàn)目標(biāo)求解。根據(jù)對(duì)探測目標(biāo)的預(yù)測,選擇行數(shù)和列數(shù)覆蓋待識(shí)別目標(biāo)的矩形區(qū)域作為模板圖像,矩形區(qū)域的分辨率可變,如圖 2所示。

圖 2 互相關(guān)圖像匹配的搜索圖及放大后的模板圖示意

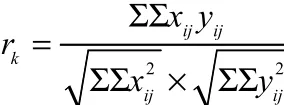

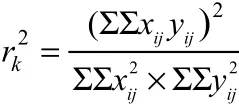

設(shè)待識(shí)別的模板圖像大小為m×n,在640×512的搜索圖像中進(jìn)行逐行逐列搜索匹配時(shí),搜索圖像依次形成(640-m+1)×(512-n+1)個(gè)子圖,每個(gè)子圖尺寸為m×n。則第k個(gè)子圖X與模板圖Y的相關(guān)系數(shù)為:

式中,xij為搜索圖的子圖X中第i行、第j列像元的灰度值;yij為模板圖Y中第i行、第j列像元的灰度值。相關(guān)系數(shù)極大值對(duì)應(yīng)子圖在搜索圖上的位置即為最佳匹配位置。

圖 1圖像處理板卡框圖

由公式可知,計(jì)算相關(guān)系數(shù)的運(yùn)算量相當(dāng)巨大,乘加運(yùn)算次數(shù)與3×(640-m+1)×(512-n+1)×m×n成正比,開方次數(shù)運(yùn)算與2×(640-m+1)×(512-n+1)成正比。由于本方案采用DSP作為運(yùn)算平臺(tái),開方運(yùn)算較復(fù)雜,需要消耗大量的時(shí)鐘周期。根據(jù)C6678的運(yùn)算能力,達(dá)不到對(duì)100Hz圖像實(shí)時(shí)處理的需求,因此還需要對(duì)算法加以優(yōu)化和改進(jìn)來減少運(yùn)算量及復(fù)雜度。

為實(shí)現(xiàn)快速圖像計(jì)算,本方案采用以下措施來優(yōu)化算法,以實(shí)現(xiàn)圖像相關(guān)匹配和目標(biāo)識(shí)別。

(1)相關(guān)系數(shù)計(jì)算公式變換

將計(jì)算得到的rk值轉(zhuǎn)化為計(jì)算的值:

(2)圖像預(yù)處理

為搜索圖子圖像素灰度平方和,每個(gè)子圖都需重新計(jì)算,可采用事先計(jì)算基準(zhǔn)圖像灰度平方和積分圖像來減少運(yùn)算量。設(shè)H為搜索圖X對(duì)應(yīng)的積分圖像,有:

H( i , j)即為搜索圖中每個(gè)像素點(diǎn)左上方全部區(qū)域內(nèi)像素灰度值平方求和結(jié)果。對(duì)于每個(gè)子圖來說,計(jì)算程可以被 計(jì) 算 H ( i , j) ? H ( i ? m , j ) ? H ( i , j ? n ) + H ( i ? m , j ? n )來 代 替,(640-m+1)×(512-n+1)×m×n次運(yùn)算被4×m×n次計(jì)算代替。

可見,經(jīng)過事先預(yù)處理優(yōu)化后,相關(guān)匹配的主要運(yùn)算算量可大大減少。

(3)搜索策略優(yōu)化

相關(guān)匹配的基本搜索策略是遍歷性搜索,即在搜索區(qū)域內(nèi)逐行逐列每個(gè)像素位置上計(jì)算相關(guān)系數(shù)值。因此,使用改進(jìn)搜索策略的方法,實(shí)現(xiàn)非遍歷性搜索,將大大減少相關(guān)匹配的運(yùn)算量。

根據(jù)TMS320C6678DSP的特點(diǎn),使用分層搜索,實(shí)現(xiàn)有效的非遍歷性搜索策略。該設(shè)計(jì)采用金字塔分解、逐級(jí)匹配的策略,通過2×2鄰域平均方法降分辨率生成下層分解圖像,如此逐層遞推,從而構(gòu)成多級(jí)金字塔圖像。

假設(shè)已分解獲得k級(jí)金字塔圖像,搜索匹配時(shí),首先在k層(分辨率最低)圖像中的所有位置上計(jì)算互相關(guān)系數(shù),得到k層圖像的匹配位置。然后將k層圖像的匹配位置映射到k-1層圖像作為k-1層圖像的粗匹配位置。再在k-1層圖像的粗匹配位置和附近幾個(gè)位置(通常以粗匹配位置為中心的一個(gè)n×n區(qū)域)計(jì)算互相關(guān)系數(shù),得到k-1層圖像的匹配位置。以此類推,一直到在0層圖像中找到匹配位置為止。顯然,只有k層圖像中的搜索匹配是在所有位置上遍歷進(jìn)行的,而其它層的搜索匹配位置都相當(dāng)少。同時(shí),由于降分辨率的關(guān)系,k層圖像的大小只有原始圖像的1/4k,相應(yīng)的運(yùn)算量則只有原始的1/16k。本方案采用3級(jí)金字塔圖像進(jìn)行初始粗匹配,每次精匹配在上一級(jí)粗匹配位置為中心的16×16區(qū)域計(jì)算相關(guān)系數(shù)。可實(shí)現(xiàn)運(yùn)算量變?yōu)槲锤淖兯阉鞑呗郧暗?/4096。

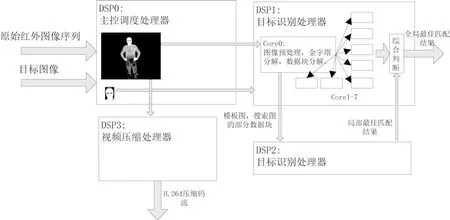

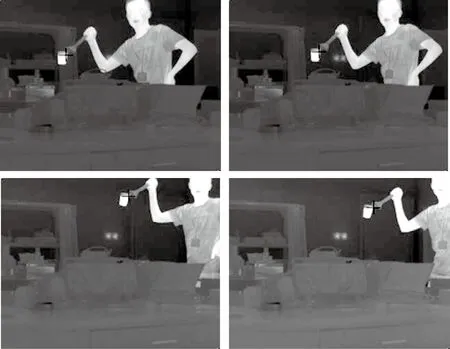

使用上述經(jīng)過優(yōu)化的算法,利用數(shù)幀實(shí)際成像結(jié)果,在上位機(jī)Matlab中進(jìn)行算法仿真,在每幀圖像中求出與模板圖像相關(guān)匹配程度最高的子圖,以此子圖的左上角坐標(biāo)為基準(zhǔn),以模板圖像大小在搜索圖(大圖)中使用矩形邊框標(biāo)記目標(biāo)匹配的位置如圖像分割和任務(wù)分配,DSP1的Core1~Core7及DSP2為從處理單元,根據(jù)主處理單元分配的任務(wù)完成相應(yīng)處理。圖像匹配算法的主要處理流程如圖 4所示。

其中,DSP1的Core0為主處理單元,控制整個(gè)相關(guān)匹配的工作流程,接收到待處理的圖像數(shù)據(jù)后,首先對(duì)圖像進(jìn)行預(yù)處理,包括圖像濾波去噪,旋轉(zhuǎn)、幾何校正等,并對(duì)圖像進(jìn)行金字塔分解。然后將搜索圖(大圖)分解為從處理單元數(shù)整數(shù)倍個(gè)數(shù)據(jù)塊,并分配給從處理單元進(jìn)行處理。從處理單元接收到任務(wù)后,完成指定的相關(guān)系數(shù)計(jì)算后,將結(jié)果送回給Core0,由Core0綜合所有的相關(guān)系數(shù)形成相關(guān)面,并求得最高峰所在位置即為匹配位置。每一級(jí)金字塔都如此操作,直至在原始圖像中獲得最終的匹配結(jié)果。圖 3所示。

可以看到,在Matlab算法仿真過程中,在多幀圖像中具有相同目標(biāo)且目標(biāo)位姿發(fā)生變化時(shí),識(shí)別率高,位置準(zhǔn)確。

2 系統(tǒng)實(shí)現(xiàn)及測試

為了實(shí)現(xiàn)實(shí)時(shí)處理實(shí)現(xiàn)歸一化互相關(guān)圖像匹配,經(jīng)上述優(yōu)化的算法還要結(jié)合多核并行處理的DSP運(yùn)算方式進(jìn)行專用設(shè)計(jì)。板卡上的4個(gè)DSP中分別用作主控調(diào)度、視頻壓縮和目標(biāo)識(shí)別計(jì)算,DSP1和DSP2用作目標(biāo)識(shí)別算法,DSP3和DSP4用作主控和視頻壓縮。在目標(biāo)識(shí)別方面,把DSP1的Core0作為主處理單元,負(fù)責(zé)

圖 3圖像匹配算法Matlab仿真結(jié)果

圖 4 基于多DSP系統(tǒng)的目標(biāo)識(shí)別流程

在任務(wù)分配給每個(gè)處理器核后,使用DSP特有的優(yōu)化方式對(duì)運(yùn)算過程作進(jìn)一步優(yōu)化。這部分的工作主要分為兩部分:一部分是充分利用DSP上集成的各種硬件加速器為匹配算法服務(wù),充分發(fā)揮DSP的硬件結(jié)構(gòu)優(yōu)勢(shì);另一部分為語言級(jí)的優(yōu)化,即通過C語言或匯編語言對(duì)耗時(shí)最多的循環(huán)進(jìn)行優(yōu)化,進(jìn)一步提高算法的實(shí)時(shí)效率。同時(shí),由于C6678的C語言編譯器具有70%~80%的匯編語言級(jí)處理能力,所以通常采用基于C語言的優(yōu)化方法就可以達(dá)到性能要求。

鑒于使用的相關(guān)匹配算法的特點(diǎn)是計(jì)算量和數(shù)據(jù)量都很大,對(duì)于DSP系統(tǒng),片內(nèi)RAM速度通常可以達(dá)到2.56 Gbit帶寬,并且可以隨機(jī)操作而不降低效率,但是容量只有64 k字節(jié)。而片外RAM容量很大,但是速度通常只有100~300 Mbit帶寬,隨機(jī)操作時(shí)效率將嚴(yán)重下降。這時(shí),由于數(shù)據(jù)交換瓶頸,算法效率嚴(yán)重下降,浪費(fèi)了DSP的計(jì)算能力。因此,必須優(yōu)化算法的數(shù)據(jù)流結(jié)構(gòu),使得算法需求與硬件結(jié)構(gòu)相吻合。采取先將基準(zhǔn)圖和實(shí)時(shí)圖存儲(chǔ)于外部存儲(chǔ),待計(jì)算時(shí)再將它們分塊搬入到片內(nèi)RAM,這樣既可以合理地分配存儲(chǔ)區(qū)域,又能提高數(shù)據(jù)處理的效率。對(duì)于程序代碼也是相同的,將核心代碼及與實(shí)時(shí)性要求緊密相關(guān)的放在片內(nèi),以便獲得較高的代碼執(zhí)行效率;而一般代碼及實(shí)時(shí)性要求不高的放在片外,節(jié)省片內(nèi)存儲(chǔ)空間。

同時(shí)使用C6678的EDMA控制器來進(jìn)行內(nèi)存管理與控制,通過設(shè)置其控制寄存器和參數(shù)RAM,可以方便高效地實(shí)現(xiàn)圖像的填充、轉(zhuǎn)置、子圖截取、行列變換互相轉(zhuǎn)化等操作。

綜上可知,經(jīng)過算法的優(yōu)化及其針對(duì)多DSP平臺(tái)的移植與優(yōu)化,可實(shí)現(xiàn)對(duì)100Hz紅外圖像的實(shí)時(shí)目標(biāo)識(shí)別。利用歸一化互相關(guān)圖像匹配算法,在完成圖像匹配,計(jì)算出實(shí)時(shí)成像的紅外圖像中與待識(shí)別目標(biāo)所在的模板圖相關(guān)度最高的子圖后,將此子圖的左上角坐標(biāo)作為識(shí)別結(jié)果,輸出至通用處理器模塊和遙測采集模塊。實(shí)時(shí)解算結(jié)果如圖 5所示。

圖 5目標(biāo)跟蹤實(shí)時(shí)解算圖

3 結(jié)束語

采用4片6678DSP芯片和1片Virtex7 FPGA實(shí)現(xiàn)的紅外圖像處理系統(tǒng),通過圖像預(yù)處理和搜索策略的優(yōu)化減少了實(shí)時(shí)處理的運(yùn)算量,提高了目標(biāo)識(shí)別、跟蹤速度,能夠滿足未來大視場紅外導(dǎo)引頭圖像實(shí)時(shí)計(jì)算要求,且該系統(tǒng)采用了基于VITA46.0標(biāo)準(zhǔn)的VPX接口,滿足了信號(hào)處理模塊通用性、小型化、低成本的要求。

[1]楊剛,向聰,袁子喬,趙博.基于TMS320C6678的ISAR實(shí)時(shí)成像方法研究[J].火控雷達(dá)技術(shù),2015,44(2):449-454.

[2]葉偉,符廣平,周安.基于多DSP+FPGA圖像實(shí)時(shí)解碼系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[J].計(jì)算機(jī)與數(shù)字工程,2015,43(11):37-46.

[3]王風(fēng)賀,楊乾,王剛.紅外圖像預(yù)處理設(shè)計(jì)及非均勻性算法應(yīng)用[J].光電技術(shù)應(yīng)用,2013,28(5):46-53.

[4]王勇,張平.高性能多DSP互聯(lián)技術(shù)[J].電子產(chǎn)品世界,2009(4):33-36.

[5]孫莉,吳順君,蘇濤.DSP并行系統(tǒng)設(shè)計(jì)方法研究[J].計(jì)算機(jī)應(yīng)用研究 .2002(9):68-70.

Design and implementation of an infrared image processing system with multiple DSP+FPGA based on VPX

Zhu Shusheng1,Li Jing1,Chen Ran2,Lv Dianjun1,Qiu Gongwang1

(1.R&D Center,China Academy of Launch Vehicle Technology,Beijing,10076;2. Sicong Optoelectronic Company Limited,Xi’an Shaanxi,710043)

For the infrared image fast real-time processing system with large format and modular design principles,the paper desgins an infrared image real time system which has four pieces of TI’DSP and one Virtex7 FPGA.The experiment shows that this system is the same with complex image algorithm and real-time processing of target tracking.

VPX;multi-DSPs; a infrared image processing system

祝樹生(1984-),男,山西朔州人,工程師,主要從事電氣系統(tǒng)總體設(shè)計(jì)工作。