基于FPGA的增量式PID算法的設計與改進

張 偉,張 建,高 巖,孫天澳,李旭升,王云亮

(丹東東方測控技術股份有限公司,遼寧丹東,118000)

基于FPGA的增量式PID算法的設計與改進

張 偉,張 建,高 巖,孫天澳,李旭升,王云亮

(丹東東方測控技術股份有限公司,遼寧丹東,118000)

本文介紹了一種基于FPGA的用Veilog HDL語言設計的增量式PID控制器的設計方法,并為了提高控制精度,消除精差,減少由于短時間內系統輸出余量過大造成的偏差而引起系統較大的振蕩,因此增加了積分分離控制算法,從而進一步提高了PID控制算法的穩定性和控制精度。

FPGA;增量式;PID;積分分離

0 引言

數字PID控制算法是在過程控制中普遍采用的控制方法,具有靈活可控的特點。但是由于在實際工業生產過程中往往存在非線性,時變不確定,波動大,穩定時間不確定等因素,使用常規的PID控制器不能達到理想的控制效果。本文采用FPGA軟件設計,實現改進型增量式PID算法,成功應用于工業在線檢測儀表探測器的穩峰電路中,降低了控制過程中的調整波動,提高了電壓調整的穩定性和可控性。

1 增量式PID算法原理

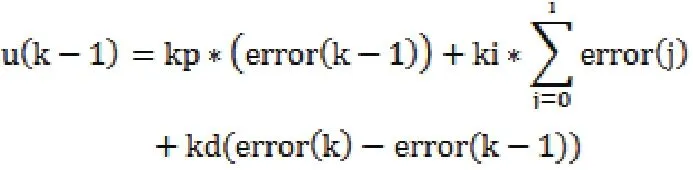

PID控制器是一種線性控制器,其控制規律如下所示:

增量式PID控制算法如下:

式中:kp--比例系數;ki--積分系數;kd—微分系數;Δu(k)—第K次采樣時刻的輸出控制量增量;error(k)—第K次采樣時刻的輸入偏差量。

由上式可知,增量式PID控制算法增量僅與最近K次的采樣有關,所以誤動作影響小,而且較容易通過加權處理獲得比較好的控制效果。

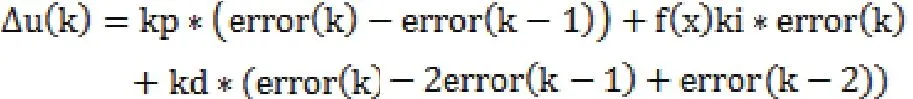

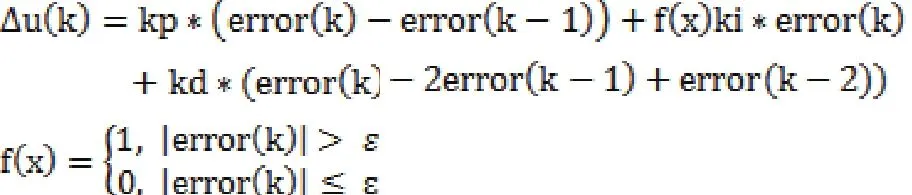

1.1 積分分離控制原理

積分分離的控制原理是:當輸入偏差(即輸入量與設定值)較大時,取消積分系數,避免超調量過大引起系統的穩定性降低;因此,設置積分分離線,當輸入偏差接近積分分離時,引入積分控制調整,以便消除靜差,提高控制精度。如下對增量式PID公式引入積分分離線:

(1)根據探測器穩峰閾值輸入積分分離線:ε>0;

(2)當|error(k)|>ε時,采用PID控制,以保證系統的控制精度;

(3)當|error(k)|≤ε時,采用PD控制,可避免產生過大的超調,使系統有較快的響應;引入積分分離后,增量式PID算法可表示為:

2 FPGA設計實現方法

(1)由于增量式PID運算過程中,描述輸入偏差量的表達式e(k)為絕對值,因此引入增減模式控制信號mode[1:0],其變量用于表達e(k)的差值符號,用于控制PID過程變量傳遞參數時是遞增預算還是遞減運算。

(2)區別與基于C語言設計的ARM,單片機等過程設計,使用Verilog HDL語言的FPGA設計屬于硬件描述語言,所有進程模塊為并行結構,而且在PID運算實現的設計中存在過程變量傳遞參數,因此不能使用非阻塞式賦值,應當在進程模塊中實現異步賦值。

(3)增加過程變量輸出變量u(k),u(k-1),u(k-2),用于對比增量變化,實現積分分離控制。

圖1 增量式PID算法軟件流程圖

3 軟件算法設計驗證[1]

(1)通過Modelsim軟件對FPGA實現的增量式PID軟件改進算法進行仿真,設置激勵參數。

(2)設置PID參數,其中比例系數Kp = 10;積分系數Ki = 5;微分系數Kd = 30;積分分離線偏差值initegral_value = 10。

(3)設置輸入變差datain,并逐次遞減。

(4)分別設置增減模式控制mode。

(5)e0,e1,e2為過程參數,用于計算積分分離線;u0,u1,u2為輸出過程參數;du為增量。

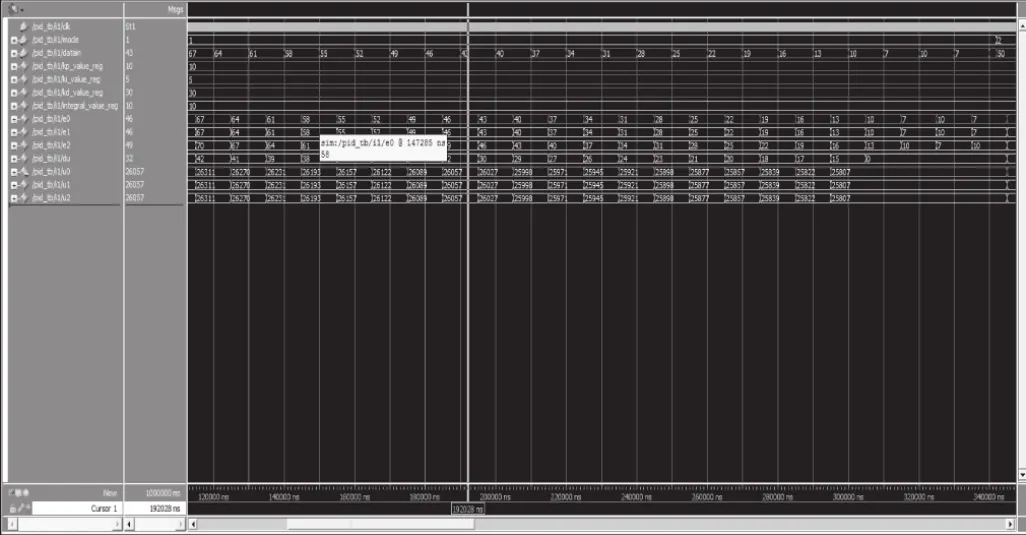

如圖2所示為增量式PID算法mode = 1遞減模式時Modelsim仿真圖[2]。

圖2 增量式PID軟件算法遞增方式仿真圖

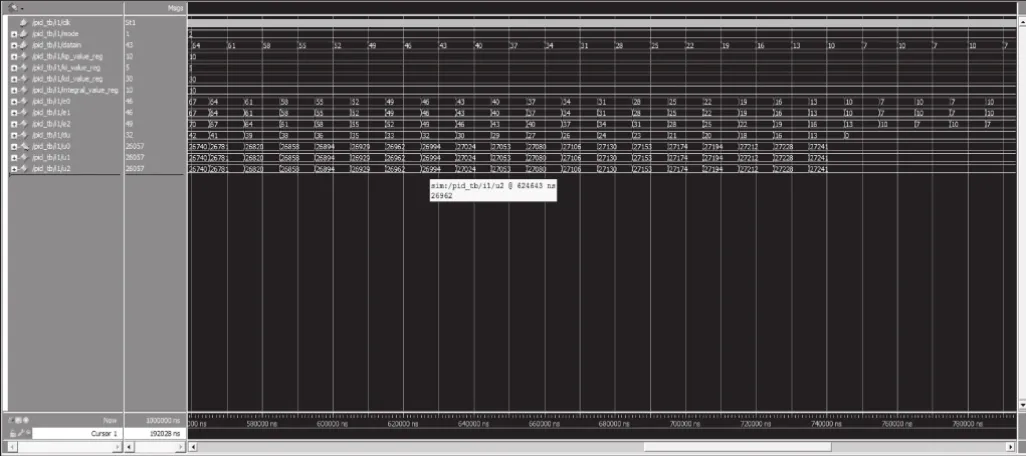

如圖3所示為增量式PID算法mode = 2遞增模式時Modelsim仿真圖。

圖3 增量式PID軟件算法遞減方式仿真圖

通過圖2,圖3中所示,增量式PID算法,其增減變化只于增量有關,減少了由于過程量變化引起的波動,避免了由靜差變化引起的過程參數的不穩定性變化,而且加入了積分分離線,減少了系統趨于穩定區間過程中不必要的余量,造成控制的不穩定性。

4 增量式PID改進控制算法在產品中的應用

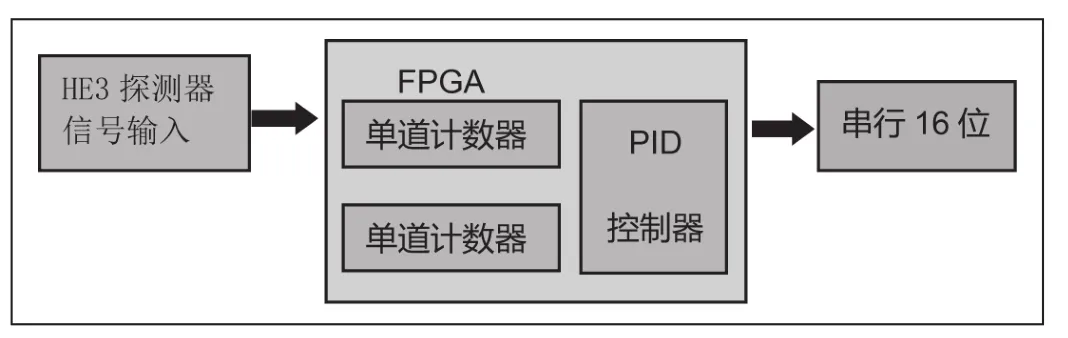

本文作者根據上述設計原理以及軟件結構的基礎上,采用Altera公司FPGA,Cyclone E系列芯片EP4CE22上得以驗證和實現。本設計應用于氦3探測器穩峰電路中,通過兩路通道計數的采集,確定輸入量偏差,針對輸入量偏差進行PID運算得到16位輸出量u0,再將16位輸入量u0直接通過spi接口接入單通道16位精度DAC中,輸出0到5V的控制電壓,再通過控制電壓控制氦3探測器高壓電路,從而調整探測器兩路計數,使得兩路計數的輸入量偏差趨于零。

圖4 增量式PID改進控制算法在產品中的應用

5 結束語

在工業過程控制應用中,PID控制由于其簡單,高效,適用性強等優點,在工業領域中得到了廣泛的應用,而在硬件系統中嵌入PID運算,尤其是FPGA硬件嵌入式設計由于Verilog HDL硬件描述語言穩定性更高,更滿足數字控制電路對數據處理的吞吐量和高速I/O的要求,并減少了由于線路,工業環境,電磁干擾等因素引起的不穩定性而導致故障,造成損失,保證的檢測儀表的穩定性要求,

[1]SanirPalnitkar.Verilog數字設計與綜合.第二版[M],夏宇聞譯,電子工業出版社,2009.

[2]劉金琨.先進PID控制以及器MATLAB仿真[M],電子工業出版社,2003.

A design and improvement of the incremental PID algorithm based on FPGA

Zhang Wei,Zhang Jian,Gao Yan,Sun TianAo,Li XuShen,Wang YunLiang

(LiaoNingDanDong.DongFangCeKong,Dandong Liaoning,118000)

This paper introduces a FPGA based design method of using Veilog HDL language to design the incremental PID controller. In order to improve the control precision, eliminate the steady-state error,and reduce the large system oscillation caused by deviation due to the large allowance of system output within a short time, this design uses the integral separation control algorithm, which can improve the stability and control precision of the PID control algorithm.

FPGA;Incremental;PID;Integral separation

遼寧省“百千萬人才工程”資助項目(遼百千萬立項【2015】9號)。

張偉(1980 - ),男,本科,學士,丹東東方測控技術股份有限公司副總工程師,教授研究員級高級工程師,主要從事同位素在線檢測儀表的研發工作。