基于CAN總線的高可靠成像控制系統設計

, ,

(1.商洛學院,商洛 726000; 2.中國科學院西安光學精密機械研究所,西安 710119;3.西安交通大學,西安 710049)

基于CAN總線的高可靠成像控制系統設計

李華1,3,朱波2,鄭培云2

(1.商洛學院,商洛726000; 2.中國科學院西安光學精密機械研究所,西安710119;3.西安交通大學,西安710049)

為了實現多套成像設備的智能化控制,設計了基于CAN總線的成像控制系統,并給出了設計中關鍵技術的解決方法;首先,給出了可靠性高的熱備份CAN總線控制系統硬件設計原理;其次,介紹了基于FPGA的CAN總線協議芯片—SJA1000邏輯控制原理與方法;最后結合實際工程項目闡述了控制系統的工作過程;試驗結果表明,該設計性能穩定、可靠性高,能夠滿足多臺成像系統的智能化控制;設計理念和方法具有通用性,系統的可擴展性強。

成像系統;CAN;FPGA;熱備份;時序

0 前言

成像系統在各行各業發揮著越來越重要的作用,傳統的成像系統都是一個控制單元控制一套成像系統,控制往往采用RS422總線等點對點的形式,在成像系統只有一套時,這樣的設計性能穩定、可靠性高,在一些對可靠性要求較高的場合,如航天、航空等,仍具有較普遍的應用[1-2]。但是,隨著成像系統的發展,單臺成像系統已經遠遠不能滿足應用需要,必須增加成像系統的單機數量,不同單機完成不同的功能,但是,隨著單機數目的增加,控制單元的負擔也越來越重,采用傳統的點對點通訊形式無論是效率,還是可靠性方面都不能滿足要求。

本文在充分調研國內外相關控制技術的基礎上,研制了基于CAN總線的分布式成像控制系統。該系統采用了主從結合的體系結構,硬件設計采用了雙CAN協議芯片熱備份設計,極高的提高了整個成像系統的可靠性。通過CAN總線進行組網通信,可快速靈活的搭建好控制平臺,根據不同的需求,控制不同的單機進行工作[3-4],改變相應的成像參數,同時獲取單機的工作狀態,從而達到完美成像的目的。

1 系統總體設計

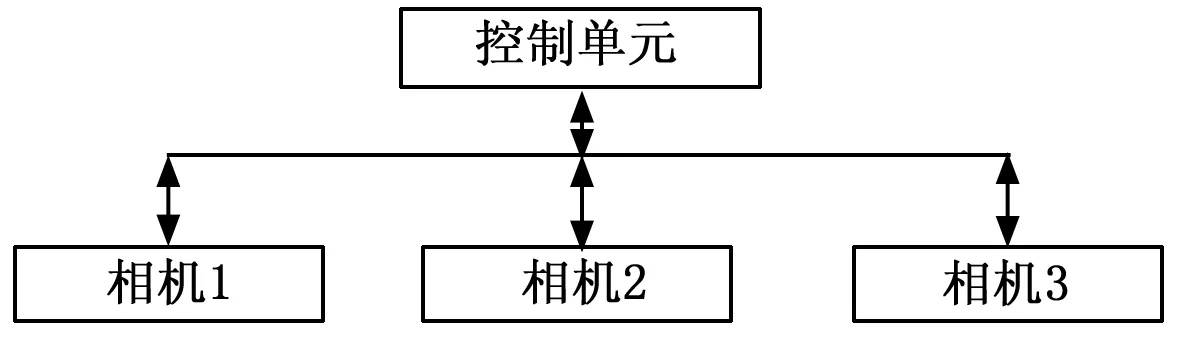

本系統總體如圖1所示。系統總共由三臺相機和一套控制單元組成,三臺相機根據需要在不同時段,使用不同參數進行相應圖像的輸出,控制單元協調三臺相機完成工程任務。

控制單元控制三臺相機的指令參數包括:曝光時間(1~47 ms可調)、幀頻(20 f/s、10 f/s、5 f/s三擋可調)、增益(3檔可調)、自動/手動曝光切換、校時(配合秒脈沖對相機進行時間修正)、初始化(相機AD配置參數)等;而相機則需要在收到遙測請求指令3 ms內,將相機當前工作狀態以遙測參數的形式返回給控制單元。可以看出,整個控制系統指令龐雜,實時性要求高,給設計帶來一定挑戰。

圖1 系統框圖

針對以上任務需求,本設計采用CAN總線作為指令、遙測傳輸通道,其中,CAN總線協議芯片使用業內比較成熟的SJA1000,接口芯片選用PCA82C250,工作方式為增強型CAN(PeliCAN)模式,使用標準幀格式傳輸,每個CAN幀長度11字節,數據前3字節為頭部信息,傳輸速率為500 Kbps。SJA1000的配置、數據發送與接收等操作由FPGA進行控制,滿足了系統工作需要。

2 系統硬件設計

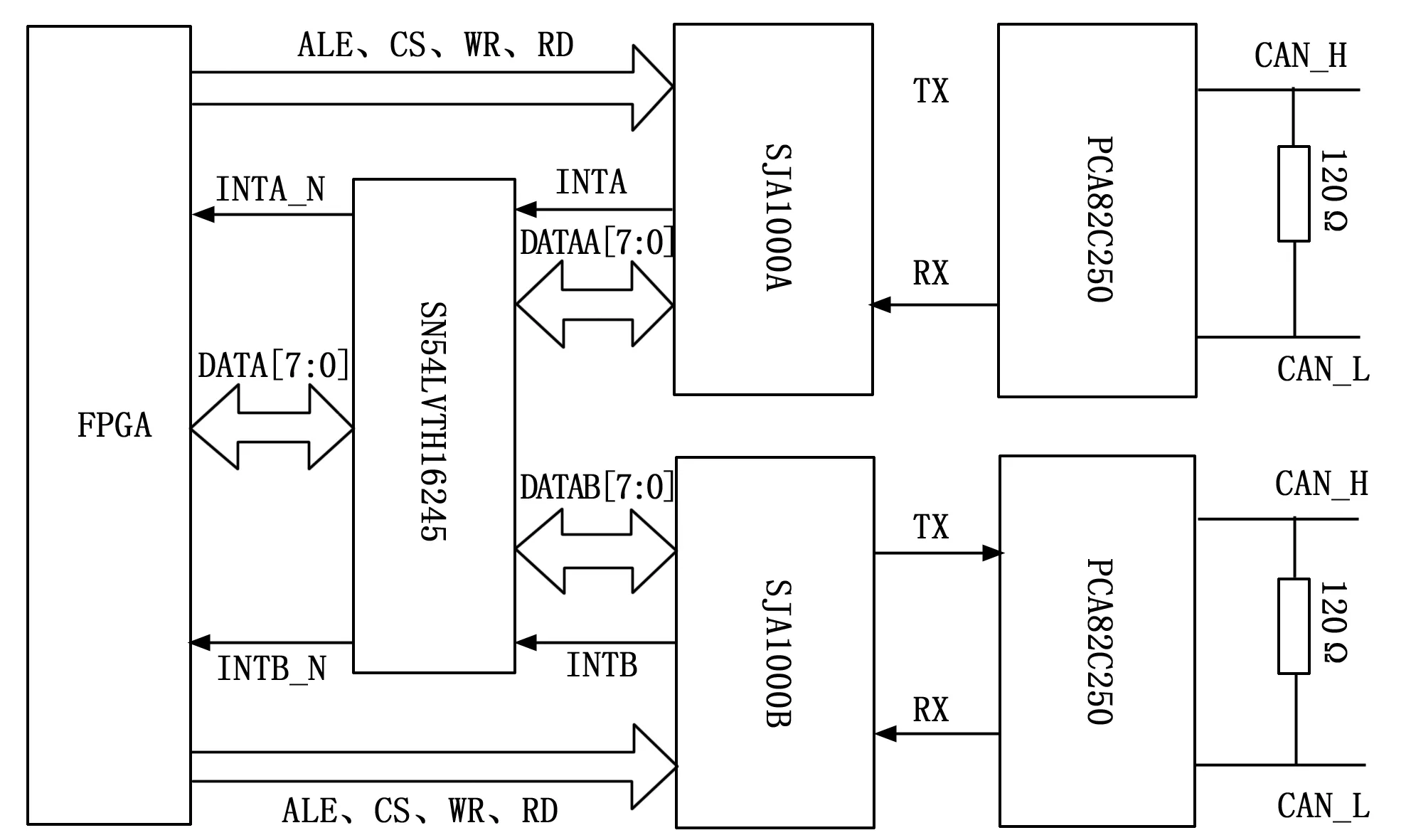

相機通訊系統的硬件組成如圖2所示。其中,FPGA模塊選用Xilinx公司Virtex II系列的XC2V3000,其核電壓為+1.5 V,輔助電壓為+3.3 V,接口電壓本設計取+3.3 V。CAN總線通訊模塊采用Philips公司生產的SJA1000作為CAN控制器芯片,PCA82C250作為CAN總線收發器。對于 Virtex II系列的FPGA而言,接口電平不支持5 V I/O標準,如果與5 V I/O標準的SJA1000直接相連,將可能導致FPGA管腳通過極大電流,造成器件的永久損壞。為了兼容電平差異,設計上采用了一片TI公司的雙向總線收發器SN54L VTH16245,將SJA1000的5 V TTL電平數據信號AD0~AD7、中斷信號INT轉換成3.3 V I/O標準信號,連接到FPGA的相應引腳上,而SJA1000讀寫控制信號CS、WR、RD、ALE對于FPGA來說是輸出信號,因此,直連至SJA1000相應的管腳即可。

為了增加系統的可靠性,適應復雜的工作環境,本設計使用了兩片SJA1000芯片,構成熱備結構。為了節約總線資源,SJA1000采用數據總線共用的形式,即兩片SJA1000的數據總線在經過SN54L VTH16245芯片前進行了2合1操作,合并后的信號經過SN54L VTH16245后進入FPGA進行處理。而兩片SJA1000的控制信號則分別進入FPGA進行控制,保證了兩片SJA1000操作的獨立性,不會造成數據丟失。

該硬件設計的兩片SJA1000互為備份,正常工作時通過SJA1000A進行通訊,如果A路出現故障,立即切換至SJA1000B進行通訊,同時對SJA1000A進行復位初始化操作,極大的提高了系統的可靠性和環境適應能力。

圖2 SJA1000熱備份硬件設計

3 系統邏輯設計

邏輯設計是本系統的核心,整個控制過程由一片FPGA完成,主要功能包括:系統主邏輯控制、初始化SJA1000、寫SJA1000和讀SJA1000。在介紹SJA1000具體操作之前,先對CAN總線的數據格式和本設計應用層數據協議簡要介紹。

CAN協議規定了兩種不同的幀格式,不同之處為標識符的長度,具有11位標識符的幀稱之為標準幀,具有29位標識符的幀被稱為擴展幀。本設計根據項目需求,使用標準幀進行數據傳輸,一幀CAN數據幀共11字節,其中前3字節為幀頭,用于數據鏈路層的控制,后面8字節為用戶數據。幀頭1~幀頭3與SJA1000的地址16、17、18對應,用戶數據與SJA1000的地址19~26對應。

應用層數據在CAN總線上傳輸之前,若總數據量少于等于8字節,則按照CAN總線單幀數據域結構組織數據,組成CAN單幀傳輸幀傳送。若總數據量大于8字節,則按照CAN總線復合幀數據域結構組織數據,組成CAN復合幀傳輸幀傳送。復合幀首幀最先發送,之后按照順序發送中間幀,最后發送尾幀。

基于SJA1000的控制系統其工作實際就是按照協議接收指令并按照要求組幀發送數據的過程,也就是在一個主控邏輯的指揮下完成SJA1000的初始化、讀、寫等操作[5]。

3.1 主控邏輯

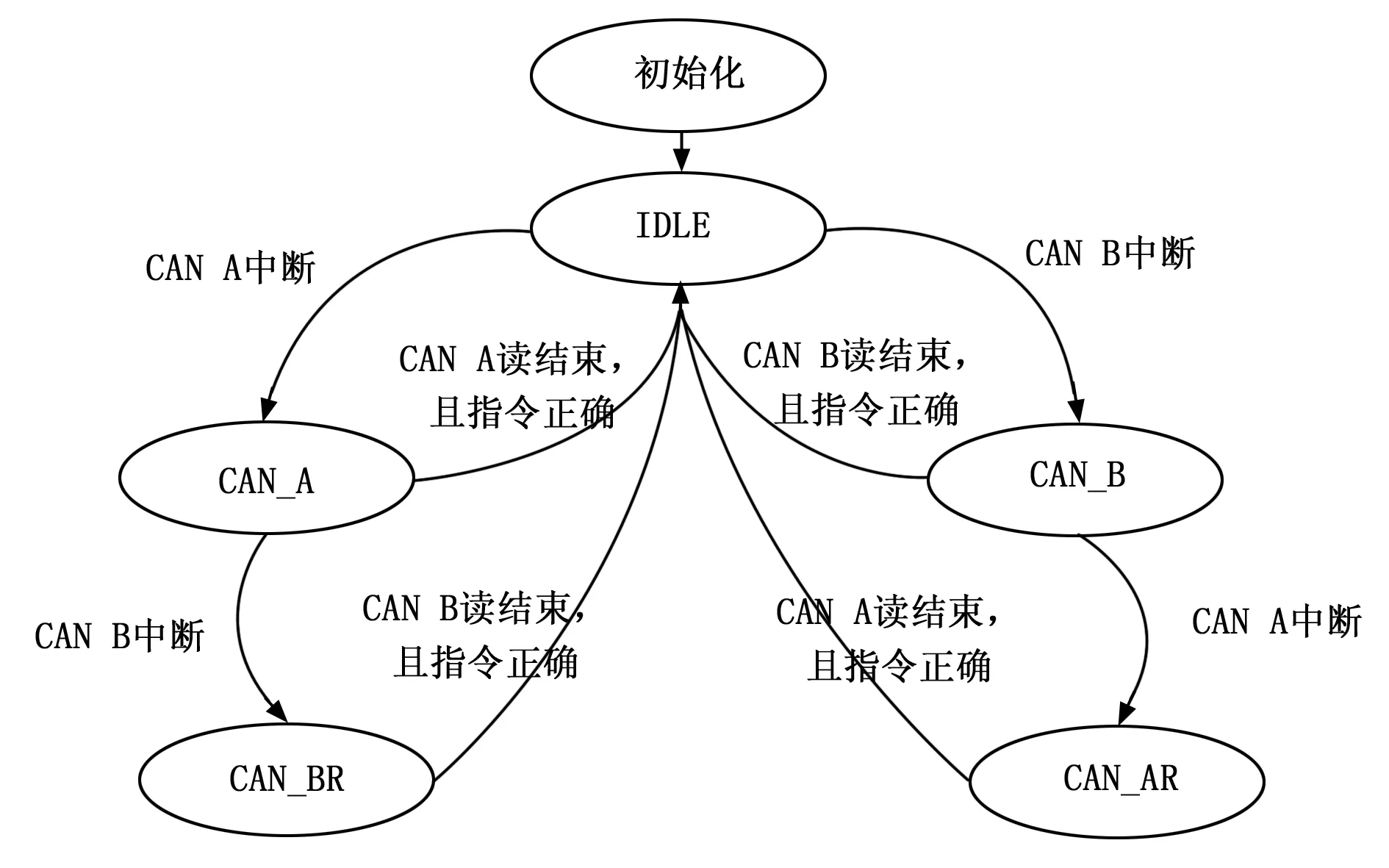

本系統的主控邏輯如圖3所示。

圖3 本系統主控時序

分析圖3可以看出,系統的主控邏輯由一個大的狀態機組成,其工作過程如下:系統上電穩定后,FPGA首先對兩片SJA1000芯片進行初始化,然后啟動狀態機進入IDLE狀態等待SJA1000芯片中斷的到來,此時,如果是SJA1000A產生的中斷,FPGA就開始對SJA1000A進行讀操作,根據讀取到的指令進行下一步工作,期間如果SJA1000B有中斷到來,先將其寄存,等待FPGA將SJA1000A的數據處理完畢,接著再讀取SJA1000B內的數據,并進行相應的后續處理工作。以上操作完成后,狀態機重新進入IDLE,等待下一次中斷的到來。同理,如果是SJA1000B的中斷先來,就先處理B內的數據。如此往復就可以控制兩片SJA1000連續工作,完成控制系統指令和遙測參數的處理。

3.2 初始化SJA1000

對SJA1000進行初始化是一切操作的開始,也是最重要的一步,系統通過配置相關的寄存器,完成SJA1000芯片的初始化。值得注意的是,SJA1000的寄存器配置只能在芯片復位模式下進行,所以應該對SJA1000實行有效的復位操作。初始化過程就是依次對總線定時寄存器0、總線定時寄存器1、輸出控制寄存器、時鐘分頻器、驗收代碼寄存器、驗收屏蔽寄存器、中斷使能寄存器等7類寄存器進行尋址和賦值。

在SJA1000需要初始化的寄存器中,最重要的是驗收代碼寄存器(ACR)和驗收屏蔽寄存器(AMR)。ACR和AMR是CAN總線實現點對點、一點對多點的重要寄存器。其中,AMR是專門為實現一點對多點而設置的寄存器,因為CAN控制器實際對網絡數據的標識符和本身的ACR值進行比較時還要參考ARM值,當AMR中某位為1時也就意味著ACR中的該位被屏蔽,任意值都可以接收,也即只比較AMR寄存器中位置為0的位,只要他們符合就接收。

以設置雙濾波,接收標識符ID.28~ID.18為0000_1010,010和ID.28~ID.18為0110_1011,111的兩類CAN標準幀為例,在PeliCAN模式下,設置驗收代碼寄存器ACR0=0x0A、ACR1=0x40、ACR2=0x6B、ACR3=0xE0;根據雙濾波器時信息幀與濾波器的位對應關系,將需要參與濾波的信息位對應的驗收屏蔽寄存器位設置為0,設置AMR0=0x00,AMR1=0x0F、AMR2=0x00、AMR3=0X0F。其他ID的標準幀則會被過濾,不會產生INT中斷。此時,如果還需要接收標識符ID.28~ID.18為0000_1011,010的標準幀,則需要將AMR0設置為0x01,告訴SJA1000對ID.21位進行屏蔽,任意值都可以通過。

本系統SJA1000時鐘為16 MHz,CAN總線的通訊波特率為500 Kbps,需要處理的幀類型有三類,因此,7類13個寄存器的值分別設置為:0x00、0x1C、0x1A、0xC7、0x20、0x00、0x02、0x00、0x01、0x0F、0x00、0x0F、0x01。寄存器設置完后,SJA1000初始化完成,就可以進行CAN總線的讀寫操作[6-7]。

3.3 讀SJA1000操作

FPGA對SJA1000的讀操作是通過INT管腳的狀態觸發的,在初始化SJA1000時,設置接收中斷使能,即如果SJA1000的緩存中有數據時,會觸發SJA1000的INT管腳電平由高變低。此時,FPGA就執行圖4所示的讀操作,將SJA1000內的數據讀取到FPGA的相關寄存器內。當FPGA將SJA1000中的數據讀取,并釋放緩沖器后,INT管腳電平又由低變高,等待下一次數據的到來。

圖4 讀SJA1000流程圖

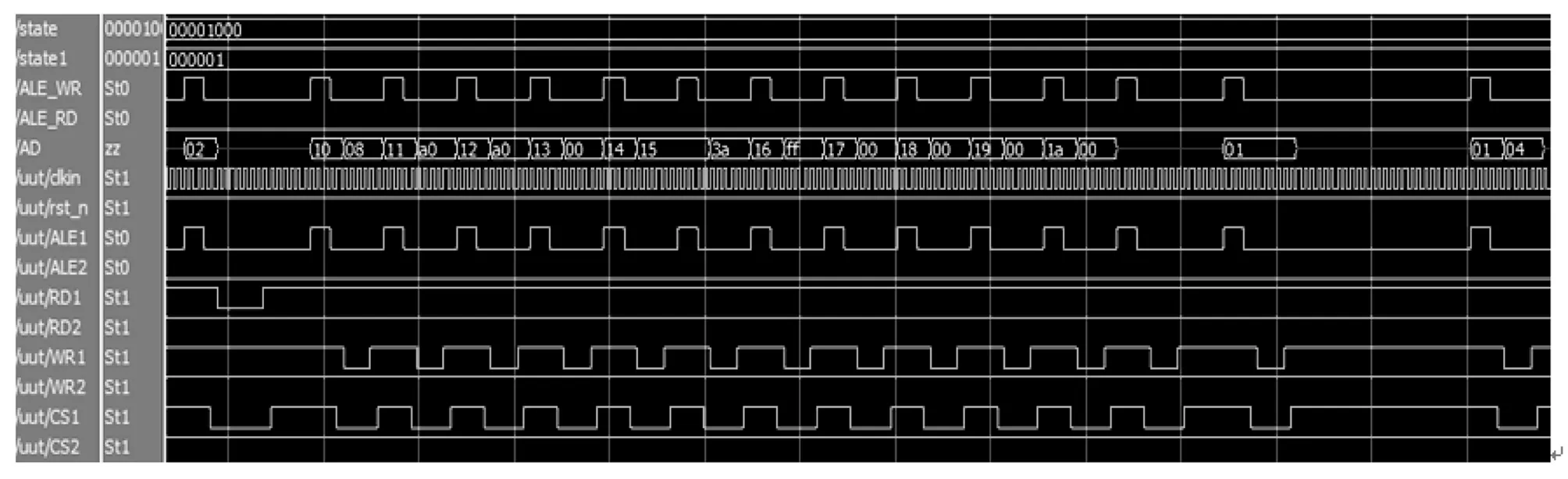

SJA1000的讀流程時序波形如圖5所示。可以看出,讀過程由4個步驟組成,在ALE、CS和RD時序有效的情況下,先判斷SR寄存器的值,然后將SJA1000接收緩存器中的數據讀出,最后再進行中斷清除和釋放接收緩存器操作。對照SJA1000手冊可知,本設計完全滿足要求。

圖5 讀SJA1000時序仿真波形

3.4 寫SJA1000操作

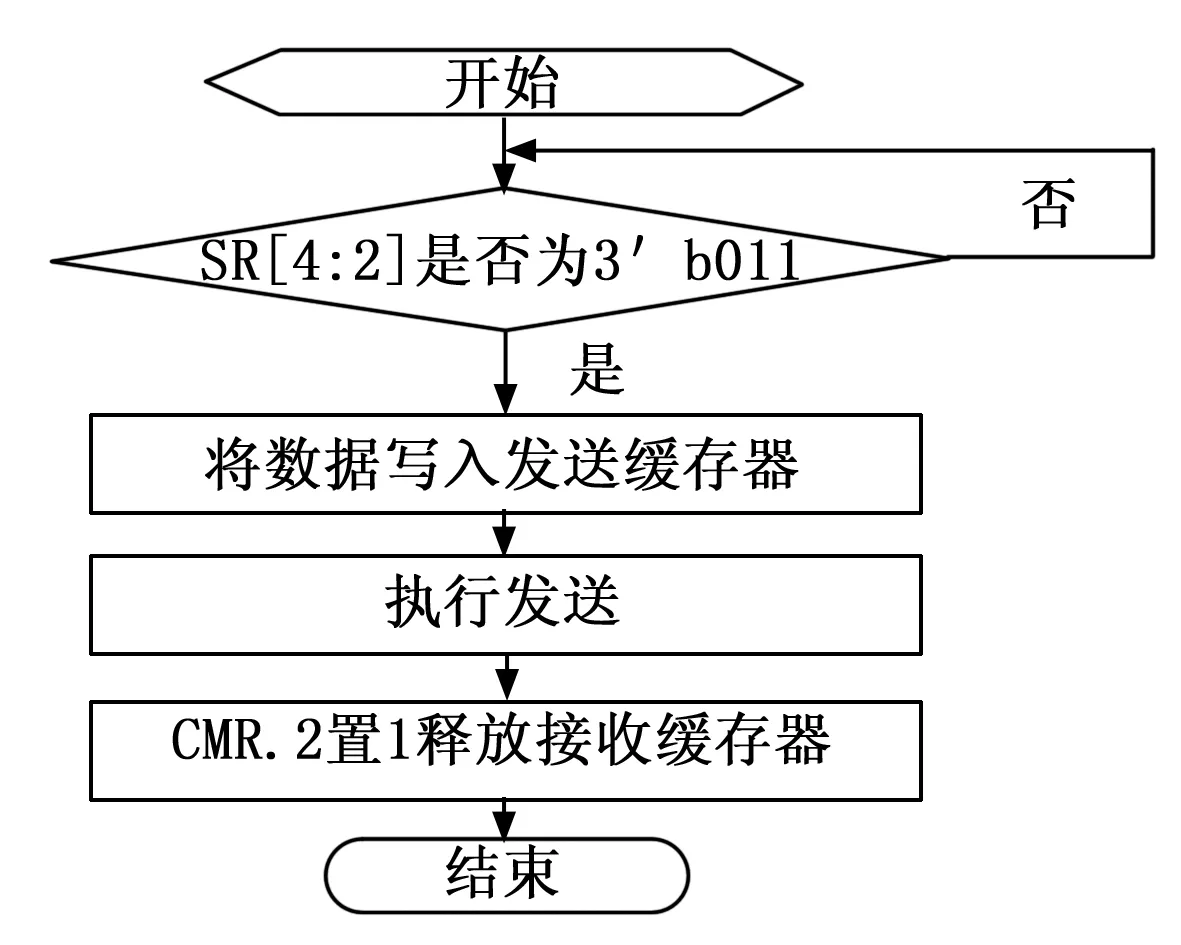

FPGA對SJA1000的寫操作是通過向SJA1000相應的寄存器寫入要發送的值完成。當相機收到控制單元發送的指令時,首先進行判斷,如果是遙測請求,則按照協議要求以復合幀的形式向控制單元發送三包遙測參數,用于反映相機當前的狀態。寫SJA1000時首先判斷SJA1000芯片當前是否在接收、發送數據,如果是則等待10 μs(根據系統指令長度和工作頻率決定),再進行判斷,如果SJA1000完成了數據的收、發,則將需要發送的數據寫入發送緩存器,如果沒有則進行恢復操作,即對SJA1000進行初始化。數據寫入操作完成后,須執行發送命令,即對CMR.0位寫入0x01,最后釋放緩存器,以等待下一次操作。具體的操作流程如圖6所示。

圖6 寫SJA1000流程圖

按照圖6所示的流程,寫SJA1000時序仿真波形如圖7所示,可以看出,整個寫過程由4個步驟組成,完成一個數據包的寫操作。在ALE、CS和WR有效的情況下先判斷SR的狀態是否滿足發送條件,如果滿足,將需要發送的數據寫入SJA1000的相關寄存器,再釋放接收緩存器。對照SJA1000手冊可知,設計完全滿足要求。

圖7 寫SJA1000時序仿真波形

4 實驗結果分析

按照以上章節思路進行系統硬件設計,兩片SJA1000構成熱備通訊系統,數據信號和中斷信號經過一片SN54LVTH16245后進入FPGA,控制信號從FPGA直連至SJA1000。物理層連接方面,SJA1000 的TX0口和RX0口分別和PCA82C250的TXD口和RXD口相連接,PCA82C250通過帶有差動發送和接收功能的兩個總線終端CAN_H和CAN_L連接到外部總線,為了匹配阻抗,提高信號傳輸的可靠性,CAN_H與CAN_L之間端接了120 Ω的電阻。

圖8 指令發送與接收界面

相機硬件設計完畢,通過地面檢測設備模擬控制單元和相機進行通訊,通訊界面如圖8所示。當發送遙測請求指令(02 20 00 00 FF)時,相機會向地檢連續返回由3條指令(即幀頭為08 A0 E0、08 A0 C0、08 A0 A0的三條指令)構成的遙測數據包,其內容按照約定協議填充,包括:曝光參數、指令計數、電壓遙測等;當發送控制指令時,相機會判斷指令的對錯,如果指令對(如30 ms曝光:05 20 00 0A 97 1E 01 C0)則返回指令接收正確(03 A1 00 3D 97 AA),如果指令錯(如錯誤曝光指令:05 20 00 0A 97 12 01 B4),則返回指令接收錯誤(03 A1 00 3D 97 55)。結合圖8中其它指令的發送和響應,可以看出,指令握手嚴格、響應及時,設計完全滿足成像系統的控制需求,具有較高的可靠性。

5 結束語

由于CAN總線結構簡單、通信速率高、可靠性好、連接方便、通信協議簡單,且具有統一的國際標準,被公認為最有前途的現場總線之一,因此,工業上得到了普遍的應用,近些年,隨著對CAN總線的認可,航天應用也越來越普遍。本設計通過FPGA控制SJA1000實現CAN總線通信,可擴展性好,穩定性高,降低了應用系統的重量、體積以及功耗,同時為了進一步提高CAN總線通信系統的可靠性,設計了基于雙SJA1000芯片的熱備結構,經過實際工程項目檢驗,證明了其良好的效果。目前,該控制系統已在工程項目中獲得了成功的應用。

[1]趙慶磊,龍科慧,韓誠山,等.空間TDICCD相機的在軌成像參數重注[J].航空學報,2014,35(8):2271-2278.

[2]韓紅霞,孫 航,曹立華.基于FPGA的紅外相機時序構造設計[J].液晶與顯示,2014,29(3):370-376.

[3]劉 鑫,林兆華,杜璧秀.CAN總線分布式自動調焦控制系統設計[J].國外電子測量技術,2014,33(8):44-48.

[4]毛 晴,梁 軍,劉 贊.基于FPGA的通用開放式星載陀螺模擬器設計[J].計算機測量與控制,2016,24(5):160-166.

[5]徐木水,劉金國.基于FPGA的CAN總線通信接口的設計[J].電子設計工程, 2010,18(18):96-99.

[6]孟 磊.基于CAN總線技術的汽車數字儀表的研究[D].西安:西安電子科技大學,2011.

[7]關俊強,左麗麗,吳維林.基于FPGA和CAN控制器軟核的CAN總線發送系統的設計與實現[J].計算機測量與控制,2016,24(3):281-284.

DesignofHighReliabilityImagingControlSystemBasedonCANBus

Li Hua1,3, Zhu Bo2, Zheng Peiyun2

(1.Shangluo University, Shangluo 726000, China;2.Xi′an Institute of Optics and Precision Mechanics, Chinese Academy of Sciences, Xi′an 710119, China;3.Xi′an Jiao tong University, Xi′an 710049, China)

In order to achieve intelligent control of many sets of imaging systems, this paper presents an imaging control system based on CAN bus,and introduces how to solve some problems of key technology on the design.Firstly, hardware design principle of high reliability thermal back-up CAN bus control system is given; Then, logic control principle and method of SJA1000 chip based on FPGA is introduced; Finally, combined with the actual engineering project the working process of the control system is expounded.Experimental results proved that this system has advantages of stable and reliable, which can achieve intelligent control of more than one imaging system.The concept and method of this design is versatile, so the system has good universality.

imaging system; CAN; FPGA; thermal back- up; timing

2017-03-24;

2017-04-10。

國家自然科學基金項目(61273366);陜西省自然科學基礎研究計劃(2016JM6060)。

李 華(1980-),女,陜西西安人,副教授,主要從事基于可編程邏輯器件的圖像處理相關與教學工作方向的研究。

1671-4598(2017)10-0069-04

10.16526/j.cnki.11-4762/tp.2017.10.019

TP274

A