基于XC6SLX45T平臺的PCIe數據卡設計

,,,

(南京南瑞集團公司,南京 211100)

基于XC6SLX45T平臺的PCIe數據卡設計

朱孟江,王元強,聶云杰,洪昊

(南京南瑞集團公司,南京 211100)

為提升數據傳輸速率、提高數據處理靈活性,提出一種基于FPGA的的PCIe數據卡設計方法。該方案選用Xilinx公司的XC6SLX45T平臺,采用IP核的方式設計了一款PCIe數據卡。該卡采用DMA傳輸模式,通過DMA讀寫提高傳輸速率,其數據傳輸速率可達到400 Mbps。

FPGA;IP核;PCIe;DMA

引 言

PCI-Express(簡稱PCIe)總線的出現,完全地改變了原本的PCI總線的并行技術,PCIe采用的是新型的串行點對點技術,改善了PCI總線傳輸速度以及系統帶寬方面的本質問題。PCIe總線的提出,彌補了PCI總線的不足之處,PCIe總線將發展成為取代PCI總線的新型數據總線[1]。

目前電力行業業務復雜、數據繁多,根據電監會5號令《電力二次系統安全防護規定》的要求,各發電企業、電網企業、供電企業內部基于計算機和網絡技術的業務系統在安全區I和安全區II之間以密文的方式進行通信。軟件密碼算法不僅消耗硬件CPU資源,且存在較大安全隱患,速度也受硬件資源的限制,這就需要設計一款高效、快速的硬件數據加密卡。目前市場上數據對稱加解密速度均在400 Mbps左右, SPI、UART等串行接口性能遠遠不夠,USB和以太網又不方便集成到服務器,因此選用Xilinx PCIe解決方案,同時FPGA在數據處理方面也具有很大的靈活性。

本文將以Xilinx公司的Spartan-6為平臺,闡述PCIe IP Core的方案及其優化策略,并著重描述其DMA和傳統終端模式,配合上位機測試程序進行相關數據測試。該方案具有方便、可集成性、速度快等優點,已在電力調度系統中得到廣泛的應用。系統集成示意圖如圖1所示。

圖1 系統集成示意圖

1 PCIe原理

1.1 PCIe簡介

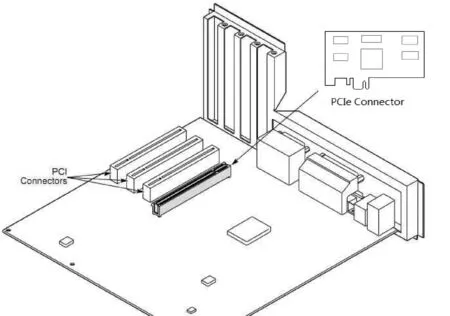

與PCI總線不同,PCIe總線使用端到端的連接方式,在一條PCIe鏈路的兩端只能各連接一個設備,這兩個設備互為數據發送端和數據接收端。PCIe總線除了總線鏈路外,還具有多個層次,發送端發送數據時將通過這些層次,而總線接收端接收數據時也使用這些層次。PCIe總線使用的層次結構與網絡協議棧較為類似,由事物層、數據鏈路層和物理層組成。PCIe發送端和接收端中都含有TX(發送邏輯)和RX(接收邏輯),其結構如圖2 所示。

圖2 PCIe總線物理鏈路

1.2 PCIe IP核

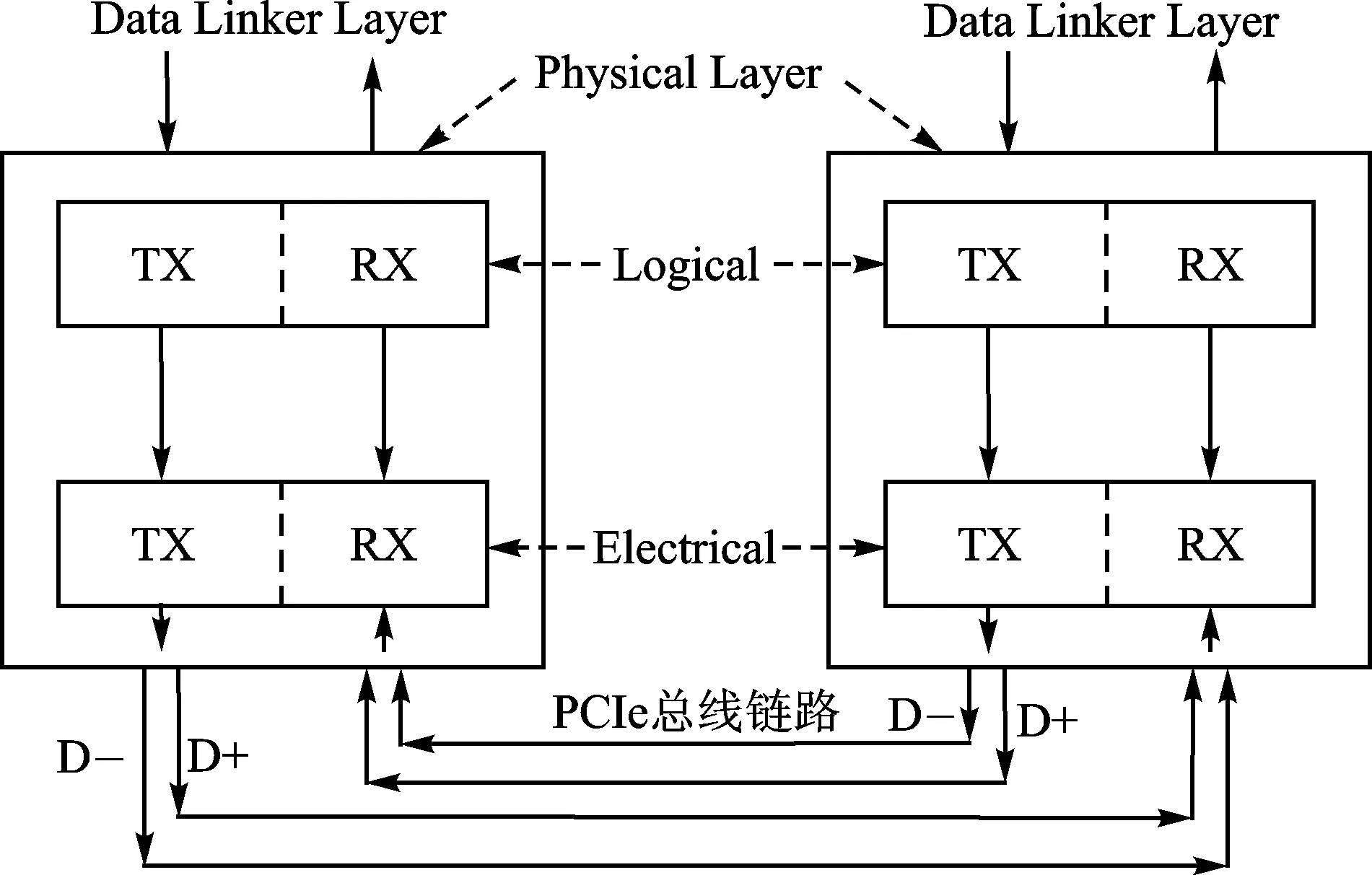

用FPGA實現PCIe功能,簡單地說就是完成TLP包的處理,即事物層數據協議的處理。TLP由三部分組成:幀頭、數據、Digest段。

TLP幀頭長為3或者4個DW,格式和內容隨事物類型變化。數據段為TLP 幀頭定義下的數據段,如果該TLP不攜帶數據,則該段為空。Digest段(Optional)是基于幀頭、數據字段計算出來的CRC,又稱為ECRC,一般Digest段由IP 核填充,所以PCIe的處理在用戶層表現為處理TLP中幀頭和數據段。TLP包中各個字段含義不再一一解釋,可參照《PCI Express體系結構導讀》一書。TLP格式如圖3所示。

圖3 TLP格式

1.3 PCIe接口空間配置

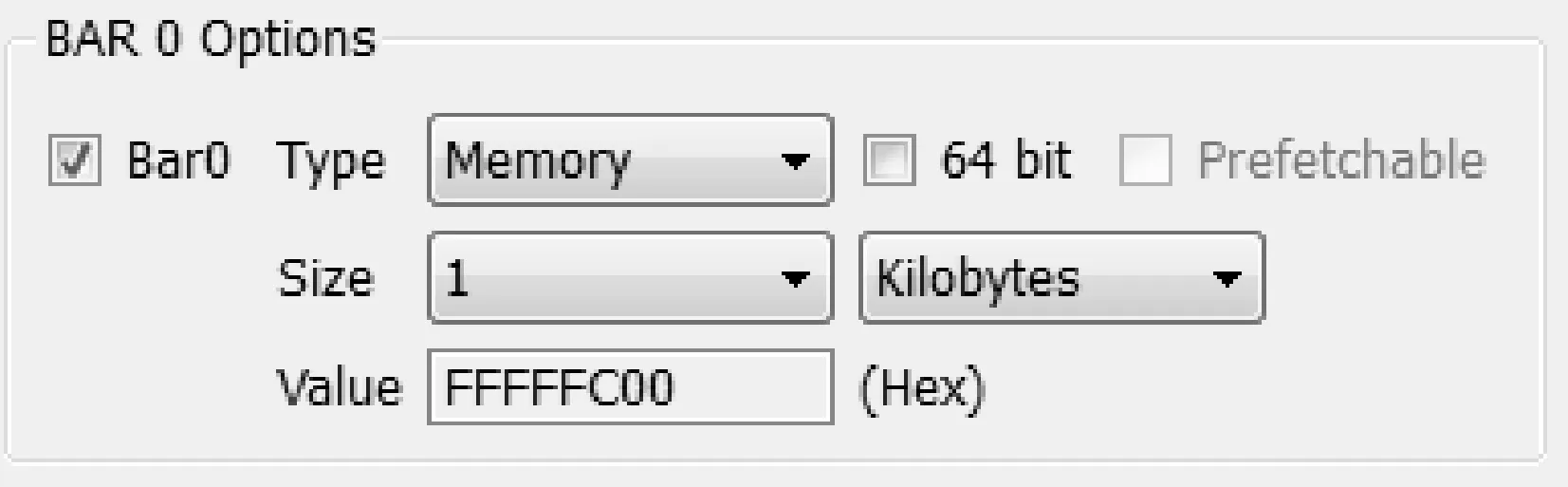

PCIe通信是靠發送TLP包完成的,讀寫包里都有地址信息。如果板卡向PC發送TLP包,例如MWr包,那很好理解,地址信息就是PC的物理地址;如果是MRd包,則PC收到后回復一個完成包,板卡從完成包分析出數據即得到MRd讀取地址的數據。那PC如何讀寫板卡的數據呢? PC啟動時BIOS探測所有的外設。對PCIe設備來說,BIOS檢測到板卡有多少個BAR(Base Address Register)空間,每個空間有多大,然后對應為這些BAR空間的分配地址。對PC設備來說,它能“看”到PCIe板卡的空間只有BAR空間,只能訪問這些BAR空間。板卡可以發送合法的PCIe TLP包,并得到PC端的響應,但是PC端訪問板卡被局限在BAR空間。本方案PCIe BAR空間僅設置為BAR0空間,配置如圖4所示。

圖4 BAR0空間設置

2 程序設計

2.1 PCIe設備驅動

PCIe設備驅動與PCI一樣,與普通設備驅動沒有太大差別,具備open、close、ioctl、read、write等接口函數,實現方式大同小異。與普通字符設備驅動的區別主要在probe函數上,PCIe設備驅動比普通字符設備驅動多了一個probe探測函數,該函數主要有如下功能:

◆ 驅動加載時,將PCIe的BAR0空間映射到主機并為DMA申請內存空間;

◆ 為PCIe設備申請中斷,并分配中斷號;

◆ 初始化驅動讀寫隊列。

PCIe設備驅動代碼如下:

static int __devinit fpga_probe(struct pci_dev *pdev, const struct pci_device_id *id){

……

pci_enable_device(pdev);//enable PCIe

pci_set_master(pdev); //設置成總線主DMA模式

……

PhysicalBase0Addr=pci_resource_start(pdev,BAR_0);

PhysicalBase0len=pci_resource_len(pdev,BAR_0); //將PCIe內存空間映射到主機

fpga_priv.PCI_Base0_Addr=ioremap( PhysicalBase0Addr, PhysicalBase0len);

fpga_priv.dma_buf = pci_alloc_consistent(pdev,PKT_LEN,&fpga_priv.dma_buf_t);

if(fpga_priv.dma_buf==NULL)

return ERROR;

init_waitqueue_head(&fpga_priv.read_wait);//初始化讀隊列

init_waitqueue_head(&fpga_priv.write_wait); //初始化寫隊列

fpga_priv.irq = pdev->irq;//為PCIe設備申請中斷號

request_irq(fpga_priv.irq, fpga_interrupt,IRQF_SHARED,"FPGA",& fpga_priv);

……

}

2.2 DMA驅動程序

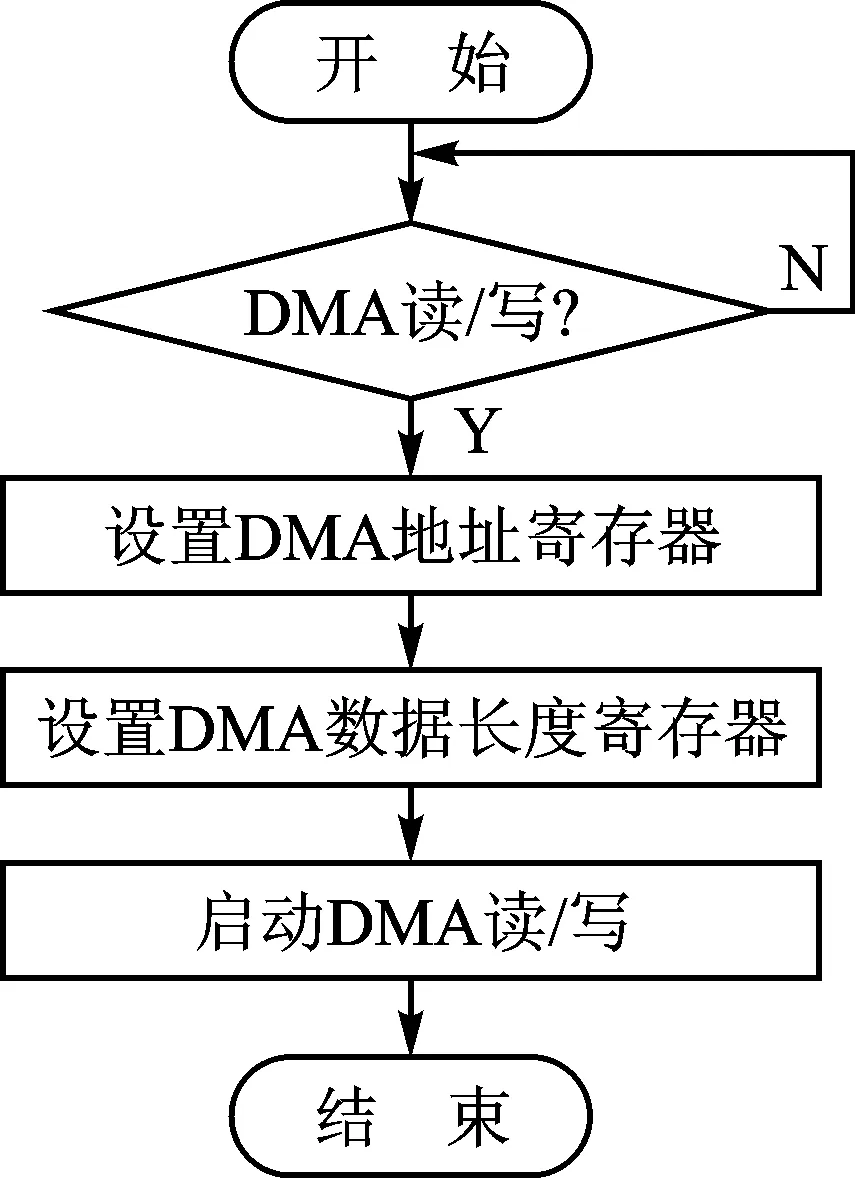

圖5 DMA操作流程

DMA(Direct Memory Access,直接內存訪問)不需要處理器的干預,處理器只需將讀/寫數據首地址和數據長度告訴DMA控制器,啟動DMA讀/寫即可[2]。本設計在FPGA內部設置了DMA讀寫寄存器和DMA地址寄存器,其操作過程如圖5所示。

DMA程序實現如下[3]:

int DMA_operation (int len, int i){

int val;

PCIe_InitiatorReset();

//對FPGA軟復位

TLP_cnt = (len%TLP_SIZE) ? (len/TLP_SIZE+1) : len/TLP_SIZE;

TLP_cnt += 1;

//計算PCIe傳輸TLP包大小

PCIe_WriteReg(DMA_LEN_REG, len);

//設置DMA數據長度,地址為默認地址

PCIe_WriteReg(RDMATLPC, TLP_cnt);

//設置TLP傳輸包數

PCIe_WriteReg(BUFCONTROL1, 0x101);

//使能DMA讀/寫操作

PCIe_WriteReg(DMACR, 0x10000);

do {

val = PCIe_ReadReg(BUFSTATE1);

} while(val==0x0);

//等待DMA完成

PCIe_WriteReg(BUFCONTROL1, 0);

//disable讀/寫操作

return 0;

}

2.3 FPGA中斷狀態機設計

PCIe可以發出兩種中斷,一種是虛擬INTx信號線的,另一種是MSI的。過去PCI板卡發送中斷通過拉低INTx(INTA#、INTB#、INTC#、INTD#)來申請中斷,PC檢測到INTx的中斷,就跳轉執行INTx對應的中斷驅動程序。MSI是基于消息機制的,PC啟動后為PCIe板卡分配一個或多個消息地址,板卡發送中斷只需要向對應的地址內發送消息,消息內容中包含消息號,每個消息號對應在PC 端的某一地址。需要注意的是,Windows XP是不支持MSI的,到了WinNT和Win7才支持,因此本方案采取INTx傳統中斷方式。

中斷程序采用狀態機控制,正常情況下處于等待狀態,當用戶應用程序提交中斷申請時,將request信號傳遞給狀態機,觸發中斷;當PC收到PCIe中斷時,必須在中斷服務程序給FPGA一個確認信號,并在讀/寫完成之后清除該確認信號,以便FPGA可以進入下一次中斷請求。

用戶中斷請求信號intr_req,當讀/寫完成時,提交中斷請求,如下:

assign intr_req = ((rd_done=1'b1) || (wr_done==1'b1)) ? 1'b1 : 1'b0;

intr_req信號傳遞到中斷程序狀態機,如下:

always @(posedge clk ) begin

case (crypt_intr_state)/*狀態機狀態*/

`BMD_INTR_CRYPT_RST : begin

if(intr_req )//用戶應用的中斷請求

next_crypt_intr_state = `BMD_INTR_CRYPT_ACT0;

end

`BMD_INTR_CRYPT_ACT0 : begin

……

end

`BMD_INTR_CRYPT_ACT1 : begin

if (cfg_interrupt_ack)//等待PC確認收到中斷請求

next_crypt_intr_state = `BMD_INTR_CRYPT_ACT2;

end

`BMD_INTR_CRYPT_ACT2 : begin

……

end

`BMD_INTR_CRYPT_DUN : begin

//等待PC清除確認標志,否則不能進入下一中斷

if((!cfg_interrupt_ack)||(timeout_cnt == TIMEOUT))

next_crypt_intr_state = `BMD_INTR_CRYPT_RST;

end

default:

next_crypt_intr_state = `BMD_INTR_CRYPT_RST;

endcase

end

整個狀態機操作如下:

① 在BMD_INTR_CRYPT_ACT0狀態下,用戶應用將cfg_interrupt_n和cfg_interrupt_assert_n置為有效,從而將中斷置為有效。

② 然后,核將cfg_interrupt_rdy_n置為有效,表示已接受中斷請求。在BMD_INTR_CRYPT_ACT1狀態,用戶應用將cfg_interrupt_n置為無效;此時如果PCI命令寄存器中的中斷禁用位設置為 0,則核發出將中斷置為有效的消息。

③ 在BMD_INTR_CRYPT_ACT2狀態,用戶應用一旦確定中斷請求已被接收,就會將cfg_interrupt_n置為有效,同時將 cfg_interrupt_assert_n置為無效,從而將中斷置為無效。必須通過 cfg_interrupt_di[7:0]來指示相應的中斷。

④ 核將cfg_interrupt_rdy_n置為有效,表示已接收中斷的無效置位。在BMD_INTR_CRYPT_DUN,用戶應用將cfg_interrupt_n置為無效,而核發出將中斷置為無效的消息。

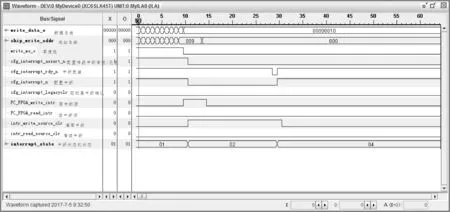

以一次數據寫為例,其信號時序仿真如圖6所示。

圖6 傳統中斷時序圖

通過對IP Core的中斷配置接口操作,PC就會接到相關中斷信息,使主機進入中斷服務程序進行處理。本設計采用狀態機的方式產生中斷信號,在FPGA內部設計中斷寄存器,正常情況下FPGA中斷處于等待狀態,當FPGA處理完數據后將中斷寄存器置位,要求PC去讀數據,此時狀態機處于中斷程序狀態,當PC接收到中斷并進入到中斷服務程序時,清除該中斷寄存器,狀態機再次恢復到等待狀態,可以進行下一次中斷。

3 實驗測試

實驗主機為DELL臺式機,CPU為奔騰D處理器,主頻2.80 GHz,內存2 GB,操作系統為Ubuntu9.10,內核版本2.6.31。

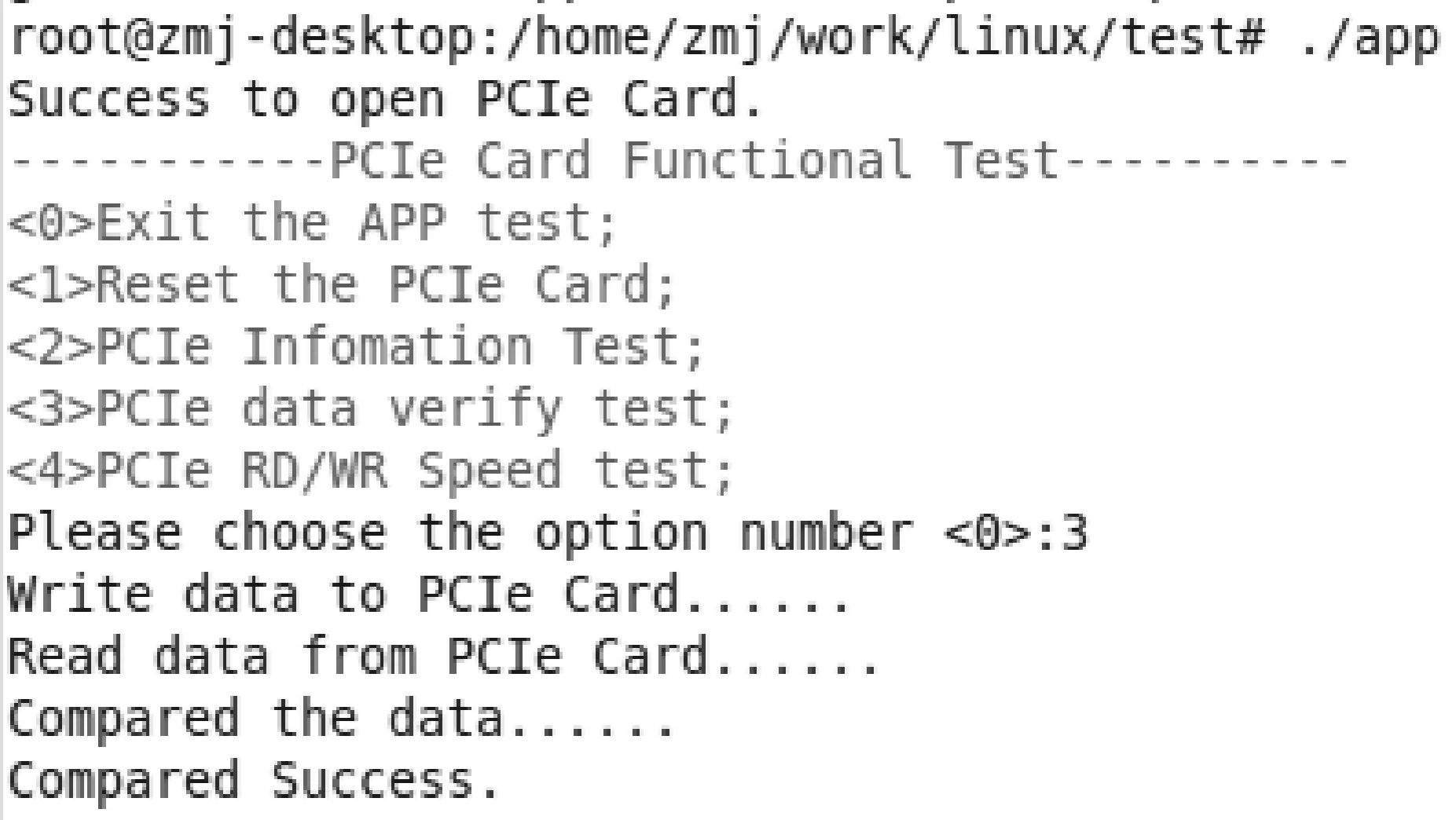

測試方法1如下:

將PCIe卡插到臺式機主板插槽,在Linux下加載PCIe卡驅動程序;系統產生2048字節隨機數,向PCIe卡中寫入隨機數,卡接收到隨機數并緩存到FPGA的雙口RAM中進行存儲;從PCIe卡的雙口RAM讀數據,數據長度與寫入保持一致;將讀出數據與寫入數據進行比對,若一致,則讀寫正確,否則錯誤。

數據正確性驗證測試如圖7所示。

圖7 數據正確性驗證測試

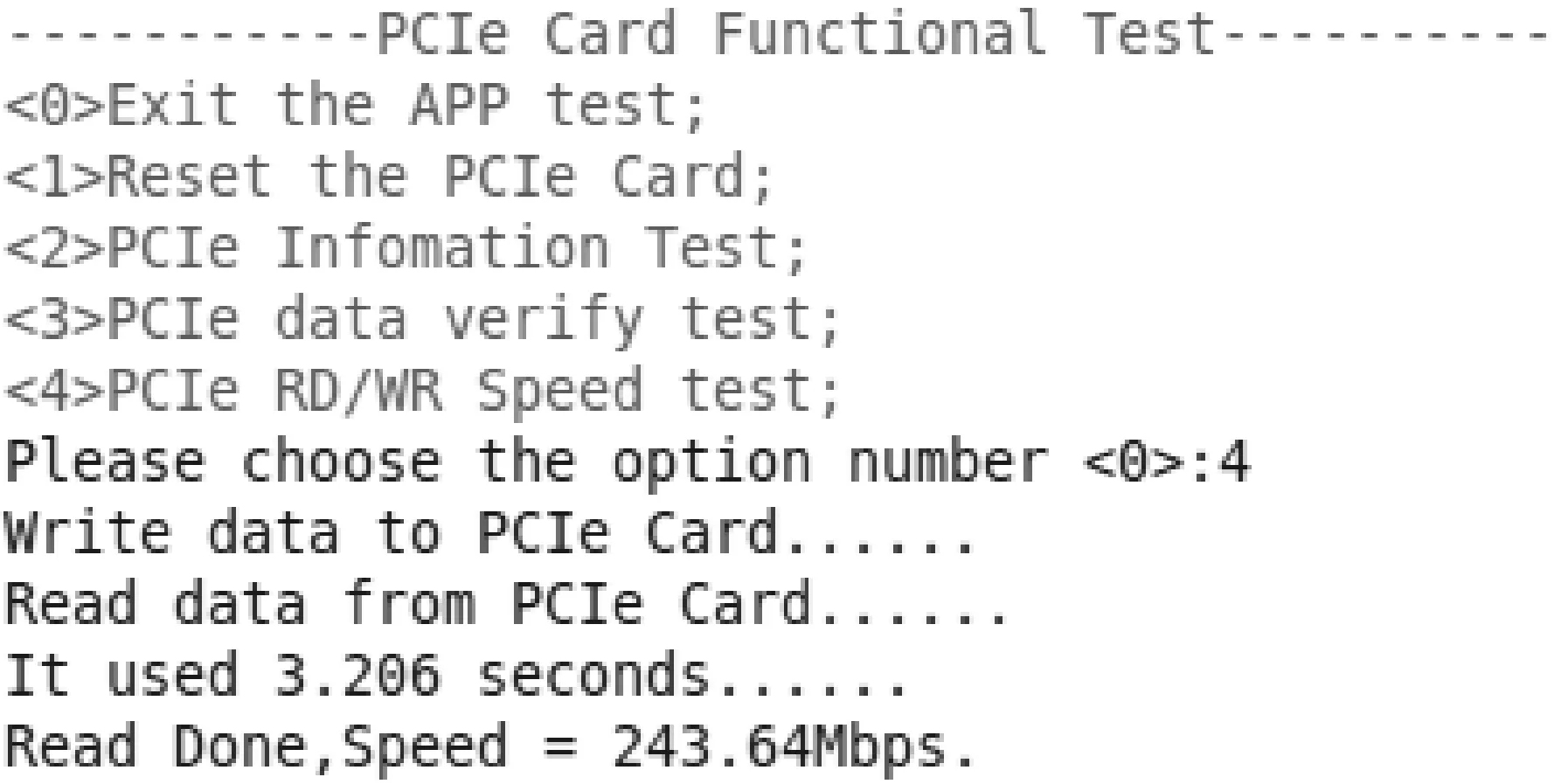

測試方法2如下:

將PCIe卡插到臺式機主板插槽,在Linux下加載PCIe卡驅動程序;系統產生2 048字節隨機數;系統計時,向PCIe卡中寫入隨機數,卡接收到隨機數并緩存到FPGA的雙口RAM中進行存儲;從PCIe卡的雙口RAM讀數據,數據長度與寫入保持一致;循環上兩步10萬次,待結束計算所用時間;根據時間與所寫數據量,計算PCIe卡讀寫速度。

PCIe卡傳輸速度測試如圖8所示。由于傳輸速度測試采用雙向先寫后讀方式,因此實際單向讀或寫的速度應為實測速度的兩倍左右,遠大于400 Mbps。

結 語

[1] 李木國,黃影,劉于之.基于FPGA的PCIe總線接口的DMA傳輸設計[J].計算機測量與控制,2013,21(1):233-235.

[2] 王曉慶,周曉波,趙強.PCIE高速數據采集系統的驅動及上位機軟件開發[J].計算機應用與軟件,2013(9):331-333.

[3] 李晃,鞏峰,陳彥化.基于PCIE驅動程序的數據傳輸卡DMA傳輸[J].電子科技,2014,27(1):117-120.

朱孟江、王元強、聶云杰、洪昊,主要研究方向為電力系統信息安全設計開發。

DesignofPCIeDataCardBasedonXC6SLX45TPlatform

ZhuMengjiang,WangYuanqiang,NieYunjie,HongHao

(NARI Group Corporation,Nanjing 211100,China)

To improve the transmission rate and the flexibility of data processing,a design method of PCIe data card based on FPGA is proposed in the paper.The scheme adopts the way of IP core on Xilinx XC6SLX45T platform.The card transmission mode uses the DMA mode,which can enhance the transmission speed,which is as high as 400 Mbps.

FPGA;IP Core;PCIe;DMA

TP336

A

2017-08-07)

圖8 PCIe卡傳輸速度測試