用FPGA實現(xiàn)儀表用DDS信號源的ASIC設(shè)計*

,

(湖南科技學(xué)院 電子與信息工程學(xué)院,永州 425199 )

用FPGA實現(xiàn)儀表用DDS信號源的ASIC設(shè)計*

包本剛,朱湘萍

(湖南科技學(xué)院 電子與信息工程學(xué)院,永州 425199 )

ASIC可以采用全定制和半定制的方法加以實現(xiàn),采用FPGA來進(jìn)行ASIC的可測試設(shè)計,可以很大程度上節(jié)約ASIC設(shè)計的成本。本文介紹了一種基于FPGA實現(xiàn)的DDS信號源的ASIC的設(shè)計方案,它可以靈活地輸出任意波形,并可以較方便地改變波形的頻率和相位。該方案可以嵌入到采用FPGA芯片實現(xiàn)的儀器儀表中,具有結(jié)構(gòu)簡單、功能強(qiáng)大、性價比高的特點,稍加改動可適用于許多儀器儀表系統(tǒng)中,具有很好的可移植性。

FPGA;DDS;ASIC;信號源;Verilog

引 言

近年來,可編程邏輯器件的廣泛使用引發(fā)了電子產(chǎn)品領(lǐng)域的一場新的革命。可編程邏輯器件具有設(shè)計靈活、速度快、更改方便、功耗低等優(yōu)點,在數(shù)字系統(tǒng)的設(shè)計中得到了廣泛的應(yīng)用,逐步會替代中、小規(guī)模的數(shù)字集成芯片[1]。

在許多儀器儀表中都要用到信號源,目前通常是采用專用的DDS芯片來實現(xiàn),但是這種芯片功能固定,不利于嵌入式應(yīng)用。而且,在儀器儀表的許多應(yīng)用場合已經(jīng)采用了FPGA可編程芯片,為我們在已經(jīng)使用了且還有硬件空間的FPGA器件中再嵌入一個信號源提供了極大的方便,不僅不會增加成本,而且可以使系統(tǒng)結(jié)構(gòu)更加簡單、體積更小、成本更低,具有很好的可移植特性。

1 DDS波形發(fā)生器的理論介紹

直接數(shù)字頻率合成(DDS)是一種以數(shù)字信號處理為基礎(chǔ),從相位的概念出發(fā)直接合成所需波形的一種全新的數(shù)字頻率合成技術(shù)。圖1是DDS的原理框圖基本結(jié)構(gòu)。它主要由相位累加器、相位寄存器、 加法器、正弦查找表、D/A轉(zhuǎn)換器及濾波電路構(gòu)成[8]。每來一個時鐘信號,相位累加器中的值便與頻率控制字M相加,得到當(dāng)前的相位值(ROM地址)。如果記數(shù)大于2N,則自動溢出;LUT(查找表)是一個波形幅度量化數(shù)據(jù)存儲器(ROM), 實現(xiàn)相位到幅度的轉(zhuǎn)換。相位累加器的輸出作為LUT的地址, LUT根據(jù)相位累加器的輸出(地址)讀出幅度信號, 送到D /A轉(zhuǎn)換器中轉(zhuǎn)換為模擬量, 最后通過濾波器輸出一個平滑的模擬信號。

頻率控制字越大,相位累加器的輸出(ROM的地址)變化越快,從而輸出的波形頻率越高。下面用正弦波信號產(chǎn)生原理來敘述DDS技術(shù)。

采用下式來描述一個簡單的正弦信號:

式中的時間t是在時間軸上連續(xù), 為了用數(shù)字方式實現(xiàn), 應(yīng)該進(jìn)行離散化處理。用周期為Tclk的基準(zhǔn)時鐘對信號進(jìn)行采樣, 采樣頻率fclk=1/Tclk,連續(xù)兩個采樣點之間的相位增量為:

將整個周期2π分成2N份, 則相位的量化單位(相位增量)δ=2π/2N。若Δθ=δ, 代入式(2)可得f0=fclk/2N。更特殊的情況是Δθ為δ的Μ倍, 即可得到輸出信號的頻率:

式中,M稱為頻率控制字(tuning word)。輸出信號的頻率由M決定, 且兩者呈線性關(guān)系。若采樣頻率不變,通過控制兩次連續(xù)采樣點之間的相位增量(即通過頻率控制字M),即可控制離散波形序列的頻率,再經(jīng)保持和濾波,可準(zhǔn)確的恢復(fù)出此頻率的模擬信號波形。DDS原理圖如圖1所示。

圖1 DDS原理圖

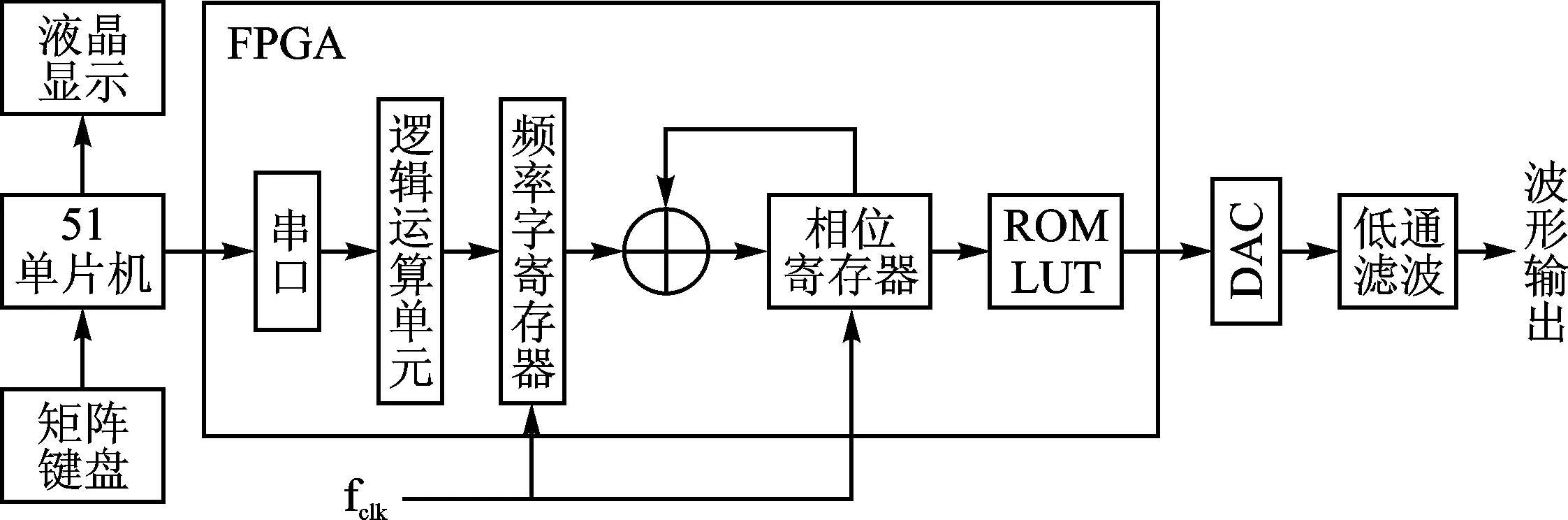

2 基于FPGA的系統(tǒng)總體設(shè)計方案

系統(tǒng)總體框圖如圖2所示,本設(shè)計以FPGA為核心,首先在FPGA中定制好ROM,并將量化的波形數(shù)據(jù)存到

圖2 系統(tǒng)總體框圖

ROM中,然后單片機(jī)通過串口將頻率字M發(fā)給FPGA,經(jīng)相位累加器實現(xiàn)ROM地址的累加,再經(jīng)地址計數(shù)器尋址讀出波形數(shù)據(jù),控制地址計數(shù)器的時鐘頻率便可控制采樣的點數(shù),從而控制輸出波形的頻率[7]。

考慮到這些數(shù)據(jù)為純數(shù)字量,需要經(jīng)D/A轉(zhuǎn)換才能將其轉(zhuǎn)換為模擬量,再通過低通濾波器濾除階梯與噪聲方可輸出滿足要求的波形[10]。由于本設(shè)計采用直接頻率合成(DDS)技術(shù),用一片EPROM存儲波形數(shù)據(jù),設(shè)定頻率字便可設(shè)定波形,使得輸出波形的頻率范圍得到了拓寬,精確度顯著提高,系統(tǒng)穩(wěn)定可靠。

3 基于FPGA的DDS信號源的內(nèi)部子模塊設(shè)計

3.1 DDS內(nèi)核的設(shè)計

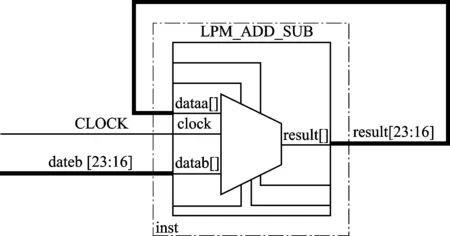

3.1.1 相位累加器

在時鐘的作用下,相位累加器進(jìn)行相位累加(相位寄存器的值加上頻率字),當(dāng)相位累加器的值累加滿時就會產(chǎn)生一次溢出,從而完成一個周期性的動作,得到DDS合成信號的一個頻率周期,DDS輸出的信號頻率即累加器的溢出率。FPGA中的相位累加器模塊如圖3所示。

圖3 相位累加器

圖4是相位累加器仿真圖,從圖中可以看出,在時鐘的激勵下,累加器的仿真結(jié)果是正確的。

圖4 相位累加器的仿真結(jié)果

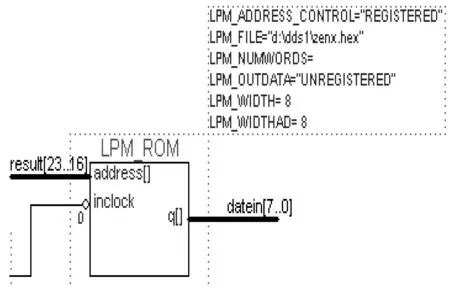

3.1.2 波形存儲器

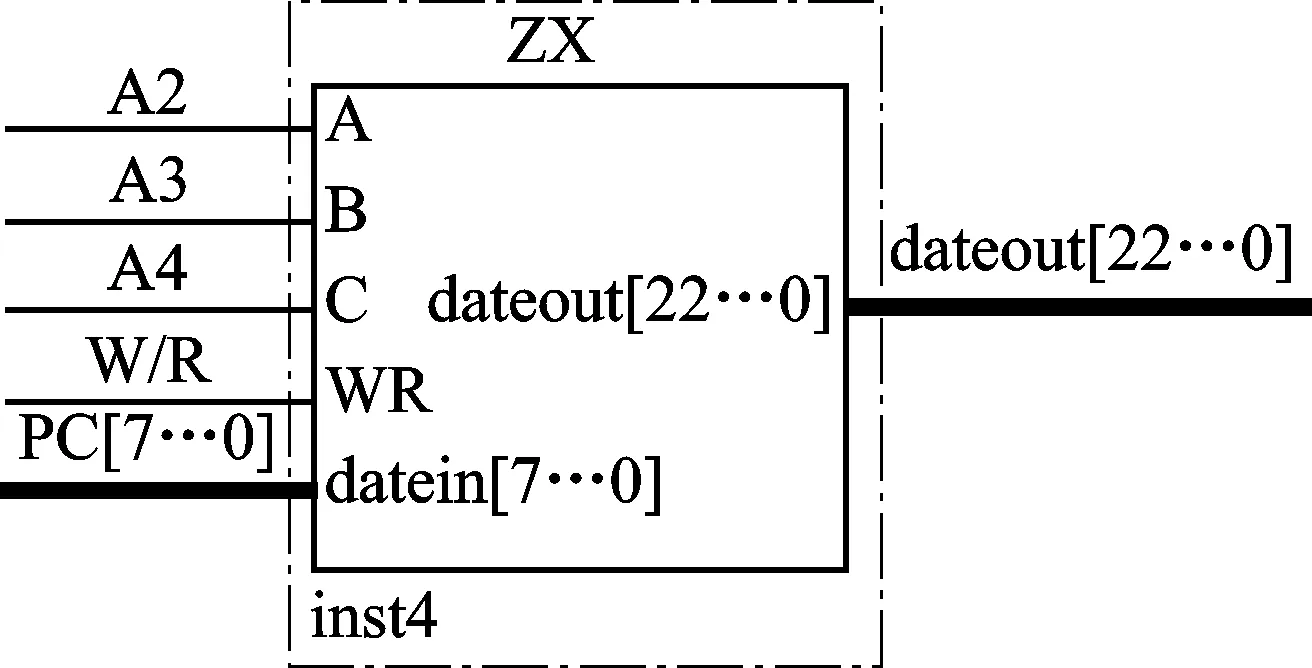

波形存儲器即在FPGA上調(diào)用的一個ROM,所生成波形一周期采樣256點的數(shù)據(jù)值放在了波形存儲器里面,通過讀取ROM的地址值,便可以得到波形的數(shù)據(jù)。地址改變,輸出的值也會隨之變化。在同樣的時鐘周期下,地址間隔的變化,生成波形的頻率也跟著變化。地址值每溢出一次,便完成了一個周期的輸出。改變波形的一個方法是改變波形存儲器中的波形數(shù)據(jù)。波形存儲器如圖5所示。

圖5 ROM模塊

ROM的設(shè)計直接調(diào)用LPM中的宏生成,端口分別為:時鐘輸入端inclock、輸出數(shù)據(jù)總線datein[7:0]、輸入數(shù)據(jù)總線result[23:16]。地址總線result[23:16]是相位累加器輸出高8位的數(shù)據(jù)。輸出數(shù)據(jù)總線datein[7:0]連接輸出緩沖通過FPGA的I/O口輸出,連接作為D/A轉(zhuǎn)換器的輸入端口。

3.1.3 頻率字寄存器

圖6 頻率字寄存器

頻率字寄存器的功能較簡單,即接收從單片機(jī)中傳來的增量寄存器的控制字。用Verilog語言描述這個模塊的底層,然后在頂層生成相應(yīng)的功能模塊。其生成的模塊圖如圖6所示。

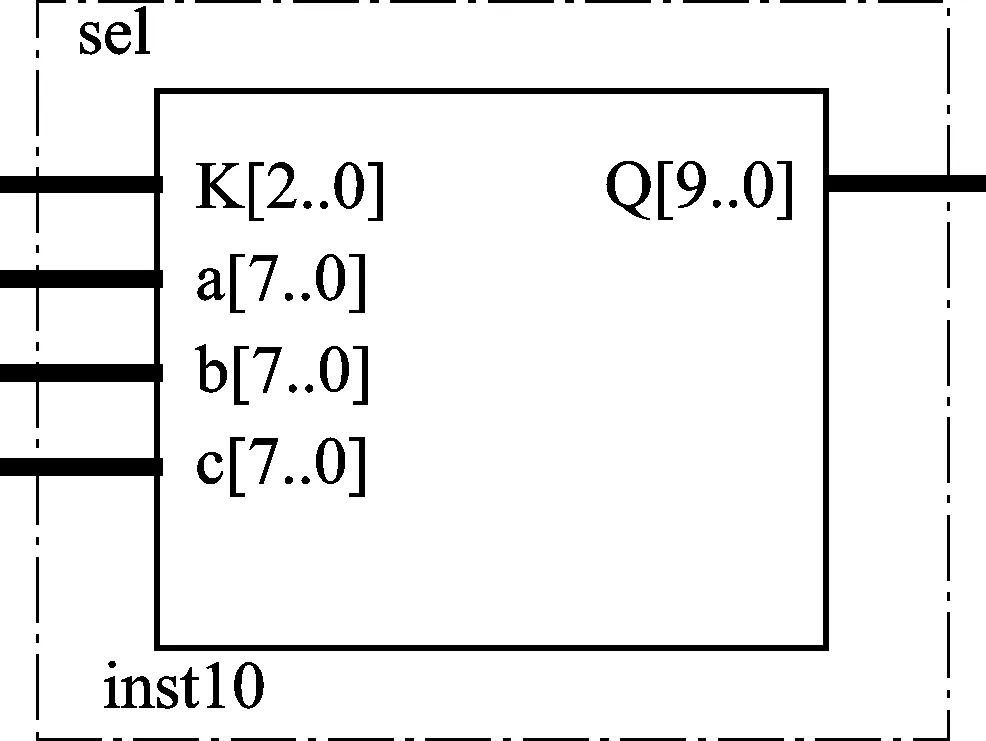

3.1.4 波形選擇模塊

這個模塊的功能是通過按鍵選擇三種波形,其生成的模塊圖如圖7所示。

3.2 UART模塊的設(shè)計

圖7 波形選擇模塊

作為各種微處理芯片最常用的一種異步通信接口,UART串行接口只需要兩根線即可,非常節(jié)約系統(tǒng)的資源,而且FPGA的主頻較高,即使傳輸?shù)臄?shù)據(jù)位數(shù)較多也不會工作于忙碌狀態(tài),所以此處選擇串口建立FPGA與單片機(jī)之間的通信。

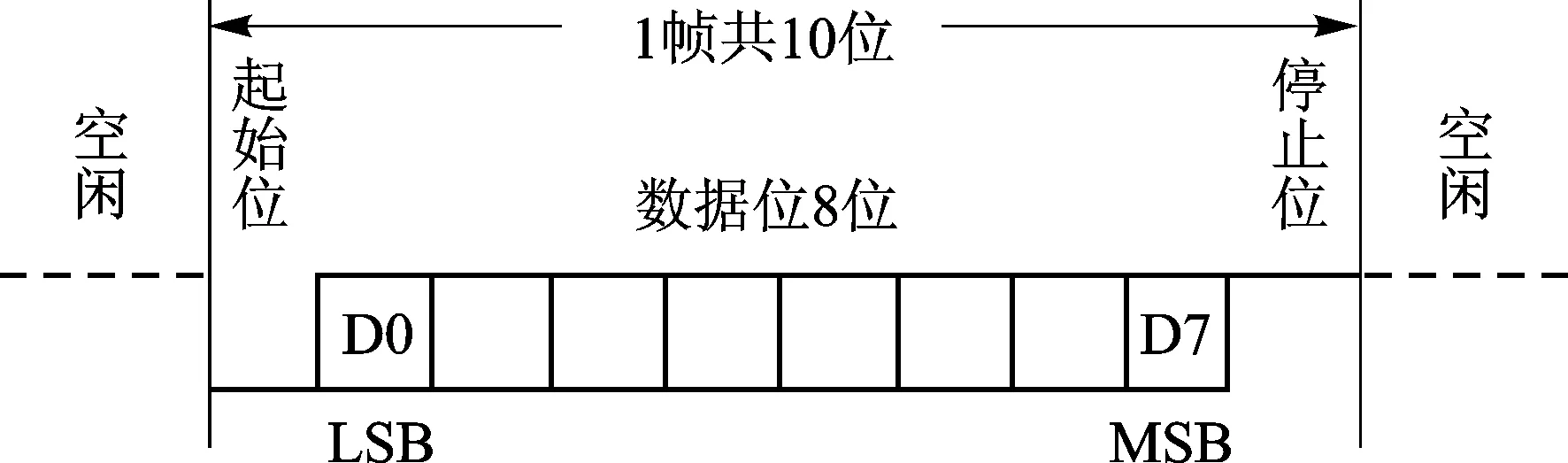

3.2.1 UART收發(fā)時序

串口收發(fā)數(shù)據(jù)需要遵循一定的時序,其時序圖如圖8所示。當(dāng)UART接收時,接收一幀數(shù)據(jù)的中間8位是有效數(shù)據(jù),開始位與停止位用于護(hù)送數(shù)據(jù);在UART發(fā)送時,將發(fā)送的并行8位數(shù)據(jù)轉(zhuǎn)為串行數(shù)據(jù),并添加開始位與停止位。UART中的一幀數(shù)據(jù)為10位,空閑時均為高電平,系統(tǒng)在檢測到低電平(開始位)之后,開始逐位采集8位有效數(shù)據(jù)位(低位在前),再將停止位置為高電平即可。

圖8 UART收發(fā)時序

3.2.2 RTL級的UART設(shè)計

在搭建好UART各個子模塊之后,可以建立一個頂層文件,分別調(diào)用各個底層模塊組成UART模塊,其總體框圖如圖9所示。

圖9 UART總體框圖

4 測試方法及結(jié)論

按照圖2搭建好系統(tǒng)電路,編寫好單片機(jī)控制程序,在Keil 4軟件環(huán)境編譯通過后,通過串口下載線把程序下載到單片機(jī)STC15F2K61S2中。然后把單片機(jī)串口引腳(P3~1)與FPGA指定配置的串口引腳連接好,把編譯好的.sof下載到目標(biāo)器件EP2C5Q208C8。最后把FPGA開發(fā)板與D/A轉(zhuǎn)換模塊連接好,D/A輸出端口連到示波器輸入端,便可以直接在示波器上觀察輸出波形。經(jīng)過測試,可以非常方便地看到1~5 MHz頻率可調(diào)的正弦波、三角波和矩形波。

[1] 朱湘萍,包本剛.基于FPGA的儀表用多功能數(shù)字時鐘的嵌入設(shè)計[J].電測與儀表,2008,45(1):62-64.

[2] 黃智偉,王彥.FPGA系統(tǒng)設(shè)計與實踐[M].北京:電子工業(yè)出版社,2005.

[3] James R,Armstrong F.Gail Gray. VHDL設(shè)計表示和綜合[M]. 李宗伯,王蓉暈,譯. 北京:機(jī)械工業(yè)出版社,2002.

[4] 郭麗浩.基于FPGA的直接數(shù)字頻率合成器的研究與應(yīng)用[D].西安:西北工業(yè)大學(xué),2006.

[5] 胡力. 基于DDS的掃頻信號源設(shè)計與實現(xiàn)[D].南京:南京理工大學(xué),2006.

[6] 宋陽, 孫肖子, 仁愛鋒. 基于DDS 和FPGA 的虛擬智能信號源的研究[J] . 數(shù)據(jù)采集與處理, 2001, 16(s1):124-126.

[7] 王宏軍,王航宇. 基于FPGANios_的信號發(fā)生器設(shè)計[J]. 國外電子元器件,2008 (10):54-56.

[8] 胡繼勝, 李洪. 基于 SoPC/NIOS II 的信號發(fā)生器設(shè)計與實現(xiàn)[J]. 電子技術(shù)應(yīng)用,2011,37(6):91-94.

[9] 林萬榮. 基于 AD9850 的 DDS 信號發(fā)生器系統(tǒng)設(shè)計與實現(xiàn)[J]. 中國有線電視, 2015(11):1286-1290.

[10] 李偉英,鐘新躍, 謝四蓮,等. 基于 DDS 技術(shù)的信號發(fā)生器設(shè)計與實現(xiàn)[J].電子工程師,2008(5):35-37.

包本剛(副教授),主要研究方向為集成電子電路設(shè)計和集成電路測試的研究;朱湘萍(講師),主要研究方向為集成電子電路設(shè)計和新型材料。

ASICDesignofDDSSignalSourceforInstrumentBasedonFPGA

BaoBengang,ZhuXiangping

(Department of Physics and Electrical Engineering,Hunan University of Science and Engineering,Yongzhou 425199,China)

ASIC can be implemented using both the full-custom and the semi-custom methods.FPGA can be used to test the design of ASIC,which can greatly save the cost of ASIC design.In the paper,a design scheme of ASIC for DDS signal source based on FPGA is introduced,which can flexibly output arbitrary waveform and can easily change the frequency and phase of the waveform.The scheme can be embedded in the instrument realized by FPGA chip and the design has the advantages of simple structure,powerful function and high performance price ratio.After doing a little change of the scheme,it can be applied to many instrumentation systems and it has good portability.

FPGA;DDS;ASIC;signal source;Verilog

湖南科技學(xué)院重點學(xué)科建設(shè)項目資助(電路與系統(tǒng))(項目編號:20170912)。

TP216

A

2017-06-19)