電流模式的高階曲率補償CMOS帶隙基準源

張普杰,王衛東,李耀臻

(桂林電子科技大學 信息與通信學院,廣西 桂林 541004)

電流模式的高階曲率補償CMOS帶隙基準源

張普杰1,王衛東2,李耀臻3

(桂林電子科技大學 信息與通信學院,廣西 桂林541004)

因為傳統的帶隙電壓基準源只經過了一階溫度補償,且輸出電壓只能在1.2V左右,所以為了得到一個可調的、更高精度的電壓基準源,提出了電流模式的帶隙電壓基準源電路。電路采用了高階曲率補償方法,且輸出的基準電壓可根據輸出電阻的大小進行調節。電路采用gpdk090CMOS工藝,通過Spectre仿真,當電源電壓為3.6V、在-60℃~-120℃溫度范圍內、溫度系數為14.4×10-6/℃ 時電源電壓抑制比為78.3dB,輸出電壓平均為1.162V。

帶隙電壓基準源;高階曲率補償;溫度系數;電壓抑制比

0 引言

基準源是模擬集成電路設計中經常用到的重要電路,分為電壓和電流基準源。因為基準源與電源電壓、工藝模型、環境溫度基本無關,并且基準源有高的電源抑制比和低的溫度系數,所以可以為電路提供穩定的電壓或電流,在A/D或D/A轉換模塊、LDO(低壓差線性穩壓器)、SOC(系統集成芯片)等系統中扮演著非常重要的角色。

傳統的帶隙基準源是把具有負溫度系數的電壓(VBE)與具有正溫度系數的電壓(ΔVBE)分別加以不同的權重然后相加,使兩者相抵消,從而獲得與溫度無關的電壓。但傳統的帶隙電壓基準源也有一個缺點,當具有不同溫度系數的電壓相抵消時,會得到一個1.2 V左右的電壓,這時如果電源提供的電壓接近1.2 V時該帶隙基準源就不適用了。為了能獲得輸出可控的基準電路,本文基于電流模式電路提出一種具有高階溫度補償的、輸出電壓可調的帶隙基準電壓源電路。

1 傳統的帶隙電壓基準源結構

正如上文提到的,典型的帶隙電壓基準源電路是把具有負溫度系數的電壓(VBE)與具有正溫度系數的電壓(ΔVBE)分別加以不同的權重然后相加,使兩者相抵消,從而獲得與溫度無關的電壓(理論上在某一確定溫度下的溫度系數為0,一般為300 K):

VREF=αVBE+β(ΔVBE)

(1)

這里ΔVBE(也可寫為VTlnn)是分別工作在兩個電流密度下的兩個晶體管的基級-發射極電壓的差值,VBE為晶體管的基級-發射極電壓,α、β為分別對正負溫度系數加的權重。在室溫下?VBE/?VT≈-1.5 mV/°K,?VT/?T≈+0.087 mV/°K(VT=kT/q,k為波耳茲曼常數)。把式(1)對溫度微分,調節α、β的值可以使VREF的溫度系數在T=300 K時為0[1]。

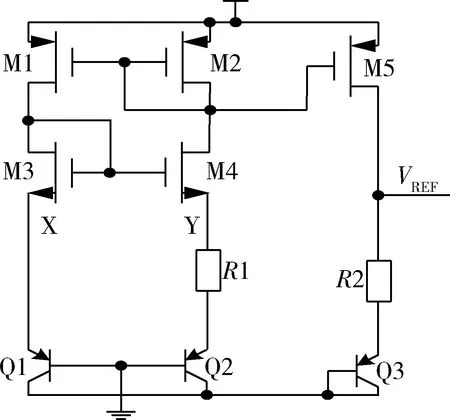

圖1為傳統的帶隙電壓基準源電路[2],M1、M2、M3、M4構成環路,所以流經Q1、Q2的電流相等。M1~M4、Q1、Q2和R1構成PTAT(與絕對溫度成正比)電路,Q2和Q3與Q1發射結面積之比為N,假設電路中MOS的寬長比相同。如果流過M1的電流為I,則M2、M5的電流也為I,VGS3=VGS4,從而VX=VY。所以有:

VEB1=VEB2+IR1

(2)

(3)

(4)

IS2=NIS1

(5)

由式(2)~式(5)可推得:

(6)

所以

(7)

VREF≈VBE3+17.2VT≈1.25 V

(8)

圖1 傳統的帶隙基準源結構

由以上推導可以看出常用的帶隙基準有以下缺點:只是對電路進行了1階的溫度補償;雖然輸出基準電壓會隨著溫度有小幅度的變化,但基本上在1.2 V左右,當電源電壓接近1.2 V時該電壓源就不適用了。為了能得到輸出可控、精度更高的帶隙基準源,本文基于電流模式電路提出一種具有高階曲率補償的、輸出電壓可調的電路結構。

2 帶隙電壓基準源的高階曲率補償

相比于典型的電壓基準源只進行了一階的溫度補償,本文提出的電路還加入了高階曲率補償電路。針對本文采用的電流模式的高階曲率補償方法,可用兩個BJT的電壓差ΔVBE產生的電流來補償。

2.1 三極管的基極-發射極電壓的溫度系數

從文獻[3]中可得到晶體管的基極-發射極電壓為:

(9)

上式中,VBE(T)表示晶體管的基極-發射極電壓隨溫度改變時的值;Vg(T)表示硅的帶隙電壓值,該值由材料本身決定;α與具體采用的工藝有關,表示載流子遷移率與溫度的關系;β表示集電極電流與溫度的相關性,當IC與溫度相關時β=1,與溫度無關時β=0;式(9)中包括常數項、一階項、高階項,典型的帶隙基準源只是對其中的一階項進行了處理,而高階項沒有得到補償,為了減小高階項對基準源的干擾,提出了一種基于電流模式的高階曲率補償電路。

2.2 高階曲率補償帶隙基準源具體電路

總電路由啟動電路、IPTAT電路、電流相加電路和ICTAT(與絕對溫度成反比)電路、INL(兩個晶體管的基極-發射極電壓差ΔVBE產生的電流)模塊組成[4]。圖1中MOS器件的溝道長度調制會導致顯著的電源依賴性。為了避免這個問題,圖1的MOS管全用共源共柵電路代替,為了避免外加偏置的設計,文中采用了自偏置的共源共柵的結構,圖2中R1、R2、R5、R6提供合適的偏置,使所有的MOS管都工作在飽和區。電路中兩個共源共柵電路分別產生IPTAT和ICTAT,并且用兩個晶體管的基極-發射極電壓差ΔVBE產生的電流INL來進行微調,用電流相加模塊把三部分電流進行相加,最后根據Vref=Rref×Iref得到一個與Rref成比例的電壓。

IPTAT模塊由M1~M8、R1、R2、R3、Q1、Q2組成(Q1的發射結面積為Q2的N倍),由此可推得IPTAT為:

(10)

INL模塊由M9、M10、R4、Q3構成,由圖中可得INL為:

(11)

由于VEB2與IPTAT有關,由式(9)可得:

(12)

由于VEB3與ICTAT無關,可得:

(13)

把式(12)、(13)帶入式(11)可得:

(14)

ICTAT模塊由M15~M22、R5、R6、Q4、R7組成(Q1的發射結面積為Q4的N倍),由此可推得ICTAT為:

(15)

以上推得的IPTAT、ICTAT、INL電流經過相加模塊可得輸出電流Iref為:

Iref=IPTAT+ICTAT+INL

(16)

把式(10)、(14)、(15)帶入式(16)可得:

(17)

由上式可以看出此時推得的Iref中包括一階溫度項(式中大括號)、高階溫度項(式中的對數項)以及硅的帶隙電壓(其中包括一階項和高階項)。為了得到與溫度無關的電流,首先要對一階溫度項進行補償,可以調節R3、R7、N的值,使式中的一階項為0。接下來對式中的高階項進行補償,消除式中的對數項。可以發現電阻R7既與一階項有關也與高階項有關,所以一階項的消除和高階項的消除是相互制約的,在調制電路時要多次嘗試,以得到最優化的電路。

根據公式Vref=Iref×Rref,調節Rref的大小就能得到需要的電壓值。

圖2 整體結構

2.3 啟動電路

因為電路啟動時帶隙中電流可能為零,這時帶隙會一直處在關斷狀態,也就是“簡并”點的問題[1]。為了避免“簡并”點的問題,本文引入啟動電路結構,如圖2中S1、S2、S3、R、Q5所示。當電路上電時S1、S2接通并通過S2的漏極給S3的柵極充電,使S3的柵極電位提高,從而使M5、M6、M19、M20導通,各支路都有電流流過,最終達到平衡點。這時S3會導通,從而把S2關斷,S1與S3導通,電流流向Q5,后面的電路工作正常后,啟動電路就不會再起作用[2]。

3 仿真驗證

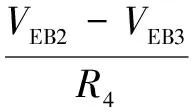

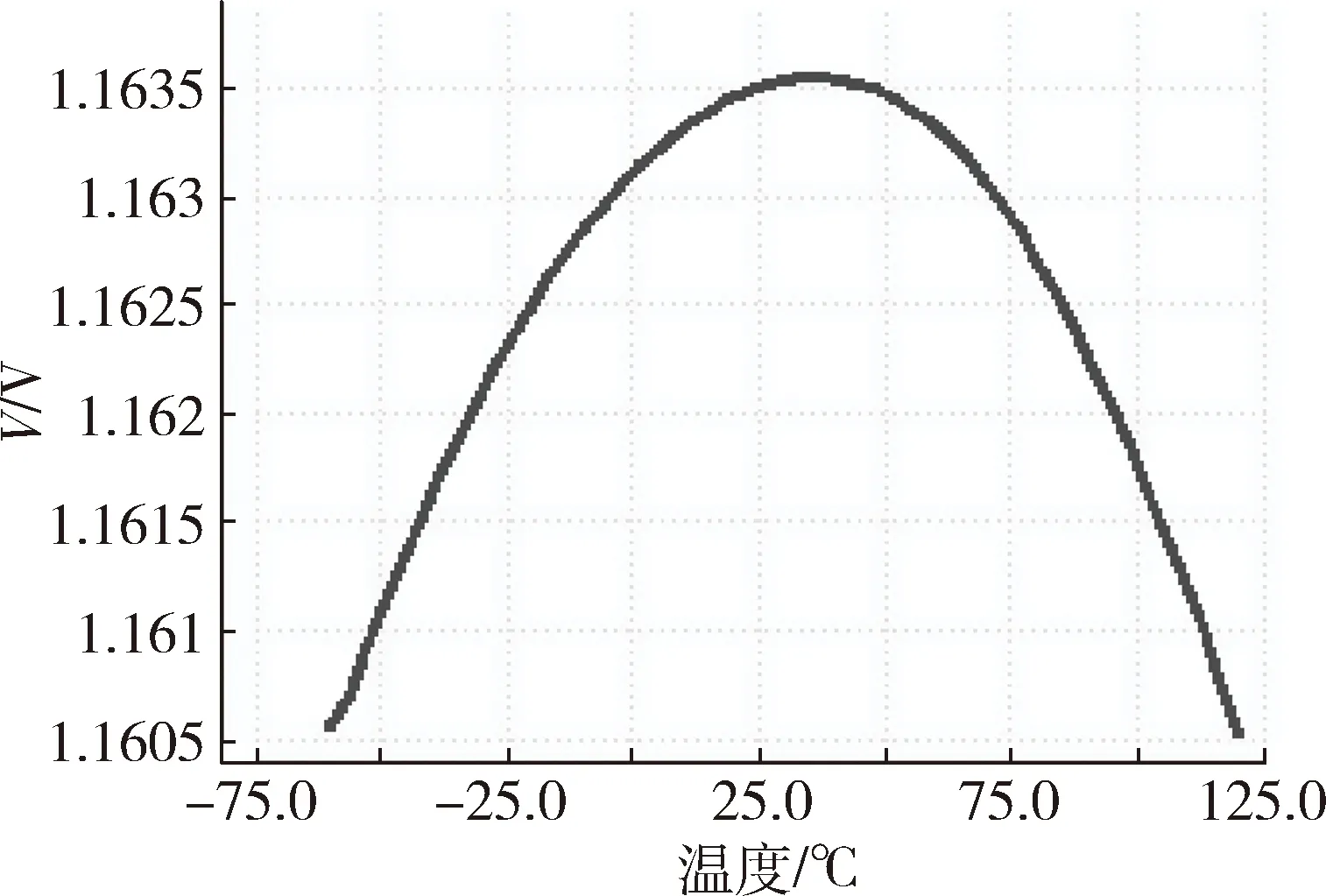

采用Cadence公司的Spectre軟件對整體電路結構進行仿真,采用gpdk090 CMOS 工藝。電源電壓為3.6 V,仿真溫度在-60℃~120℃范圍變化。仿真結果如圖3、圖4所示。

圖3 電壓隨溫度變化的曲線

圖4 電源電壓抑制比

圖3 是對輸出電壓溫度特性的仿真,當溫度在-60℃~120℃范圍時,輸出電壓基本在1.162 V,溫度系數大約為1.44×10-5/℃。圖4是對電源抑制比的仿真,電源提供的電壓為3.6 V,溫度為27℃時,可以得到,該結構有較高的電源抑制比,頻率較低時為-78.3 dB。

表1中列出了本文帶隙基準源的部分參數,并與其他文獻中的帶隙基準源進行了對比,從表中得出,相比于其他文獻中的參數,本文的電路有較好的電源抑制比和溫度系數。

表1 與其他文獻中的帶隙基準源比較

4 結論

文中設計了一種電流模式的帶隙電壓基準源電路結構,通過把3個溫度系數不相同的電流相加得到與溫度關系很小的電壓。為了使電路有更好的性能,電路采用了高階曲率補償方法。從仿真結果可以看出,當電源提供的電壓為3.6 V,溫度在-60~120℃范圍時,溫度系數為1.44×10-5/℃,電源抑制比為-78.3 dB。相比于其他文獻中的帶隙電壓基準源有更好的性能。

[1] RAZAVI B.模擬CMOS集成電路設計[M].陳貴燦,譯.西安:西安交通大學出版社,2003.

[2] 周永峰,戴慶元,林剛磊,等. 一種用于CMOS A/D轉換器的帶隙基準電壓源[J]. 微電子學,2009,39(1):25-28,33.

[3] 李斌橋,許延華,徐江濤,等. 高階曲率補償電流模式的CMOS帶隙基準源[J]. 天津大學學報(自然科學與工程技術版),2008,41(12):1459-1464.

[4] 胡勇,彭曉宏,劉云康,等. 一種新型電流模式帶隙基準源的設計[J]. 微電子學,2013,43(4):457-459,463.

[5] 梁愛梅,凌朝東. 電流鏡型二次曲率補償的帶隙基準源設計[J]. 華僑大學學報(自然科學版),2010,31(3):267-271.

[6] Zhao Chenyuan,Huang Junkai. A new high performance bandgap reference[C]. 2011 International Conference on Electronics,Communications,and Control(ICECC),2011:64-66.

[7] 陳友福,李平,劉銀,等. 一種新型的BiCMOS帶隙基準電壓源[J]. 微電子學,2006,36(3):381-384.

High-order curvature-compensated CMOS of current mode

Zhang Pujie1,Wang Weidong2,Li Yaozhen3

(School of Information and Communication Engineering,Guilin University of Electronic Technology,Guilin 541004,China)

The traditional bandgap voltage reference source is only the first-order temperature compensated ,and the output voltage reference is only at about 1.2 V. in order to get an adjustable and higher precision voltage reference,a current-mode bandgap voltage reference source was presented in this paper. Circuit adopted high-order curvature compensation methods,and the output of the reference voltage can be adjusted according to the size of the output resistance.It was fabricated in gpdk090 CMOS process.By simulation with Spectre,supplying voltage of 3.6 V,a temperature coefficient of 14.4×10-6/℃ in the temperature range of -60℃ to 120℃,the power supply rejection ratio is 78.3 dB,and the averaged reference voltage is 1.162 V.

bandgap voltage reference; high-order curvature compensation; temperature coefficient; PSRR

TN432

A

10.19358/j.issn.1674-7720.2017.24.005

張普杰,王衛東,李耀臻.電流模式的高階曲率補償CMOS帶隙基準源J.微型機與應用,2017,36(24):16-18,21.

2017-06-24)

張普杰(1991-)男,碩士研究生,主要研究方向:模擬集成電路設計。

王衛東(1956-)男,教授,碩士生導師,主要研究方向:模擬集成電路與電流模式電路。

李耀臻(1989-),男,碩士研究生,主要研究方向:模擬集成電路設計。