基于FPGA的模/數混合采集系統優化設計

楊圣龍+任勇峰+李輝景

摘 要: 針對彈上環境采集空間環境模擬量和圖像數字量的需求,設計一種以FPGA為核心的模/數混合采集系統。該系統對模擬量采集的運放不穩定性進行分析與優化,提高運放補償電路的穩定性。在FPGA內通過模/數混合編幀,提高數據存儲效率。同時針對圖像信號壓縮數據的速率變化導致數據的產生速率與傳輸速率不匹配問題,提出動態平衡編幀的方法解決了速率匹配問題。經實際飛行測試,該采集系統數據輸出可靠,可滿足系統的各項性能指標。

關鍵詞: 數據采集; 運放補償; 均勻采樣; 模/數混合編幀; FPGA; 動態平衡編幀

中圖分類號: TN79+2?34; TP274 文獻標識碼: A 文章編號: 1004?373X(2018)06?0117?04

Abstract: In allusion to the acquisition requirement of space environment analog quantity and image digital quantity on the missile environment, a analog?digital hybrid acquisition system based on FPGA is designed. In the system, the operational amplifier instability of analog quantity acquisition is analyzed and optimized to increase operational amplifier compensation circuits and improve stability. In FPGA, analog?digital hybrid framing is adopted to improve data storage efficiency. Meanwhile, in allusion to the mismatching problem of data generation speed and transmission speed caused by speed variation of packed image signal data, the dynamic balanced framing method is proposed to solve the speed matching problem. The actual flight test demonstrates that the acquisition system has reliable data output, and can meet various system performance indexes.

Keywords: data acquisition; operational amplifier compensation; uniform sampling; analog?digital hybrid framing;

FPGA; dynamic balanced framing

隨著近現代新型武器裝備和航天設備的研發,飛行器不僅要采集飛行過程中的空間環境參數,還需將更加直觀的圖像數據進行回傳,這對采集系統提出了新的要求[1]。為滿足數據采集存儲可靠指標,本文設計以FPGA為核心的采集系統,對采集的模擬信號進行調理優化,圖像數字量信號采用動態平衡編幀技術,解決了壓縮速率與傳輸速率匹配問題,將多路模擬信號與數字信號進行混合編幀存儲。數據還可通過USB串口傳至上位機進行監測,提高了數據的可靠性。

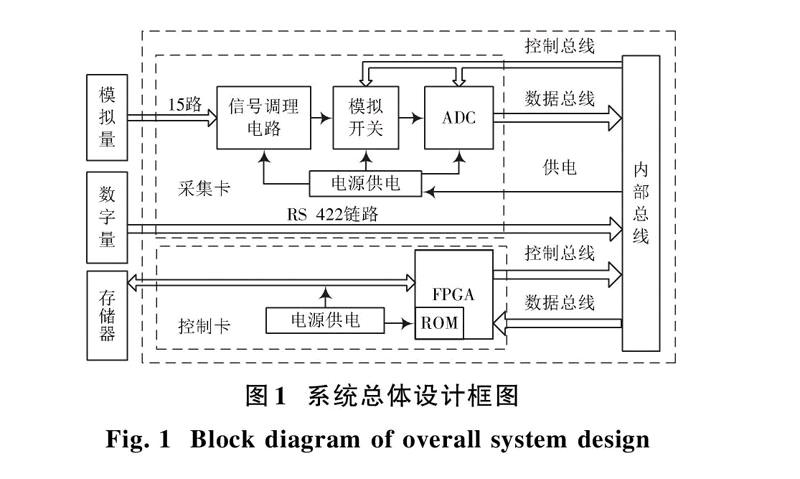

1 系統總體設計

本采集系統主要由以下四部分組成:A/D信號調理模塊、ADC轉換模塊、數字量采集模塊、FPGA模/數信號混合編幀模塊。A/D信號調理模塊負責采集模擬信號,進行濾波調理分壓后送至ADC轉換模塊;ADC轉換模塊將模擬信號轉化為數字量輸出至FPGA[2];數字量采集模塊為兩路圖像數據,通過兩路RS 422鏈路將數據送至FGPA后與模擬信號進行打包并存儲。由于不同的模擬量的采樣率不同,因此需要對各路信號進行混合編幀后實現平均采樣達到數據同步傳輸。系統設計如圖1所示。

2 硬件電路優化設計

為了減弱原始信號中積累的干擾和噪聲信號,提高輸入信號抗干擾能力,需要對模擬量信號進行濾波調理[3]。再經過分壓跟隨后使信號滿足后級模/數轉換器ADC的輸入指標要求,以此來提高信號采集精度和靈敏度。

在運放使用時,一般會增加一個負反饋電路起到穩定運放的增益、增加頻帶、提高保真度的作用,如圖2所示,但是負反饋電路的引入會使得運放電路不穩定[4]。此外,由于模擬開關 ADG706引腳間存在200 pF的分布電容[5],運放在驅動容性負載會在反饋回路上產生額外延遲,導致環路相移滯后。當相移滯后大于135°時,就會導致發生頻響尖峰甚至振蕩[6]。

圖3為某電路中運放輸出不穩定,導致的振蕩現象。通過在傳輸線上串聯電阻Rx來對運放進行環路補償,即可將運放和容性負載電路隔離,從而對信號的振鈴或震蕩起到抑制作用[7],但這種方法僅適用于容性負載小于1 500 pF的電路,經實驗測試,串聯電阻Rx一般取值為5~100 Ω。優化后的階躍響應見圖4。

3 數據編幀邏輯和實現

3.1 不同類型數據混合編幀

本數據采集系統主要采集15路采樣率不同的模擬量、兩路開關量和兩路圖像數據并進行存儲。傳統方法是將各種不同類型的數據進行分區間存儲,回收時再從對應的存儲塊區間進行回讀[8]。這種方法需要對不同的數據類型分配不同的FIFO進行緩存,當數據類型較多時,造成FIFO資源緊缺。而且在邏輯控制方面,FPGA不僅需要進行FIFO切換,還得控制不同的存儲區間,從對應的FIFO中取數進行存儲[9],導致存儲空間也需不斷進行跳變,使得FPGA邏輯處理復雜化,降低了系統的可靠性。圖5為不同類型數據分區間存儲示意圖。endprint

本系統設計在數據采集時將不同類型的數據進行混合存儲,在數據存儲時對不同數據類型加入幀結構,即編幀存儲。數據回收時,只需要按照幀結構對數據進行解包還原,即可得到原始數據。這種混合編幀的方法簡化了FPGA處理流程,大大節省了FPGA資源,并且提高了系統的可靠性,如圖6所示。

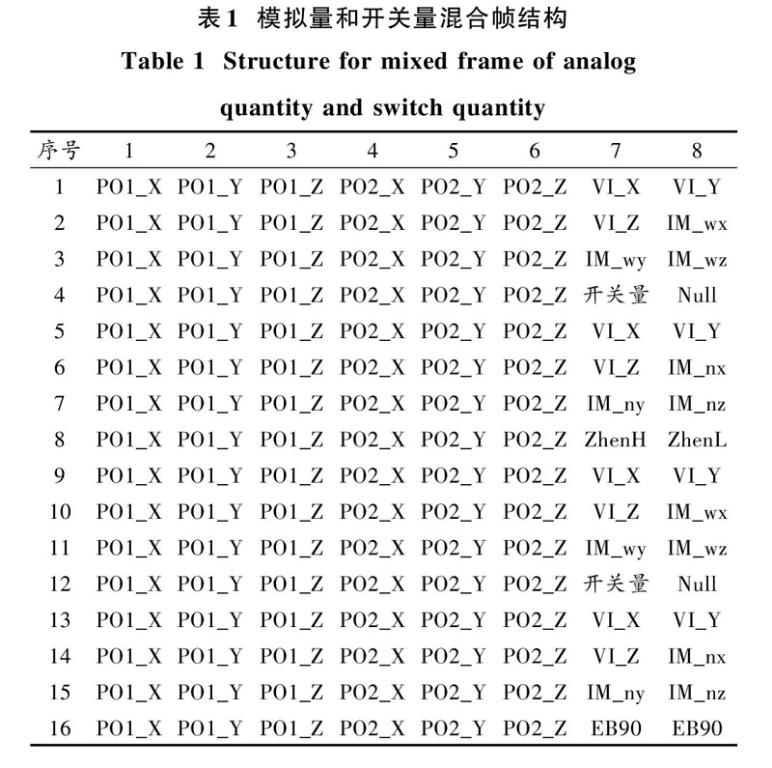

3.2 均勻采樣實現方法

根據奈奎斯特定律,采樣頻率[10]應為信號頻率的2倍。在實際工程應用中,一般為信號頻率的4倍以上;另外為保證均勻采樣,多次出現的通道應該盡量平均穿插分布在一整幀中,且各通道采樣率值均為最小采樣率的整數倍[11]。由于本采集系統中模擬量和開關量總采樣率為305 kHz,A/D按照320 kHz的采樣率進行采樣,因此在編幀時需要填補空采點。將幀結構寫入ROM表中,通過讀取ROM即可進行通道選擇。為了數據提取和校驗,在幀結構中添加幀標志(EB 90)和幀計數(ZhenH,ZhenL),Null為空采點。設計的模擬量和開關量的幀結構如表1所示。

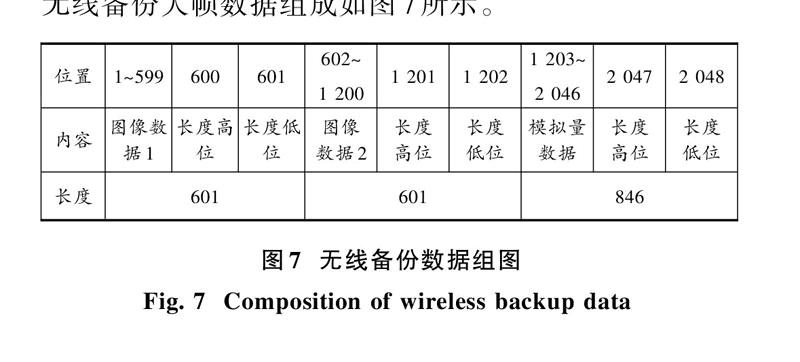

3.3 動態平衡數據編幀方法

根據系統設計要求,部分模擬量和兩路圖像數據需進行無線備份,數據以4 Mbit/s的固定速率傳給無線設備。為了區分不同的數據類型,每包數據可采用不同的幀標志和幀計數來進行編幀,本設計中無線備份數據一幀長度為2 048 B。無線備份數據每包加上幀標志和幀計數后實際產生的數據量為3 980 kbit/s,但與4 Mbit/s的帶寬傳輸速率仍不匹配。另外由于圖像壓縮數據的速率在不斷變化,因此產生的數據速率也在不斷變化。為了以固定速率進行傳輸,必須對數據幀填充無效數[12]。經過分析驗證,可以通過對不同速率的數據按照速率比進行帶寬分配,各類型數據在每一幀數據包中占用固定幀長,數據不夠時則填充無效數“00”,然后在各類型數據包后加入有效數長度值,數據解包時直接提取各包中的有效數據,這樣可以實現數據的可靠傳輸[13]。無線備份大幀數據組成如圖7所示。

其中圖像1數據包在一大幀數據中占601 B,從第1 B到第599 B為圖像數據1的數據內容,第600 B及第601 B存放本包圖像數據1的有效數據長度,其最大長度為599 B,實際長度≤599 B。圖像數據包見圖8。

當Lcount=599時,有效數據長度為599 B;當Lcount<599時,有效數據長度為Lcount字節,無效數據長度為599-Lcount,無效數據填充字節固定為“00”,存放在數據包末尾。圖像2數據包存放位置在圖像1之后,其數據組成結構與圖像1完全相同。模擬量數據包與圖像數據結構類似,數據包存放位置在圖像數據2之后,在一大幀數據中占846 B,數據包結構組成如圖9所示。

當Lcount=844時,有效數據長度為844 B;當Lcount<844時,有效數據長度為Lcount字節,無效數據長度為844-Lcount,無效數據填充字節固定為“00”,無效數據存放在數據包末尾。此方法按速率比分配各數據包的長度[14],在每幀數據中模擬量和兩路圖像數據所占長度固定,但傳輸的有效數據長度并不固定,當未寫滿固定長度時,就用無效數據“00”進行填補,每個數據包后加入有效數據的長度計數,這樣在圖像壓縮數據速率不斷發生變化時,就可實現無線備份數據動態平衡傳輸。

4 數據回收及其驗證

通過對存儲器回收讀數后部分數據如圖10所示,其中幀標x3333表示有效數據類型為模擬量和開關量,x6666,x9999分別為兩路圖像數據的數據幀標志。

通過觀察混合數據的幀頭是否對齊、幀計數是否連續來判斷數據回讀是否正常。圖11為驗證模擬量數據和開關量的編幀格式(空采點為開關量數據),易知此編幀方式能實現數據的均勻采樣,且數據準確無丟數誤碼現象。

對于無線備份數據測試,數據采用動態平衡編幀,每個數據包長度固定,圖12中灰色區域為填充的無效數“00”,包尾為有效數據的長度計數。

系統在經過高低溫和振動等試驗的重復測試后,通過上位機進行數據分析,未發現數據出現任何異常,滿足數據完整及可靠性設計指標要求[15]。

5 結 語

本文首先對采集接口電路增加了運放補償電路,分析了傳統模/數混合存儲的弊端后,提出新的混合存儲方法,并采用動態平衡的編幀方式解決了傳輸速率匹配的問題。經過各種實驗測試后,該系統采用的編幀方法數據可靠性得到了保障,對一些需要模/數混合編幀的采集系統有一定的參考意義。

參考文獻

[1] 彭巧君.彈上多類型混合信號測量的研究與設計[D].太原:中北大學,2015.

PENG Qiaojun. Research and design of multi?type mixed signal measurement on projectile [D]. Taiyuan: North University of China, 2015.

[2] 任勇峰,張凱華,程海亮.基于FPGA的高速數據采集存儲系統設計[J].電子器件,2015,38(1):135?139.

REN Yongfeng, ZHANG Kaihua, CHENG Hailiang. Design of high?speed acquisition and storage system based on FPGA [J]. Chinese journal of electron devices, 2015, 38(1): 135?139.

[3] MENG Xiangjiao, ZHANG Huixin, LI Xianghong. The design of a multi?channel data acquisition module based on FPGA [J]. Advanced materials research, 2012, 433/440: 6589?6593.endprint

[4] 何崢嶸.運算放大器電路的噪聲分析和設計[J].微電子學,2006,36(2):148?153.

HE Zhengrong. Noise analysis and design of operational amplifier circuits [J]. Microelectronics, 2006, 36(2): 148?153.

[5] 何亞杰.一種模擬濾波電路數字化方法[J].電子科技,2014,27(3):63?65.

HE Yajie. A method for digitizing analog filters [J]. Electronic science & technology, 2014, 27(3): 63?65.

[6] 武曉棟,鄭賓,崔婧,等.基于FPGA的混合編幀的高速采集系統[J].伺服控制,2014(2):51?53.

WU Xiaodong, ZHENG Bin, CUI Jing, et al. High speed data acquisition system for mixed frame based on FPGA [J]. Servo control, 2014(2): 51?53.

[7] 尹鵬亮,張永瑞,崔永俊,等.混合數據采集與存儲的實現[J].計算機測量與控制,2014(10):3297?3300.

YIN Pengliang, ZHANG Yongrui, CUI Yongjun, et al. Implementation of mixed data acquisition and storage [J]. Computer measurement & control, 2014(10): 3297?3300.

[8] 崔婧,沈三民,葉勇.基于FPGA的模數混合編幀的采集系統[J].科學技術與工程,2013,13(1):75?79.

CUI Jing, SHEN Sanmin, YE Yong. Data collection system based on FPGA based modulus hybrid frame [J]. Science technology and engineering, 2013, 13(1): 75?79.

[9] 侯明波,黃偉志,郝巖.多通道數據采集分析系統[J].儀表技術與傳感器,2013(10):47?49.

HOU Mingbo, HUANG Weizhi, HAO Yan. Design of multichannel data acquisition and analysis system [J]. Instrument technique and sensor, 2013(10): 47?49.

[10] 張小琴.基于FPGA的高速圖像數據采集系統設計[D].武漢:武漢理工大學,2010.

ZHANG Xiaoqin. Design of high speed image data acquisition system based on FPGA [D]. Wuhan: Wuhan University of Technology, 2010.

[11] 宋中喆,裴東興,楊少博.基于USB 3.0接口的高速數據傳輸系統設計[J].現代電子技術,2017,40(4):159?162.

SONG Zhongzhe, PEI Dongxing, YANG Shaobo. Design of high?speed data transmission system based on USB 3.0 interface [J]. Modern electronics technique, 2017, 40(4): 159?162.

[12] 麻志濱,廖雯,劉芳.基于FPGA的高速數據采集分析系統的設計[J].現代電子技術,2014,37(16):135?137.

MA Zhibin, LIAO Wen, LIU Fang. Design of high speed data acquisition and analysis system based on FPGA [J]. Modern electronics technique, 2014, 37(16): 135?137.

[13] 張志偉.模/數混合信號集成電路自動設計技術研究[J].陜西理工學院學報(自然科學版),2013,29(4):25?29.

ZHANG Zhiwei. Research of mixed?signal IC automatic design technology [J]. Journal of Shaanxi University of Technology (Natural science edition), 2013, 29(4): 25?29.

[14] 劉懌恒.基于FPGA的數據采集與處理系統設計[D].長沙:湖南大學,2013.

LIU Yiheng. Design of data acquisition and processing system based on FPGA [D]. Changsha: Hunan University, 2013.

[15] 葉勇.多參數數據采集裝置設計與實現[D].太原:中北大學,2013.

YE Yong. Design and implementation of multi?parameter data acquisition device [D]. Taiyuan: North University of China, 2013.endprint