過程考核在EDA技術(shù)課程考核中的實(shí)踐與探索

楊振南 梁曉琳

摘要:EDA技術(shù)是一門專業(yè)技能課,以培養(yǎng)學(xué)生應(yīng)用硬件描述語言進(jìn)行FPGA開發(fā)的能力為目標(biāo)。為實(shí)現(xiàn)這個(gè)教學(xué)目標(biāo),提出把教學(xué)分成軟件操作教學(xué)、VerilogHDL語法教學(xué)、基本數(shù)字模塊教學(xué)和綜合項(xiàng)目訓(xùn)練4個(gè)教學(xué)階段,并且在每個(gè)階段教學(xué)結(jié)束時(shí)進(jìn)行階段考試,把4個(gè)階段的考試成績加權(quán)求和作為學(xué)生的課程考核成績,同時(shí)創(chuàng)新地使用階段重修補(bǔ)考的方法督促學(xué)生全過程認(rèn)真學(xué)習(xí)。

關(guān)鍵詞:EDA技術(shù);分階段教學(xué);過程考核

1引言

EDA技術(shù)課程作為一門實(shí)用性很強(qiáng)的實(shí)踐技術(shù)課,在電子信息、通信、自動(dòng)控制及計(jì)算機(jī)應(yīng)用領(lǐng)域的重要性日益突出,在電子類專業(yè)廣泛開設(shè)。該課程開設(shè)的目的是使學(xué)生掌握采用硬件描述語言,借助EDA工具進(jìn)行電子電路設(shè)計(jì)的方法,培養(yǎng)學(xué)生使用可編程邏輯器件進(jìn)行數(shù)字系統(tǒng)設(shè)計(jì)以解決實(shí)際工程問題的能力。為了達(dá)成這個(gè)目標(biāo),學(xué)生需要具備以下四個(gè)方面的能力:掌握一種EDA開發(fā)軟件平臺(tái);掌握一門硬件描述語言;掌握基本數(shù)字電路模塊的原理及設(shè)計(jì)方法;具有設(shè)計(jì)一定復(fù)雜程度數(shù)字系統(tǒng)的能力。這四個(gè)能力具有層層遞進(jìn),前后依賴的關(guān)系。在教學(xué)中需要依照培養(yǎng)目標(biāo)分階段開展教學(xué)。為了及時(shí)地了解學(xué)生的學(xué)習(xí)效果,督促學(xué)生掌握好各階段的知識(shí)和技能,為后續(xù)階段的學(xué)習(xí)打下基礎(chǔ),就需要在每個(gè)階段結(jié)束后,對(duì)學(xué)生的學(xué)習(xí)進(jìn)行考核。鑒于此,筆者對(duì)EDA技術(shù)課程進(jìn)行了改革,采用分階段教學(xué)與過程考核相結(jié)合的方法。具體實(shí)施辦法如下所述。

2分階段教學(xué)方法

根據(jù)EDA技術(shù)教學(xué)需要達(dá)成的四個(gè)目標(biāo),把教學(xué)分成以下四個(gè)階段。

2.1QuartuslI軟件操作的教學(xué)

筆者所在學(xué)校的實(shí)驗(yàn)箱使用的是Ahera公司的FPGA芯片,所以選擇該公司的QuartuslI軟件作為EDA開發(fā)平臺(tái)。此階段的教學(xué)目標(biāo)是讓學(xué)生掌握QuartuslI軟件的基本操作,了解FPGA芯片開發(fā)的基本流程,掌握實(shí)驗(yàn)箱的結(jié)構(gòu)和使用,理解FPGA芯片與普通數(shù)字邏輯芯片的差異。教學(xué)內(nèi)容包括:Qua-tuslI創(chuàng)建工程,新建各類設(shè)計(jì)文件,繪制電路圖的基本操作,全程編譯,創(chuàng)建仿真文件,仿真激勵(lì)設(shè)置,仿真結(jié)果閱讀,鎖定引腳,實(shí)驗(yàn)箱原理及使用等。教學(xué)方法:在機(jī)房進(jìn)行教學(xué),老師邊講邊演示,學(xué)生邊聽邊操作。每次課結(jié)束前,對(duì)所講的內(nèi)容進(jìn)行總結(jié),如果有涉及理論教學(xué),則穿插在演示過程中講解。教學(xué)中使用數(shù)字電路基礎(chǔ)課程中學(xué)習(xí)過的器件作為教學(xué)和練習(xí)對(duì)象,例如簡單與非邏輯電路,加法器,選擇器,觸發(fā)器等的內(nèi)部結(jié)構(gòu)圖。

2.2 Verilog HDL語法教學(xué)

硬件描述語言應(yīng)用最廣泛的有VHDL和Verilog HDL兩種,后者與C語言語法類似,容易學(xué)習(xí),所以筆者選擇后者用來教學(xué)。此階段的教學(xué)目標(biāo)是讓學(xué)生掌握Ve~ogHDL語言的基本語法。教學(xué)內(nèi)容包括:Verilog HDL程序的基本框架,always語句,assign語句,case語句,if語句和運(yùn)算符等。教學(xué)方法:在機(jī)房進(jìn)行,先練后講;以數(shù)據(jù)選擇器為對(duì)象討論組合電路的設(shè)計(jì)方法;分別使用不同的語句進(jìn)行設(shè)計(jì),從實(shí)例講解和練習(xí)出發(fā),再小結(jié)使用到語句的語法;以寄存器,計(jì)數(shù)器為對(duì)象,講解簡單時(shí)序電路的設(shè)計(jì)方法。每一個(gè)實(shí)例都要求學(xué)生在課堂上完成仿真驗(yàn)證,操作熟練的同學(xué)則要求完成實(shí)驗(yàn)箱上的驗(yàn)證,并且布置課后練習(xí),要求學(xué)生在自己的電腦上進(jìn)一步熟練軟件操作,學(xué)習(xí)語法規(guī)則。

2.3基本數(shù)字模塊設(shè)計(jì)教學(xué)

此階段的教學(xué)目標(biāo)是:讓學(xué)生根據(jù)設(shè)計(jì)任務(wù),利用學(xué)習(xí)過的Verilog HDL語句,自己進(jìn)行數(shù)字模塊的設(shè)計(jì)。教學(xué)內(nèi)容包括:數(shù)碼管譯碼器,多位多選一數(shù)據(jù)選擇器,BCD編碼器,分頻器,BCD碼計(jì)數(shù)器等。教學(xué)方法:老師講解設(shè)計(jì)目標(biāo),進(jìn)行設(shè)計(jì)任務(wù)分解,設(shè)計(jì)原理分析,然后學(xué)生進(jìn)行代碼編寫和設(shè)計(jì)驗(yàn)證;為了降低設(shè)計(jì)難度,逐步培養(yǎng)學(xué)生的設(shè)計(jì)能力,可以采用關(guān)鍵代碼行填空,代碼段填空,直到完全獨(dú)立編寫的方法。每次課,都需要留出時(shí)間給學(xué)生講解答案,分析代碼,并要求每個(gè)學(xué)生最終完成設(shè)計(jì)。

2.4綜合訓(xùn)練項(xiàng)目教學(xué)

教學(xué)目標(biāo):培養(yǎng)學(xué)生使用自上而下的方法進(jìn)行數(shù)字系統(tǒng)設(shè)計(jì)的能力。教學(xué)內(nèi)容:計(jì)數(shù)器與數(shù)碼管譯碼器綜合設(shè)計(jì),數(shù)碼管掃描器的設(shè)計(jì),頻率計(jì)的設(shè)計(jì),電子時(shí)鐘的設(shè)計(jì),ADC轉(zhuǎn)換器讀寫時(shí)序設(shè)計(jì),串行通信接口模塊的設(shè)計(jì)等,具體教學(xué)內(nèi)容可以依據(jù)實(shí)際教學(xué)課時(shí)和教學(xué)進(jìn)度進(jìn)行適當(dāng)增減。教學(xué)方法:老師講解設(shè)計(jì)目標(biāo),把設(shè)計(jì)分解成不同的內(nèi)部模塊,并畫出方框圖,講解各個(gè)內(nèi)部模塊之間的信號(hào)連接。然后,要求學(xué)生進(jìn)行代碼的設(shè)計(jì)。為了降低設(shè)計(jì)難度,對(duì)于部分核心代碼可以給出參考代碼,或者給出參考資料和參考教材,讓學(xué)生自學(xué)。此階段難度較大,因此,教學(xué)需要擴(kuò)展到課后。筆者教學(xué)中,采用了這次課布置任務(wù),講解設(shè)計(jì)原理,下次課檢查學(xué)生的設(shè)計(jì)結(jié)果的方法。這樣學(xué)生就可以利用兩次課中間的空余時(shí)間完成練習(xí)。老師在檢查完結(jié)果后,公布參考代碼,并且演示,然后學(xué)生根據(jù)參考代碼,查漏補(bǔ)缺。

3過程考核

3.1過程考核總體概述

分階段教學(xué)的模式,從第二個(gè)階段開始,每個(gè)階段都使用到上一個(gè)階段的知識(shí)和技能,同時(shí)又是下一個(gè)階段學(xué)習(xí)的基礎(chǔ),所以學(xué)生在每個(gè)階段的學(xué)習(xí)都非常重要。地方性本科院校的學(xué)生,其學(xué)習(xí)主動(dòng)性和自覺性較差,僅就教學(xué)進(jìn)行改革,則大部分學(xué)生都無法達(dá)成教學(xué)目標(biāo)。通過課程考核是學(xué)生獲得學(xué)位的必要條件,因此充分利用考核督促學(xué)生學(xué)習(xí)是一個(gè)很有效的方法。在傳統(tǒng)的教學(xué)中,使用期末考試進(jìn)行一次性考核。從以往的經(jīng)驗(yàn)看,學(xué)生常依靠前突擊應(yīng)對(duì)考試,不利于督促學(xué)生平時(shí)的學(xué)習(xí)。尤其本課程的階段依賴性決定期末考試的方式不適合用來進(jìn)行本課程的考核。

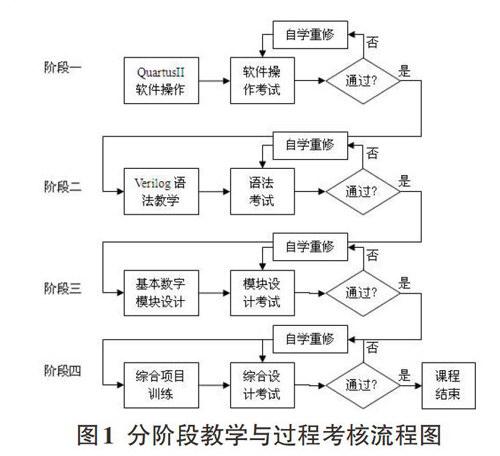

因此,筆者在每個(gè)階段教學(xué)結(jié)束后都進(jìn)行考試,四個(gè)階段共有四次考試,這四次考試分散在整個(gè)學(xué)期的不同時(shí)間進(jìn)行,是對(duì)學(xué)生學(xué)習(xí)過程的深入考核,簡稱為過程考核。又由于學(xué)生個(gè)體差異,階段考試也會(huì)出現(xiàn)不及格的現(xiàn)象。不及格意味著該生這個(gè)階段學(xué)習(xí)離目標(biāo)太遠(yuǎn),不能直接開展后續(xù)階段的學(xué)習(xí),因此學(xué)生需要通過自學(xué),重修這個(gè)階段的內(nèi)容,然后參加補(bǔ)考,補(bǔ)考通過才能進(jìn)行下一個(gè)階段的學(xué)習(xí)。教學(xué)和考核的進(jìn)行過程如圖1所示。

3.2各個(gè)階段考試內(nèi)容及考試方法

3.2.1軟件操作考試

考試要求:此階段主要考試學(xué)生對(duì)于QuartuslI軟件操作的掌握程度。要求學(xué)生在不翻閱教材、實(shí)驗(yàn)指導(dǎo)書的前提下,能夠順利完成工程創(chuàng)建,電路圖繪制(電路圖通過試卷提供),全程編譯,仿真驗(yàn)證,和實(shí)驗(yàn)箱驗(yàn)證。考試內(nèi)容和形式:考試在機(jī)房進(jìn)行,一人一機(jī),考試時(shí)間為一個(gè)小時(shí);考試內(nèi)容為教學(xué)過程中講解過的示例和練習(xí)過的數(shù)字電路基礎(chǔ)模塊內(nèi)部結(jié)構(gòu)圖,教師選取4-5個(gè)圖寫在一張?jiān)嚲砩献鳛轭}目,學(xué)生隨機(jī)抽取一個(gè)題目進(jìn)行現(xiàn)場(chǎng)考試。考試成績的評(píng)定:老師在學(xué)生每完成一個(gè)步驟后進(jìn)行檢查,根據(jù)學(xué)生完成的速度和質(zhì)量給出該步驟得分,最后加總所有步驟得分計(jì)算出總分。

3.2.2 VerilogHDL語法考試

考試要求:要求學(xué)生掌握VerilogHDL的基本語法,正確的編寫VerilogHDL語句,能夠發(fā)現(xiàn)和改正語法錯(cuò)誤,正確使用運(yùn)算符。考試內(nèi)容及形式:考試使用傳統(tǒng)的閉卷考試的方式,在教室進(jìn)行,學(xué)生間隔坐好,老師監(jiān)考,考試時(shí)間為一個(gè)小時(shí)。試卷內(nèi)容由老師靈活設(shè)置,只要完成考試要求即可。試題類型可以為填空題,選擇題或者是改錯(cuò)題等,但是不建議設(shè)置編程題。考試成績的評(píng)定:考試結(jié)束后,教師改卷給出成績。

3.2.3基本數(shù)字模塊考試

考試要求:此階段要求學(xué)生掌握基本數(shù)字電路模塊的作用及原理,具備運(yùn)用VefilogHDL語言設(shè)計(jì)基本數(shù)字模塊的能力。考試內(nèi)容及形式:考試在實(shí)驗(yàn)室進(jìn)行,每人一臺(tái)電腦一個(gè)實(shí)驗(yàn)箱,考試時(shí)間一個(gè)小時(shí);老師從本階段教學(xué)中講解過的數(shù)字模塊抽取4-5個(gè)制成試卷,學(xué)生隨機(jī)抽取一道題,現(xiàn)場(chǎng)編程設(shè)計(jì),仿真驗(yàn)證,并且使用實(shí)驗(yàn)箱驗(yàn)證,每完成一步,老師當(dāng)場(chǎng)檢查,根據(jù)完成情況給出該步驟得分。考試成績?cè)u(píng)定:考試結(jié)束后,老師收集學(xué)生試卷,根據(jù)學(xué)生每個(gè)步驟得分統(tǒng)計(jì)出此階段考試的總分。