高性能多標準可配置Viterbi譯碼器設計與驗證

戴瀾 馬東俊

摘 ?要: 為了使Viterbi譯碼器廣泛地應用于更多標準中,結合前向回溯譯碼和滑窗流水技術,同時ACS(Add?Compare?Select)部件通過減規約的操作減少異或延遲,提出一種高性能可配置Viterbi譯碼器。該譯碼器支持[12,13,14]碼率,約束長度在5~9之間,生成多項式任意配置等參數,同時支持GPRS,WiMAX,IS?95 CDMA,LTE,CDMA 2000等多標準。在對譯碼器進行設計的基礎上,基于UVM 驗證方法學搭建一種模塊級驗證平臺,完成Viterbi譯碼器模塊級的功能驗證,覆蓋率達到99.4%。利用Synopsys Design Compiler工具進行綜合,面積為0.2 mm2;在28 nm工藝,500 MHz主頻下,功耗為38.3 mW,吞吐率為1.06 Gbit/s。結果表明,此譯碼器具有很好的靈活可配性,在移動終端有很好的應用前景。

關鍵詞: Viterbi譯碼器; 滑窗流水技術; 多項式任意配置; UVM 驗證方法學 ; 異或延遲; 移動終端

中圖分類號: TN919.3?34 ? ? ? ? ? ? ? ? ? ?文獻標識碼: A ? ? ? ? ? ? ? ? ? ? ? ? 文章編號: 1004?373X(2018)10?0010?05

Abstract: To make the Viterbi decoder widely applied in more standards, a high?performance configurable Viterbi decoder is proposed by combining with pre?traceback (PTB) decoding and sliding?window pipeline technology, and reducing the XOR delay by means of the specification subtraction operation in Add?Compare?Select (ACS) components. The decoder can support the code rates of 1/2, 1/3 and 1/4, constraint length of 5 to 9, polynomial generation arbitrary configuration and other parameters, and meanwhile can support multiple standards such as GPRS, WiMAX, IS?95 CDMA, LTE, and CDMA2000. On the basis of the decoder design, a module?level verification platform is established based on the UVM verification methodology to accomplish module?level functional verification for the Viterbi decoder with the code coverage rate as high as 99.4%. The Synopsys Design Compiler tool is used to perform integration, and the area is 0.2 mm2. In the 28 nm process with the main frequency of 500 MHz, the power consumption is 38.3 mW and the throughput rate is 1.06 Gbit/s. The results show that the decoder has good flexibility and compatibility, and has a good prospect in mobile terminal application.

Keywords: Viterbi decoder; sliding?window pipeline technology; polynomial arbitrary configuration; UVM verification methodology; XOR delay; mobile terminal

維特比譯碼器在現代通信、信息儲存中都有廣泛的應用。為了配合多樣化的通信標準,設計一個能夠適應多種標準的、高性能的維特比譯碼器,具有十分重要的意義。

一般Viterbi譯碼器大多是支持單一標準的[1?3],本文中基于前向回溯和流水技術[4?5],采用基四算法,提出一種支持多標準、可配置的譯碼器。表1列出了不同通信標準下,多標準Viterbi譯碼器需要支持的碼率、約束長度、狀態數參數。從表中可以看到大部分通信標準的碼率都在[12,13,14]間變化,約束長度在5~9間變化。

如何高效地驗證Viterbi譯碼器是目前亟待解決的問題。文獻[6]采用VMM(Verification Methodology Manual)驗證方法學搭建MAC(Media Access Control)模塊的驗證平臺,缺點是VMM最初不開源,使用不方便;文獻[7]采用OVM(Open Verification Methodology)驗證方法學設計了一個關于SoC(System on Chip)系統的驗證平臺。OVM雖然是開源的,但是沒有引進寄存器解決方案,這是很大一個短板。而UVM(Universal Verification Methodology)驗證方法學繼承了OVM和VMM的優點,同時又結合System Verilog(SV)驗證語言的隨機約束特性,針對可配置譯碼器可以產生大量隨機激勵,所以本文中采用UVM驗證方法學,結合SV驗證語言,搭建層次化驗證平臺,解決了手動遍歷所有配置信息的問題,實現了驗證的高效性。

1 ?Viterbi譯碼器優化算法

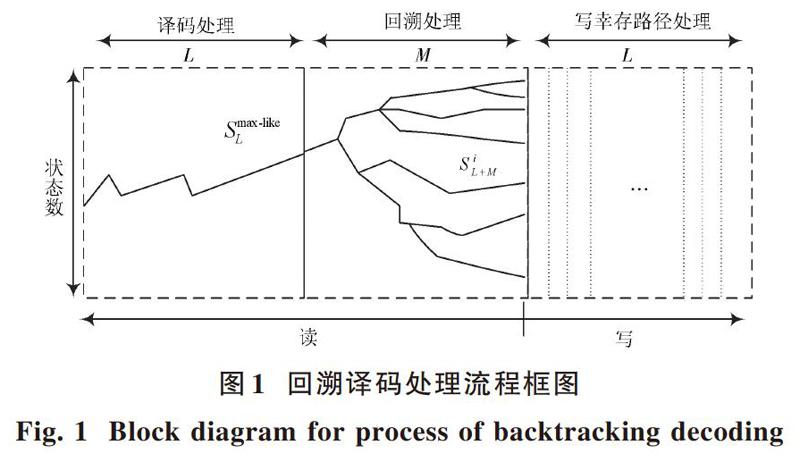

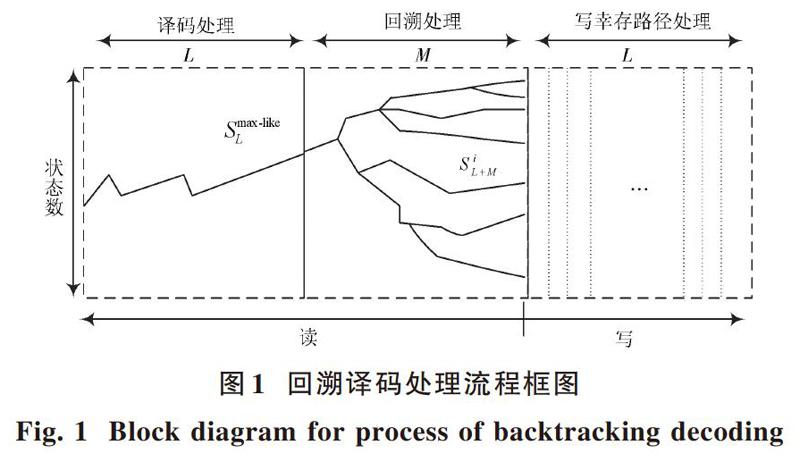

傳統的回溯方法在文獻[4?5]中進行了詳細的介紹。為了減小傳統回溯方法中的譯碼延遲,本方案中采用基于數據一致性原則的前向回溯譯碼方法(Pre?traceback,PTB),同時引入指針寄存器,在基四結構下,通過64狀態交換單元組成的交換網絡來得到DC(Decoding,DC)操作的起始狀態。如圖1所示,所有狀態經過M步回溯處理以后,將匯聚到同一個狀態。在起始回溯時,選擇任意起始狀態,通過一定級數回溯后,路徑會收斂于最大似然狀態。

采用 PTB 處理后從幸存路徑寫入到譯碼比特出來延時大小為 3L,減小了后向回溯處理中存儲器讀/寫次數。Idle表示空閑狀態,不做任何操作。 前向回溯法讀/寫次數時序圖如圖2所示。

2 ?Viterbi譯碼器實現方案

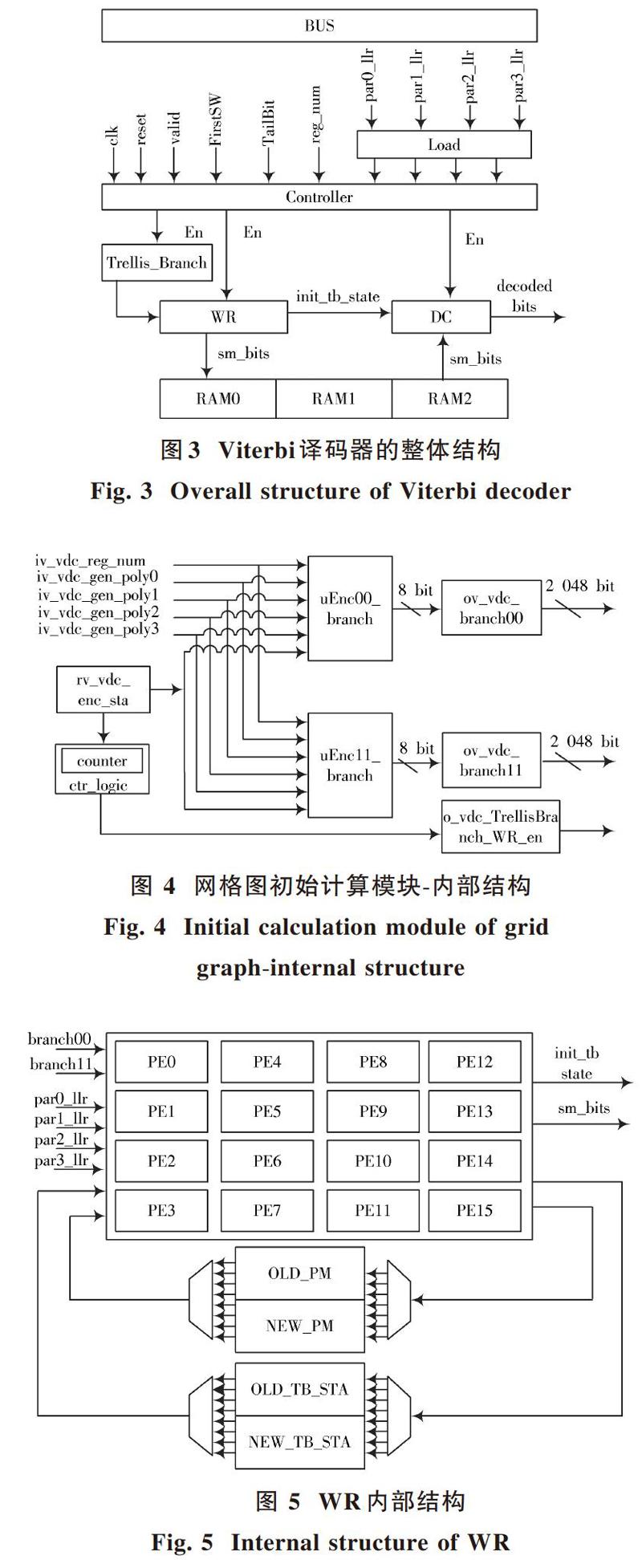

文中Viterbi譯碼器主要根據LTE卷積編碼(3,1,7)設計的,其是一個支持多標準、高性能、可配置的Viterbi譯碼器。Viterbi譯碼器的整體結構圖如圖3所示。

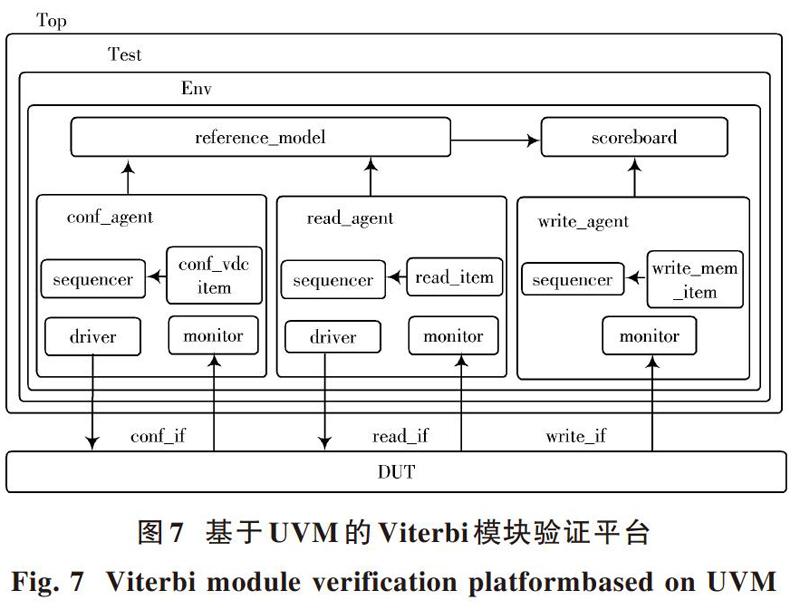

Trellis_initial是網格初始化單元,根據碼率、生成多項式、約束長度初始化trellis圖的分支路徑,對于基四算法來說,需要生成4路輸出,分別是“00”,“01”,“10”,“11”分支產生的校驗比特。這4條分支產生的校驗比特用于分支度量的計算。經過簡化,本方案中只需要產生2路分支,即“00”分支和“11”分支,得到的發送序列用于計算分支度量,從而完成譯碼器的可配置。網格圖內部計算結構如圖4所示。

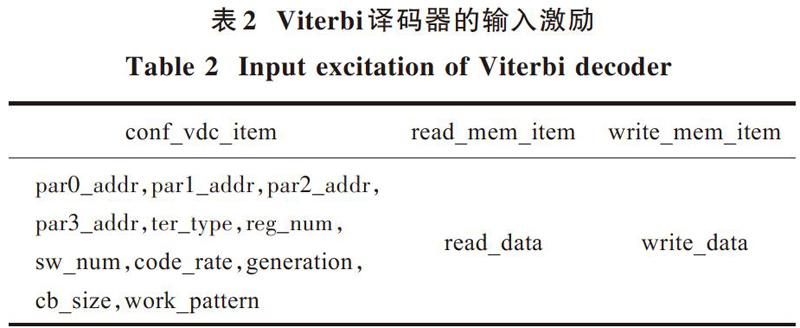

WR(Write)是前向狀態遞歸計算單元,本設計中一共有64個ACS單元,每4個組成一個蝶形處理單元,共有16個蝶形處理PE(Processing Element)單元。WR內部計算結構如圖5所示。

ACS單元內部結構圖如圖6所示,單元內部增加少量減法器來減小譯碼延遲,同時采用減規約操作,每次減去前一時刻的某一個狀態度量值,比模規約算法少了兩級異或延遲。

DC是譯碼單元,回溯譯碼單元從RAM中讀取的數據是128位寬,譯碼時首先要從128 bit中選出對應回溯狀態的2個幸存比特,然后利用幸存比特更新回溯狀態,同時取回溯狀態的高兩位作為譯碼輸出。

綜上所述,本文中通過對配置參數的靈活性支持,采用前向回溯譯碼和流水操作,得到了可配置的Viterbi譯碼器。

3 ?Viterbi譯碼器驗證

本文基于UVM驗證方法學結合SV語言,設計了Viterbi譯碼器驗證平臺,如圖7所示。

在該平臺中例化了三個agent,分別是conf_agent,read_agent和write_agent,定義了三個interface,分別是conf_if(配置接口)、read_if(讀數據接口)、write_if(寫數據接口),來實現信息配置,數據讀取和寫入。本文中采用的reference model是基于C語言編寫的參考模型,通過DPI(Direct Programming Interface)[9]接口將其接入到驗證平臺中,最終在scoreboard中實現和DUT(Design Under Test)的結果比對。通過比對,判斷DUT的功能是否正確。下面對所設計的驗證組件進行了簡單的討論。data_item產生DUT的輸入激勵,這些輸入激勵可以是輸入數據,也可以是一些配置信息,如表2所示,為本方案中所需要的配置和數據激勵。

conf_vdc_item生成Viterbi譯碼需要的配置信息,包括4路檢驗信息的地址、結尾方式、寄存器個數、滑窗個數、碼率、生成多項式的配置、工作模式、碼塊大小;read_mem_item產生輸入激勵信息;write_mem_item存儲Viterbi譯碼結果,用于和reference model的譯碼結果比較。

sequencer負責發送sequence_item(conf_vdc_item,read_mem_item,write_mem_item)到 driver,并接收driver發回來的一個響應。driver是一個主動的主體,負責將 read_mem_item,write_mem_item 里的信息驅動到 DUT 的端口上,monitor是一個被動的主體,負責監測輸入激勵和譯碼結果,在write_agent里只例化了monitor。

4 ?結果與分析

4.1 ?基四算法下的性能仿真結果

基四算法下的性能仿真結果如圖8所示。該仿真中碼塊長度1 600,碼塊個數10 000,AWGN信道,采用QPSK調制。從圖8中可以看出,基四算法下的前向回溯譯碼性能優于基二算法,性能提升約1 dB。

4.2 ?性能對比

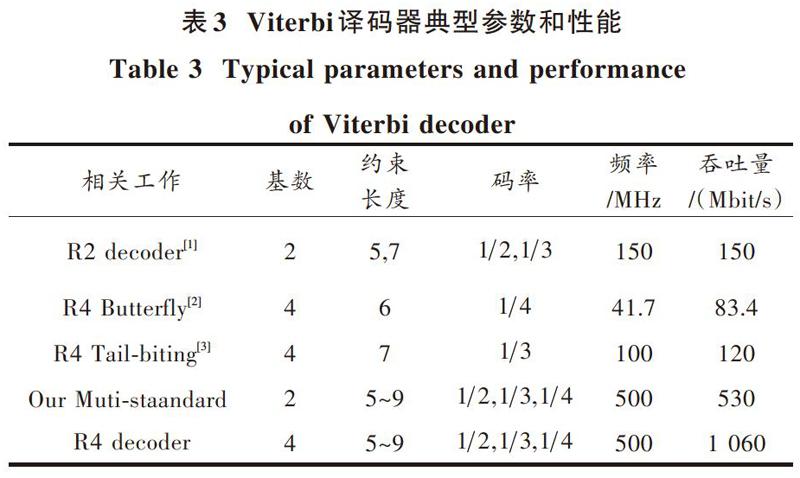

表3列出了本設計中基二、基四算法下Viterbi譯碼器典型參數和性能,以及其他相關工作中的性能對比,主要包括基數、約束長度、碼率、頻率和吞吐率。由表3可知,本文實現的Viterbi譯碼器不但性能更高,而且靈活性更強,可以支持約束長度在5~9,碼率在[12,13,14]間變化,并支持GPRS,WiMAX,IS?95 CDMA,LTE,CDMA 2000等多種通信標準。

4.3 ?DC綜合結果

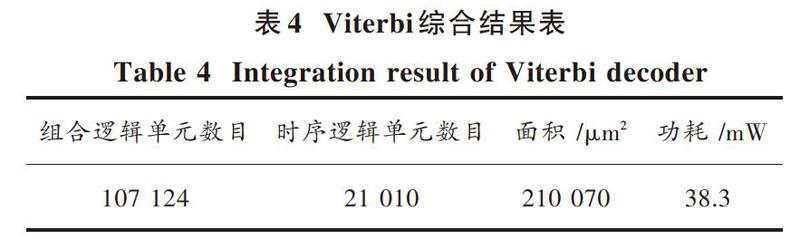

本文設計采用TSMC 28 nm標準單元庫,利用Synopsys Design Compiler進行綜合,主頻設為500 MHz,綜合結果如表4所示。

4.4 ?驗證結果

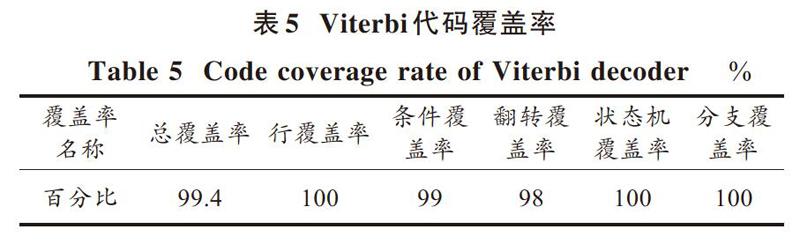

軟件仿真是在Linux環境下,利用VCS編譯UVM庫進行的,設置的碼塊個數為300個。通過在scoreboard里判斷DUT和rererence model的結果,若譯碼結果一致,打印“compare success!”字樣,否則打印“compare failed!”。本文中最終打印結果全部打印的“compare success!”,說明維特比譯碼器譯碼正確。表5列出了最終代碼覆蓋率。

以上結果說明本文中設計的驗證平臺達到了預期要求,實現了對Viterbi譯碼器的功能驗證。

5 ?結 ?語?

本文通過配置Viterbi譯碼器的動態參數實現了支持不同標準的譯碼器,并通過仿真驗證。在500 MHz主頻下,峰值吞吐可以達到1.06 Gbit/s。對于支持多標準的譯碼器來說,明顯優于其他設計。利用Synopsys Design Compiler工具進行綜合,500 MHz主頻下,功耗為38.3 mW,且仿真結果表明,該譯碼器具有較好的譯碼性能,值得應用推廣。同時在驗證領域中,本文采用UVM驗證方法學搭建的驗證平臺成功復用到CRC(Cyclic Redundancy Check)檢驗的模塊中,極大地提高了驗證的效率和平臺的復用性。

參考文獻

[1] BATCHA M F N, SHA′AMERI A Z S. Configurable adaptive Viterbi decoder for GPRS, EDGE and Wimax [C]// Proceedings of IEEE International Conference on Telecommunications and Malaysia International Conference on Communications. Penang: IEEE, 2007: 237?241.

[2] YUAN H H, HSU C Y, KUO T S. Low complexity Radix?4 butterfly design for the Viterbi decoder [C]// Proceedings of IEEE Vehicular Technology Conference. Montreal: IEEE, 2006: 1?5.

[3] ABDALLAH R A, LEEY S J, GOEL M, et al. Low?power pre?decoding based viterbi decoder for tail?biting convolutional codes [C]// Proceedings of IEEE Workshop on Signal Processing Systems. Tampere: IEEE, 2009: 185?190.

[4] MANZOOR R, RAFIQUE A, BAJWA K B. VLSI implementation of an efficient pre?trace back approach for Viterbi algorithm [C]// Proceedings of International Bhurban Conference on Applied Sciences and Technology. Islamabad: IEEE, 2007: 27?30.

[5] 薛蓮.MIMO?OFDM系統二相ACS前向回溯基四Viterbi譯碼器設計與實現[J].科技通報,2013,29(9):176?180.

XUE Lian. Design and implementation of two?phase ACS and pre?traceback Radix?4 Viterbi decoder for MIMO?OFDM system [J]. Bulletin of science and technology, 2013, 29(9): 176?180.

[6] 李炎琨.基于VMM驗證方法的研究[D].西安:西安電子科技大學,2010.

LI Yankun. The research of VMM?based verification method [D]. Xian: Xidian University, 2010.

[7] 柏才明.基于OVM的SoC功能驗證系統的設計與實現[D].武漢:華中科技大學,2011.

BAI Caiming. Design and implementation of OVM?based SoC function verification system [D]. Wuhan: Huazhong University of Science and Technology, 2011.

[8] 張弓.可配置的Viterbi譯碼器的FPGA實現[D].西安:西安電子科技大學,2009.

ZHANG Gong. Implementation of a configurable Viterbi decoder with FPGA [D]. Xian: Xidian University, 2009.

[9] Accellera. Universal verification methodology (UVM) 1.2 user′s guide [EB/OL]. [2015?11?06]. https://wenku.baidu.com/view/19eced832f60ddccdb38a05b.html.

[10] 3GPP. TS 36.212?2009 multiplexing and channel coding (V8.7.0) [S]. [2009?06?01]. http://www.zbgb.org/147/StandardDetail

2505982.htm.

[11] Accellera. Universal verification methodology(UVM)1.2 class reference [EB/OL]. [2013?12?16]. http://ishare.iask.sina.com.cn/f/65070280.html.