內存推移理論及其實驗

李凱凱,金 翊,歐陽山,周時強

三值光學計算機[1-10]具有數據位眾多、按位可重構、按位可分配等應用特色[11-15],適合處理大批量數據[16-18].正是由于這些特性,使得三值光學計算機對存儲器有特殊要求:一是能夠在處理器與非易失性存儲器之間高速交換大量數據;二是需要大容量的隨機訪問存儲器,目前的容量要求為數百GB或TB量級,且在這方面的要求會越來越高.由于在傳統的電子計算機存儲體系中,非易失性存儲器(TB級容量的外存)與CPU之間的數據交換需要由隨機訪問存儲器(GB級容量的內存)來中轉,故難以滿足三值光學計算機對存儲器的特殊要求.因此,需要為三值光學計算機研發具有大容量、高訪問速度、非易失且可以被隨機讀寫的新型存儲器系統.

為滿足三值光學計算機對存儲器的新需求,2013年上海大學三值光學計算機研究團隊提出了雙空間存儲器結構和理論[19-20].這種新的存儲體系將非易失性塊地址空間和隨機訪問字地址空間落實到由非易失性隨機訪問存儲器(non-volatile random access memory,NVRAM)構成的同一個存儲器實體上,其中最關鍵的是將傳統內存空間映射到巨大的雙空間存儲器不同段落上的新理論——內存推移理論.雙空間存儲器及其內存推移理論已經在理論和模擬實驗中獲得成功,因此用實物來實現雙空間存儲器和內存推移理論成為最終證實這一新型存儲體系和相關理論的關鍵,也是在實踐中完善雙空間存儲器理論的關鍵一環.本工作詳細介紹了所構建的第一個內存推移寄存器組及所完成的內存推移操作.由于雙空間存儲器和內存推移理論可以與各種處理器配合,將其應用于電子計算機后,會徹底消除大量數據和程序在內存與外存之間的復制過程,有效提高電子計算機的效率,并且能夠自然地實現對隨機寫入數據的非易失性保存,非常有利于實施目前廣受關注的內存計算技術.因此,在本工作給出的實驗研究中以常用的嵌入式系統[21]S3C2440為處理器,通過將一個bank的2 MB內存空間在1 GB隨機訪問字空間上任意推移,證實了雙空間存儲器理論和內存推移理論在理論上的正確性和實踐上的可行性.

1 基礎理論

1.1 雙空間存儲器

文獻[19-20]給出了雙空間存儲器的詳細理論、結構和技術,并指出:雙空間存儲器是利用NVRAM構造的新型存儲系統,同時具有非易失存儲特性的塊空間和可隨機訪問的字空間.雙空間存儲器將內存空間和外存空間落實在同一個存儲實體上,塊空間在雙空間存儲器上安裝的程序和保存的數據可以通過字空間運行和隨機訪問,完全省去了程序和數據在內存與外存之間的拷貝過程,從而大幅度提高了計算機的運行效率.文獻[19]還指出:如果將操作系統、程序注冊表等系統運行的基本程序和數據放置在CPU可以永久訪問到的字空間范圍——不可閉窗(詳情見2.5節)中,就可省去開機時引導操作系統的過程;如果在不可閉窗內增設一個關機狀態表來記錄關機時刻CPU的運行現場,就可在下次開機時從關機狀態表迅速恢復上次關機時CPU的現場,實現開機后CPU立刻接續上次關機時的工作,使開關計算機如同開關電燈.

由于NVRAM技術的進步,尤其是2015年8月公布的3D Xpoint技術提供了性能卓越的NVRAM器件,用NVRAM構造計算機的存儲器已成為未來的潮流.Intel公司已于2016年4月宣稱其下一代PC——OPTANE將使用NVRAM來構造內存.考慮到64位CPU的內存地址線已經多達64根,而理論上OPTANE的內存可達264B,即16 EB容量(雖然這個內存對于PC來說太大了,即便只使用40根地址線,也能構造出1 TB的超級內存).超級內存足以容納PC的所有程序和數據,而不再需要外存,但是要把當前存儲于U盤、光盤、硬盤和網絡上的以塊為單位來組織和管理的文件裝入這個超級內存,就需要在超級內存上構造出塊空間.一旦再構造了塊空間,超級內存就在事實上成為了雙空間存儲器的一個實例.

1.2 內存推移理論

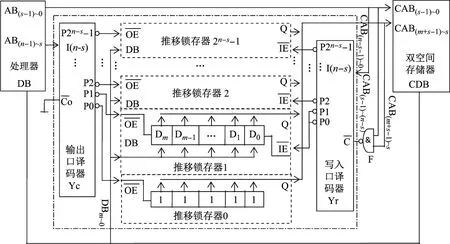

三值光學計算機研究團隊在構造雙空間存儲器時,發明了將內存空間自動映射到巨大的雙空間存儲器字空間上任意區段的技術,稱為內存推移理論.這項發明的核心是構造了如圖1中點劃線框內所示的推移鎖存器組以及相應的操作技術.

圖1推移鎖存器組結構Fig.1 Structure of the latch group

圖1 中的處理器可以是任何種類的CPU或內存訪問主控設備,此處采用常見的簡單處理器——嵌入式系統S3C2440.假設圖1中處理器的內存地址線有n條(AB(n?1)~0),其中低序號的s條地址線(AB(s?1)~0)與雙空間存儲器中低序號的s條地址線(CAB(s?1)~0)相連接;而其余的n?s條高序號地址線(AB(n?1)~s)連接到推移鎖存器組輸出口譯碼器Yc的輸入端I(n?s);處理器的數據總線DB連接到雙空間存儲器的數據總線CDB,其中m+1條數據線(DBm~0)還連接到各個推移鎖存器(除推移鎖存器0外)的數據輸入端DB.

圖1中的推移鎖存器組包含2n?s個推移鎖存器,設定編號為推移鎖存器0~2n?s?1,還包含一個輸出口譯碼器Yc和一個寫入口譯碼器Yr.推移鎖存器0的構造與其他推移鎖存器不同.它沒有數據輸入端DB和寫入控制端IE(—表示低電平有效),因此其設定值(圖1中均設定為1)不可能被修改,但數據輸出口Q及其輸出控制端與其他推移鎖存器相同.推移鎖存器1~2n?s?1的結構完全相同.它們的數據輸入口DB都連接到處理器數據總線的DBm~0上.當某個推移鎖存器的寫入控制端IE有效時,DBm~0上的數據將寫入該推移鎖存器并被保存,從而修改該推移鎖存器的值Dm~D0.

Yc的每個輸出端P i(i=0,1,···,2n?s?1)分別控制一個推移鎖存器的輸出控制端OE,故稱Yc為輸出口譯碼器.Yc的輸入端I(n?s)連接處理器內存地址線的高序號部分AB(n?1)~s,同時其有效使能端Co接地,于是Yc總有效.因此,處理器內存地址線的高序號部分AB(n?1)~s的編碼i總是被Yc譯碼.譯碼完成后,Yc的輸出端P i使推移鎖存器i的輸出控制端有效,于是推移鎖存器i將其保存的m位數據(Dm~D0)經數據輸出口Q送到雙空間存儲器地址線的m根高序號地址線(CAB(m+s?1)~s)上.推移鎖存器i將處理器送出的內存地址AB(n?1)~0自動映射為雙空間存儲器的CAB(m+s?1)~0地址,而處理器本身完全不會受到影響.當處理器對內存空間的訪問維持在低序號地址線AB(s?1)~0上的情況發生改變,而高序號地址線AB(n?1)~s的值i不變時,推移鎖存器i保持被選通.此時,雙空間存儲器的高序號地址線(CAB(m+s?1)~s)的值不改變,處理器對AB(s?1)~0給定的內存地址范圍的訪問全部被推移鎖存器i自動引導到由CAB(s?1)~0給定的雙空間存儲器范圍內.因此,稱內存空間范圍AB(s?1)~0為映射窗,稱雙空間存儲器范圍CAB(s?1)~0為窗壁——剛好能安置一個映射窗的墻壁.一個窗壁上的所有存儲單元的高序號地址線CAB(m+s?1)~s相同,故選用這個值作為窗壁編號.當一個推移鎖存器被選通后,其值Dm~D0被送上CAB(m+s?1)~s,因此Dm~D0本質上就是窗壁編號.推移鎖存器通過保存的窗壁編號將映射窗引導到指定的窗壁.針對這一過程,可以形象地認為每個推移鎖存器有一個虛擬的存儲空間,稱其為窗框,推移鎖存器的編號i就是對應的窗框編號.于是,推移鎖存器i的值為Dm~D0,就是將第i號窗框安置在Dm~D0號窗壁.給每個推移鎖存器賦不同的值,就是將所有的窗框安置在了不同的窗壁上.內存地址線的高序號部分AB(n?1)~s的每個值都會選擇一個推移鎖存器,等同于選擇一個窗框,因此所有窗框的容量之和正好就是內存空間的大小.AB(n?1)~s的改變就是把映射窗從一個窗框移到另一個窗框——映射窗推移.顯然,映射窗無法到達沒有窗框的窗壁,這就是引入窗框概念的根本原因.

Yr的每個輸出端P j(j=1,2,···,2n?s?1)分別控制一個推移鎖存器的寫入控制端,故稱Yr為寫入口譯碼器.Yr的有效使能端C與非門F的輸出端相接,F的輸入為雙空間存儲器的高序號地址線CAB(m+s?1)~(n?s),同時Yr的輸入端I(n?s)連接雙空間存儲器低序號地址線CAB(n?s?1)~0. 當訪問雙空間存儲器的高序號地址線CAB(m+s?1)~(n?s)不全為1時,Yr無效,Yr的所有輸出端P j都輸出1,所有推移鎖存器的寫入控制端均無效,所有推移鎖存器都不接收DBm~0上的值,則推移鎖存器自身保持的數值都不會被改寫.僅當CAB(m+s?1)~(n?s)全為1時,Yr的C有效. 這時Yr輸入端I(n?s)收到CAB(n?s?1)~0上的地址碼j,相應地使其輸出端P j為低電平,其他輸出端均為高電平.于是推移鎖存器j的寫入控制端有效,該推移鎖存器j就會接收處理器數據總線DBm~0上的值來修改自身保持的數值,而其他推移鎖存器則無改變,推移鎖存器j對應的窗框j被移動到新的窗壁上——窗框推移.考慮到各個推移鎖存器的寫入控制端在CAB(m+s?1)~(n?s)全為1時有效,可知各推移鎖存器的寫入控制端被安排在雙空間存儲器高序號地址線的一段連續區域(CAB(n?s?1)~0的取值范圍),稱這段地址范圍為推移矢量表.

顯然,內存推移理論能夠顯著減少處理器隨機訪問雙空間存儲器所需的地址線數目,無需內存分頁管理技術,可方便地實現多處理器共享/分享存儲器技術.這意味著內存推移理論將降低CPU的硬件復雜度和內存管理復雜度,增加CPU使用存儲器的靈活性.

2 實驗系統設計

2.1 實驗目標

本工作通過以下具體實驗驗證了內存推移理論[22-24]:①改變處理器訪存地址的低位,驗證映射窗的存在和處理器透過映射窗對雙空間存儲器的隨機訪問能力;②改變處理器訪存地址的高位,驗證映射窗推移技術;③修改推移鎖存器的值,驗證窗框推移技術;④修改推移鎖存器0的操作,驗證不可閉窗的存在.

鑒于本工作的研究目標是內存空間在雙空間存儲器字空間上的推移理論,而該理論與雙空間存儲器的塊空間無關,故不考慮雙空間存儲器中塊空間的各類問題.

2.2 雙空間存儲器設計

內存推移理論的功能是將較小的內存空間分時映射到大容量雙空間存儲器的不同區段.本實驗的目標在于驗證這項理論的正確性和可行性,因此所設計的雙空間存儲器只要比被推移的內存空間總容量大數百倍即可.鑒于本實驗設定的內存空間總容量為2 MB(S3C2440處理器內存空間的一個bank),故選用1 GB的雙空間存儲器.相應地,設計該雙空間存儲器地址線為30根,定義為CAB29~0.為簡化實驗操作,還約定只使用占連續4個字節地址的32位數據總線寬度.

為節約實驗成本,在保證實驗目標不受損害的前提下,本實驗在多種NVRAM中選用常見的型號為S29GL01GNOR Flash芯片來構建雙空間存儲器.這種芯片的存儲容量在字模式下為64 M×16位,故本實驗用2片S29GL10G芯片經地址線并接且數據線并列后,形成64 M×32位的存儲芯片對,再用4對存儲芯片構造出1 GB的雙空間存儲器.由于本實驗是以連續4個字節的32位寬度來使用數據總線,故無需使用處理器的AB0和AB1地址線,而將處理器地址線AB2連接到雙空間存儲器地址線的CAB0.依此類推,處理器地址線ABn連接雙空間存儲器地址線CABn?2.

2.3 推移鎖存器組設計

推移鎖存器組是連接CPU與雙空間存儲器字空間的重要紐帶.對于CPU來說,推移鎖存器組屏蔽了雙空間存儲器的容量大小;對于雙空間存儲器來說,推移鎖存器組屏蔽了CPU的尋址能力.因此,只要有合適的推移鎖存器組,CPU就能夠和雙空間存儲器協同工作.因此,推移鎖存器組的結構要由系統中的CPU與設定的雙空間存儲器共同決定.

推移鎖存器組中包含的鎖存器數量等于窗框的數量.從圖1中可以看出,窗框的數量與映射窗的大小存在制約關系,映射窗變大一倍,窗框的數量就減少一半.在本實驗中,被推移的內存空間總容量為2 MB,若設定映射窗大小為218B(256 KB),則相應的窗框數量為2(21?18)個,即設定推移鎖存器組包含8個鎖存器.

每個推移鎖存器的有效鎖存數據位數取決于雙空間存儲器的窗壁數量.對于給定的雙空間存儲器,窗壁的數量由窗壁的大小來決定,而窗壁的大小等于映射窗的大小,故本實驗的窗壁大小為256 KB.于是1 GB的雙空間存儲器就有2(30?18)=4 096個窗壁,編號為0~4 095,因此每個推移鎖存器要有12位.本實驗采用16位的鎖存器74ACT16373來構造推移鎖存器,將其低12位作為有效值,高4位棄之不用.

2.4 推移指令設計

對推移鎖存器的操作分為映射窗推移和窗框推移兩種.在系統設定完畢后,每當處理器給出的內存地址高位部分發生改變,系統就自動完成映射窗推移,無須為此設置專門的指令.而窗框推移必須改變相應的推移鎖存器的值,這是對特定地址的賦值操作,對應著一條特定的賦值指令,即推移指令.在系統設定中,每個推移鎖存器都有獨立的寫入端口,且每個寫入端口都與雙空間存儲器的一個隨機訪問地址相關聯,故稱該地址為推移鎖存器的寫入端地址[20].此時,對推移鎖存器的具體賦值操作如下:CPU給出一個特定的內存地址,其高位部分選擇特定的不可修改推移鎖存器,即將映射窗推移到一個特定的窗壁,而該內存地址的低位部分則在該窗壁中選通一個可修改推移鎖存器的寫入端口,并通過賦值指令修改該推移鎖存器保持的值.于是,推移指令的形式為向內存空間特定地址賦值的語句,且給出的新數值為目標窗壁的編號.

本實驗中的處理器部件選用基于S3C2440制作的TQ2440 Core 2.0核心板.S3C2440處理器采用I/O端口和存儲器統一編址方式,指令使用32位尋址,但僅設置30根外部存儲器的邏輯地址線,對應的地址范圍為0000 00000~3fffffffH,故最多可外接存儲器1 GB,且指令中32位地址的最高兩位無效.將30根外接地址線分為兩組:低27根以地址線的形態給出,稱為A26~A0;高3根則以8根bank使能線的形態給出,稱為bank7~bank0,即將外接存儲器的1 GB空間分成8個128 MB的bank,由指令中的A29~27來選通各bank的使能端,其中選通bank1使能端的地址是A29~27=001B.

TQ2440 Core 2.0核心板對外提供了21根地址線A[20∶0]和bank1~bank5以及bank7的使能線,因此該核心板允許給bank1~bank5以及bank7各外接2 MB隨機訪問存儲器.在不影響實驗目標的前提下,為方便設計,本實驗僅將bank1的2 MB外接隨機訪問存儲器空間用于推移操作的內存空間,所以A[20∶0]就是本實驗的處理器地址線AB20~0.對于這2 MB外部擴展內存,S3C2440的地址線A26~21無意義,因此默認為00 0000B.于是,當S3C2440處理器訪問本實驗所設定的內存空間時,在指令中必須給出如下的的32位地址:0800 0000H~081fffffH,此處稱其為訪存地址.

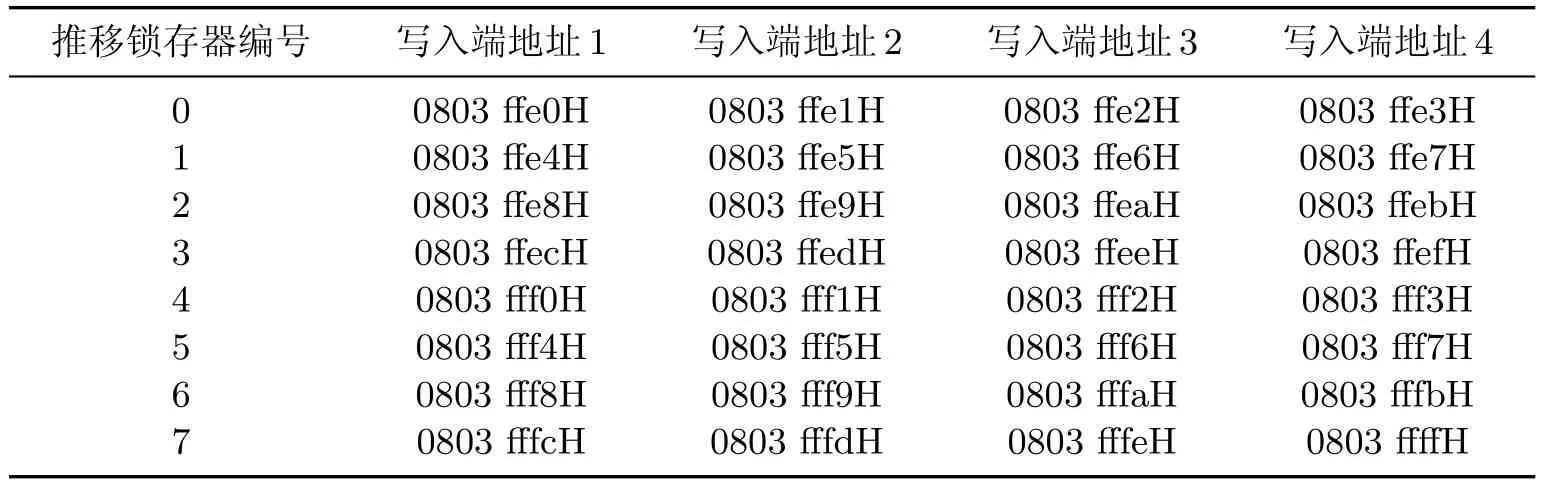

在本實驗中,通過地址線的具體連接方式將8個推移鎖存器的寫入端地址設定在雙空間存儲器字空間的3fffffe0~3fffffff區域,即設定在第4 095號窗壁地址最高的32個字節中,并設定通過推移鎖存器0訪問0fffH號窗壁.于是,當改寫推移鎖存器的值時,必須先保證推移鎖存器0中保有0fffH值,再用寫入訪存地址0803ffe0H~0803ffffH范圍的指令來改寫相應的推移鎖存器,從而將對應的窗框移動到指定的窗壁.由于S3C2440處理器的A0和A1地址線沒有參與雙空間存儲器尋址,故每個推移鎖存器的寫入端有4個連續的訪存地址(見表1),其作用完全相同,本實驗只使用寫入端地址1.推移鎖存器2的寫入端訪存地址為0803ffe8H,由于本實驗總是以連續4個字節的32位寬度來使用數據總線,因此將2號窗框推移到第1 024號窗壁上的推移指令為*(unsigned int*)(0x0803ffe8)=0x0400,其中0x是十六進制數據前綴.

表1 推移鎖存器寫入端地址Table 1 Write end addresses for the latch group

2.5 不可閉窗設計

計算機系統復位后,將自動執行位于特定地址的第一條指令,并由此轉入系統的初始化程序,而在系統運行時,又需要將常用程序或者常用數據駐留在內存中,以確保較高的訪問速度.在使用雙空間存儲器的新型電子計算機中,內存空間對應所有窗框組成的空間.而程序和數據都位于窗壁上,于是駐留內存的程序和數據對應的窗壁永遠可以被隨機訪問.這意味著該窗壁上的窗框永久存在,不得被移走.這種窗壁被稱為不可閉窗,其對系統運行至關重要.

由于本實驗使用的是掉電易失性鎖存器,為了彌補這一不足,將采用以下方案:先對選定的推移鎖存器寫入選定的不可閉窗的窗壁編號,然后手動將推移鎖存器的寫入控制端接入低電平,使該推移鎖存器成為不可修改,對應的窗框就永久駐留在選定的窗壁上,使得該窗壁成為不可閉窗.本實驗選定4 095號窗壁為不可閉窗,持續占有0號窗框,于是對推移鎖存器0實施上述操作.

2.6 實驗板電路設計和制作

本實驗的主要目標是用實物系統來驗證雙空間存儲器的核心理論——內存推移理論.由于雙空間存儲器是三值光學計算機研究團隊在2013年提出的新型存儲器理論和結構,在本實驗成功之前尚沒有實物存在.因此,本實驗將設計和制作出第一個真實的雙空間存儲器系統并實施內存推移操作.

在規劃本實驗時,考慮到構造實際系統的可靠性、簡潔性和實驗操作的方便性,采用廣州天嵌計算機科技有限公司生產的TQ2440 Core 2.0核心板作為處理器部件.該板已經將嵌入式處理器S3C2440焊接好并以標準排針插口引出了所需的地址線、數據線和控制線,而且有較好的上位機監控調試軟件及人機界面.該核心板對外只提供了21根內存地址線A[20∶0],故可以外接的內存空間為2 MB.本實驗將制作一個1 GB的雙空間存儲器和相應的推移鎖存器組,然后在所設計的實驗系統上驗證內存推移理論.

依據圖2所示的系統連接原理圖完成實驗板設計,其中核心板給出的高序號地址線A20~18接入輸出口譯碼器的輸入端,用于尋址推移鎖存器的輸出端;推移鎖存器組輸出端的12根信號線Q11~0與雙空間存儲器的高序號地址線A27~16相連;核心板給出的低序號地址線A17~2與雙空間存儲器的低序號地址線A15~0相連;核心板給出的數據總線和雙空間存儲器的數據直接互連.

圖2 系統連接原理圖Fig.2 Schematic diagram of the system connection

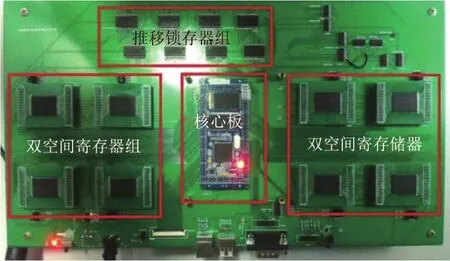

采用Altium Designer軟件設計本實驗的電路板.在電路板上焊裝各種元件和芯片后,組裝雙空間存儲器以及TQ2440 Core 2.0核心板,構成預期的內存推移實驗系統(見圖3).

圖3 內存推移實驗系統Fig.3 Experimental system of the pulling memory mapping

3 實驗操作規劃

內存推移理論的核心理論如下:①用NVRAM構造大容量的雙空間存儲器;②構造推移鎖存器組;③處理器透過映射窗機制隨機訪問窗壁的字單元;④用推移指令在雙空間存儲器字空間上移動窗框.由于雙空間存儲器和推移鎖存器組構建在實驗板上,其正確性將通過驗證核心理論③和④中的兩項技術來證實.因此,本實驗在操作方面的重點內容是這兩項技術的實施.

3.1 實驗準備

實驗準備主要包括兩方面的工作.

(1)編寫目標程序.通過ARM Developer Suite v1.2平臺編寫本實驗需要的目標程序,其中包括嵌入式系統的基本設置以及用于驗證內存推移理論的操作.用推移指令對推移鎖存器組中的每個推移鎖存器進行賦值,由S3C2440透過映射窗隨機訪問雙空間存儲器字空間對應窗壁上的字單元,修改推移鎖存器的值,完成在雙空間存儲器字空間上推移窗框.用C語言編寫目標程序后,編譯鏈接將其轉換成bin文件,并等待燒寫到指定位置.

(2)搭建實驗平臺.實驗系統的主要軟件和硬件包括SuperVivi-USB-Transfer-Tool、PC機、TQ2440 Core 2.0核心板、雙空間存儲器、推移鎖存器組以及實驗板.開始實驗前連接好實驗板與PC機上的串口和USB口,其中串口用于SuperVivi-USB-Transfer-Tool與S3C2440上的軟件通信,PC機通過USB口向實驗板上的S3C2440處理器燒寫目標程序.

將以上環節準備完畢,確保無誤之后,通電等待實驗.

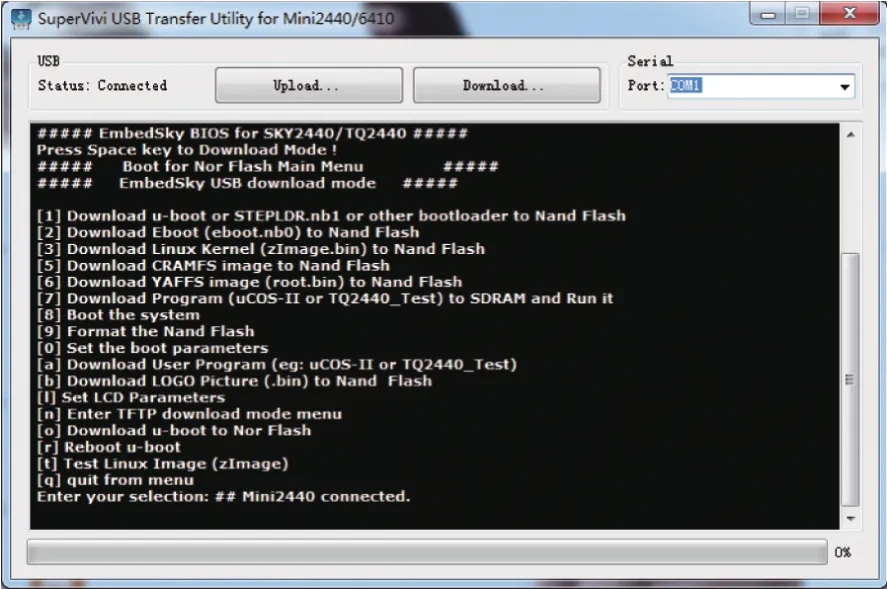

實驗預期結果:從SuperVivi-USB-Transfer-Tool的交互界面上得出TQ2440 Core2.0核心板連接成功,USB通行工作正常,串口工作正常;在所給出的命令中,選擇Download Program(uCOS-Ⅱor TQ2440Test)to SDRAM and Run it命令燒寫目標文件BispaceSimulation.bin到同步動態隨機存儲器(synchronous dynamic random access memory,SDRAM)中運行.

3.2 驗證推移指令的正確性

由于本實驗無法直接查看各個推移鎖存器中保持的數據,因此用邏輯分析儀對推移鎖存器組的輸出信號進行采集和分析,以此來確定被選通推移鎖存器所保持的數據.

實驗操作規劃:待目標文件BispaceSimulation.bin燒寫完畢后,目標程序會自動運行;目標程序首先執行嵌入式系統的基本設置,然后執行推移指令,實現對推移鎖存器組中每個推移鎖存器賦初值;用邏輯分析儀對推移鎖存器組的輸出信號進行采樣,以判斷各個推移鎖存器保存的數值是否正確.

具體操作如下:①給推移鎖存器寫入一個初始值,選擇一個選通該推移鎖存器的訪存地址進行訪問,記錄該推移鎖存器給出的數值;②通過推移指令給該推移鎖存器賦新值;③再次對上述訪存地址進行訪問,記錄該推移鎖存器給出的新數值;④查看邏輯分析儀中記錄的數值,判斷推移鎖存器所保存的數值是否正確.以上操作重復多次.

以對推移鎖存器1的實驗為例,說明操作過程如下:

volatile unsigned int*ip=(volatile unsigned int*)(0x0803ffe4)(選中推移鎖存器組中的推移鎖存器1的寫入端地址);

*ip=0x3f(向推移鎖存器1寫入初始值3fH);

unsigned int x=*(unsigned int*)(0x08040020)(訪問1號窗框,測得推移鎖存器給出的數值);

*ip=0x4aa(向推移鎖存器1賦新值4aaH);

unsigned int x=*(unsigned int*)(0x08040020)(再次訪問1號窗框,測得推移鎖存器給出的新數值).

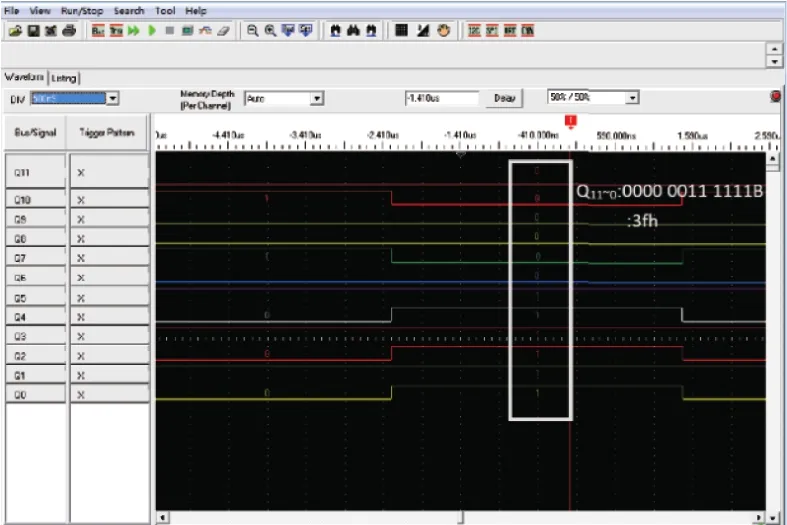

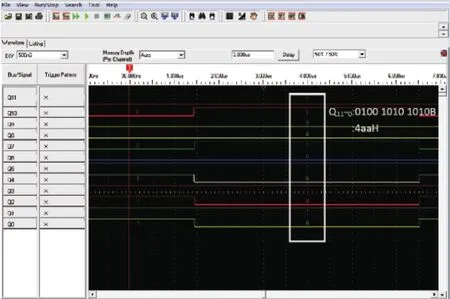

實驗預期結果:邏輯分析儀第一次應測得推移鎖存器的輸出值為3fH,第二次為4aaH.

3.3 透過映射窗隨機訪問窗壁的字單元

實驗操作規劃:初始化推移鎖存器組,給出對任意訪存地址的讀/寫命令,考察該命令的執行結果.

以訪問08040020H地址為例,說明此項實驗的操作過程如下:①執行推移指令*(unsigned int*)(0x0803ffe4)=0x400,將推移鎖存器1的值設定為400H,然后S3C2440處理器給出訪存地址08040020H,于是選通1號窗框,則將映射窗移動到雙空間存儲器的1 024號窗壁,透過映射窗內偏移地址20H,讀出對應存儲單元的內容,通過串口輸出到PC,在SuperVivi-USBTransfer-Tool的交互界面上顯示,截圖保留實驗結果;②對1 024號窗壁內的對應存儲單元寫入數值1234 4321H,本實驗系統只采用32位數據格式,且S3C2440處理器必須給出從0804 0020H開始的地址來訪問雙空間存儲器的連續4個字節(原因請參見2.4節);③從1 024號窗壁內的對應存儲單元讀出更新后的數據,截圖保留實驗結果;④比較第①,③步的實驗結果,判斷給出的讀/寫命令是否被正確執行.

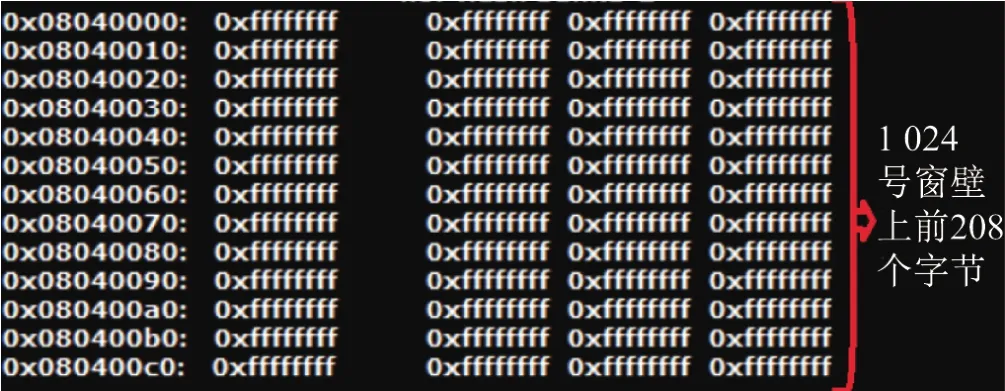

實驗預期結果:第①步,應得出1 024號窗壁內的對應存儲單元上的數據ffffffffH;第②,③步,應得出S3C2440處理器能夠將數據1234 4321H寫入1 024號窗壁內對應存儲單元,該窗壁的其他存儲單元保持NOR Flash芯片擦除后的數據ffH.

3.4 用推移指令在雙空間存儲器字空間上完成窗框推移

以訪問08040020H地址為例,說明此項實驗的操作過程如下:①通過推移指令*(unsigned int*)(0x0803ffe4)=0x600,將推移鎖存器1的值設定為600H,即將1號窗框推移到雙空間存儲器的1 536號窗壁,并對該單元寫入數值1122 3344H;②調用串口輸出函數Uart Print(“0x%08x”,*(unsigned int*)(0x08040020)),讀出該訪存地址的數值,在SuperVivi-USBTransfer-Tool的交互界面上顯示,截圖保留實驗結果;③用推移指令*(unsigned int*)(0x0803ffe4)=0x400,將推移鎖存器1的值重新設定為400H;④重復第②步,此時映射窗在雙空間存儲器的1 024號窗壁,偏移地址為20H的存儲單元內容應為1234 4321H(參見3.3節);⑤再次用推移指令*(unsigned int*)(0x0803ffe4)=0x600,將推移鎖存器1的值重新設定為600H;⑥重復第②步;⑦比較第②,④,⑥步中3次讀取到的同一訪存地址0804 0020H的內容,判斷第①,③,⑤步的推移指令是否都將1號窗框推移到了正確的窗壁.

實驗預期結果:通過3次訪問同一訪存地址為0804 0020H的存儲單元,應得到3個不同數據,第一次為1122 3344H,第二次為1234 4321H,第三次為1122 3344H.

3.5 不可閉窗的驗證

實驗操作規劃:通過修改推移鎖存器0的操作驗證不可閉窗的存在.

操作過程如下:①首先向推移鎖存器0寫入fffH,斷開推移鎖存器0的寫入控制端,使其接入低電平,完成設定4 095號窗壁為不可閉窗和持續占有0號窗框的操作;②訪問雙空間存儲器4 095號窗壁,訪問到的數據內容在SuperVivi-USB-Transfer-Tool的交互界面上顯示,截圖保留實驗結果;③再次向推移鎖存器0寫入400H,將0號窗框從4 095號窗壁推移到1 024號窗壁;④重復第②步;⑤比較第②,④步得到的數據結果,判斷第③步推移指令是否將0號窗框推移到其他窗壁上,驗證不可閉窗是否存在.

實驗預期結果:通過第②,④步兩次訪問到的內容應相同,都是4 095號窗壁上的數據,表示推移指令對不可閉窗無效,不可閉窗上的窗框永久存在,不能移走.

3.6 映射窗推移技術的驗證

實驗操作規劃:改變處理器訪存地址的高位,驗證映射窗是否得到推移.3.3和3.5節中分別用到了1號窗框和0號窗框,在完成驗證的過程中,多次改變了處理器給出的訪存地址高位,即已經多次把映射窗從一個窗框移到另一個窗框,因此綜合分析3.3和3.5節的實驗過程和記錄,即可對映射窗推移技術進行驗證.

操作過程如下:①得到3.3和3.5節的驗證結果;②分析3.3和3.5節的驗證結果,判斷處理器訪存地址高位的改變是否對映射窗進行了推移.

實驗預期結果:完成3.3和3.5節驗證實驗,驗證映射窗推移技術.

4 實驗過程及結果分析

4.1 實驗準備

按照實驗準備操作搭建實驗平臺.TQ2440 Core 2.0核心板從NOR Flash芯片模式中啟動,通電后,實驗結果和預期結果一致.圖4是SuperVivi-USB-Transfer-Tool的交互界面顯示結果.

圖4 SuperVivi-USB-Transfer-Tool的交互界面Fig.4 Interactive interface of Super Vivi-USB-Transfer-Tool

4.2 驗證推移指令的正確性

通過實驗測得推移鎖存器1的初始值為3fH(見圖5).在執行推移指令后的訪存中,測得的賦予推移鎖存器的新值為4aaH(見圖6).這說明通過推移指令已將數據4aaH正確寫入了推移鎖存器1中,推移指令的正確性得以驗證.

圖5 測得初始值3fHFig.5 Measured initial value 3fH

圖6 測得賦予推移鎖存器的新值4aaHFig.6 Measured initial values 4aaH given by the latch

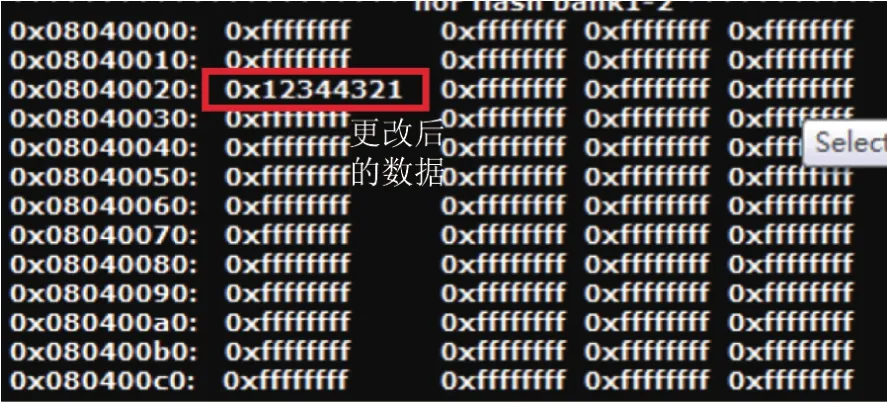

4.3 透過映射窗隨機訪問窗壁的字單元

從圖7可以看出,S3C2440處理器能正確訪問1 024號窗壁上的數據.從圖8可以看出,S3C2440處理器成功修改了1 024號窗壁上偏移地址為20H存儲單元上的數據,證明了S3C2440處理器能夠透過映射窗隨機訪問窗壁的正確字單元.

圖7 對1 024號窗壁上內容的訪問Fig.7 Access to the content of 1 024th window entity

圖8 訪問修改后的單元Fig.8 Access to the modifi ed unit

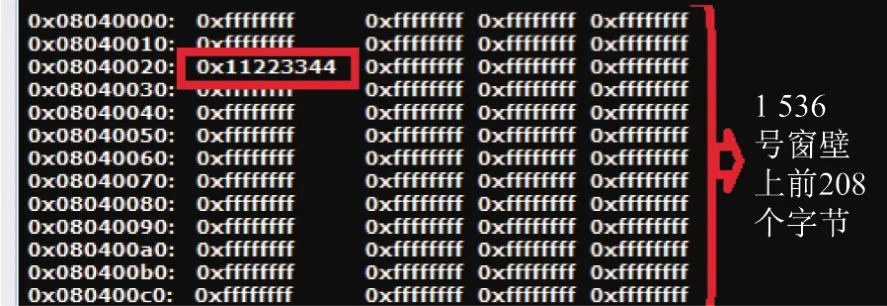

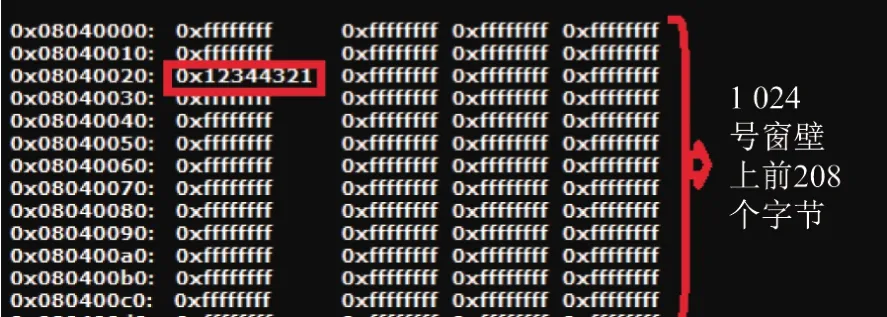

4.4 用推移指令在雙空間存儲器字空間上完成窗框推移

從圖9可以看出,S3C2440處理器成功訪問到了1 536號窗壁,并成功改寫偏移地址為20H存儲單元上的數據為1122 3344H.從圖10可以看出,通過推移指令實現了窗框推移操作,成功將S3C2440處理器引導到對1 024號窗壁的訪問,并訪問到3.3節中修改過的偏移地址為20H存儲單元上的數據1234 4321H.從圖11可以看出,再次通過推移指令實現了窗框推移操作,成功將S3C2440處理器又引導到1 536號窗壁,訪問到剛剛修改過的偏移地址為20H存儲單元上的數據1122 3344H.整個實驗過程中兩次用到推移指令,成功完成窗框推移操作.

圖9 第一次訪問Fig.9 First access

圖10 第二次訪問Fig.10 Second access

圖11 第三次訪問Fig.11 Third access

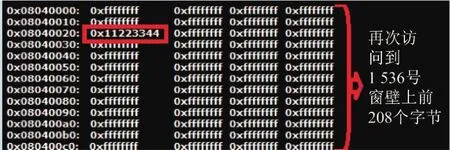

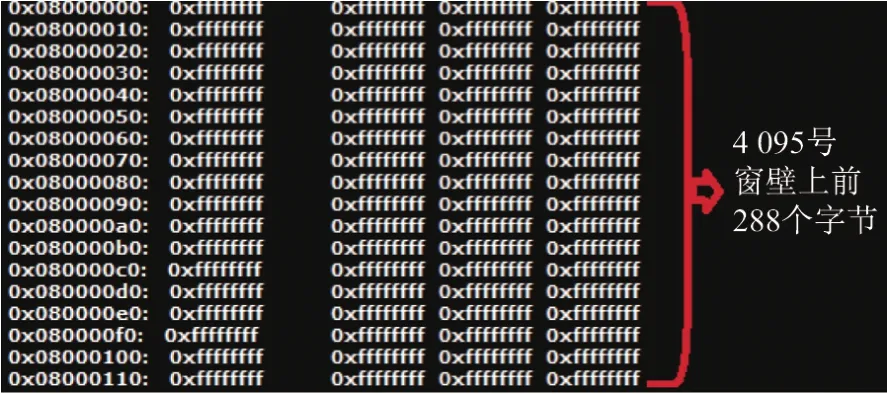

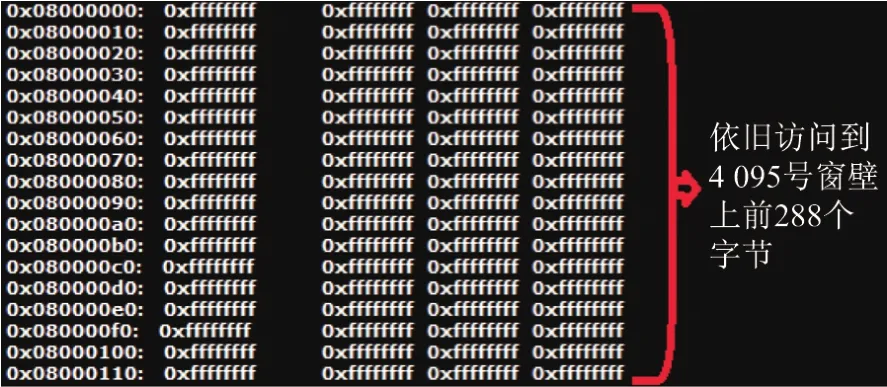

4.5 不可閉窗的驗證

從圖12可以看出,S3C2440處理器能正常訪問4 095號窗壁.從圖13可以看出,執行推移指令后無法實現窗框推移,不能將S3C2440處理器引導到1 024號窗壁,而是依舊停留在4 095號窗壁,說明4 095號窗壁為不可閉窗,持續占有0號窗框,不能被移動.

圖12 訪問0號窗壁上的數據Fig.12 Access to the data of the 0th window entity

圖13 執行推移指令后的訪問Fig.13 Access after pushing command

4.6 映射窗推移技術的驗證

實驗結果和預期一致,通過改變處理器訪存地址的高位,成功驗證了映射窗推移技術.對上述實驗重復多次,每次給出不同的參數,實驗結果均達到實驗目的,成功驗證了推移指令的正確性.S3C2440處理器能夠隨機訪問雙空間存儲器字空間的存儲單元,且用推移指令在雙空間存儲器的字空間上能正確移動窗框.這充分證明了內存推移理論和技術的核心內容的正確性.

5 結束語

本研究成功完成了基于TQ2440 Core 2.0核心板的內存推移實驗,證實了內存空間在雙空間存儲器上推移理論和技術的正確性.在本實驗中,利用TQ2440 Core 2.0提供的21根地址線A[20∶0]構成系統的2 MB內存空間,通過內存推移理論將該內存空間自動映射到1 GB的雙空間存儲器的任意一個局部范圍,并用推移指令將該局部范圍在整個雙空間存儲器上進行移動,從而使核心板對2 MB內存空間的隨機訪問自動落實為對1 GB雙空間存儲器指定位置的隨機訪問.

本實驗的成功為內存空間推移理論奠定了可靠的實物基礎,解決了雙空間存儲器在電子計算機系統的應用過程中,受到CPU地址線寬度限制的內存空間與雙空間存儲器巨大隨機訪問字空間的對接問題,奠定了構造雙空間存儲器和實施內存推移理論的實踐基礎.相信在不久的將來,完全可以實現基于雙空間存儲器的新型電子計算機,使得CPU能夠直接隨機訪問到更大的非易失存儲空間,從而使內存和外存之間的數據復制問題不復存在.

致謝:感謝徐凌宇教授對本工作的大力支持!