定時同步信號產生電路的設計與實現

王 斐,郭江宇,李勇峰,劉 健

(北方自動控制技術研究所,太原 030006)

0 引言

定時器是接收機系統的重要組成部分,它能夠提供所需的各種主脈沖定時信號和波門定時信號。在最初的設計中,定時器大多采用純硬件的實現方法,用分立元件搭建邏輯電路,電路復雜,工作量大,可讀性差,可靠性低,根據特定的需求設計特定的電路,基本不具備通用性。近年來,以數字技術為基礎的定時器得到了飛速的發展,性能指標達到了一個新的水平。現場可編程門陣列(FPGA)器件具有容量大、運算速度快、靈活可變等優點,使得許多復雜電路有了新的實現途徑,越來越被廣泛地應用于實際系統中[1]。因此,需要通過FPGA設計一種可以實現大量定時單元的定時芯片。

目前,對于定時電路的研究主要集中在可重構方面,所建立的電路較為復雜,難以工程實踐。吳文博[2]的碩士論文中著重強調了定時電路的重要性,同時研究了現場可編程門陣列(FPGA)在雷達定時器中的應用,并且運用基于部分可重構方法的原理及設計思想,基于已有的邏輯層面之上,把設計程序進行進一步簡化,使雷達定時器可實現局部動態再次構建。鄒仕祥[3]對于定時電路在通信網絡中的應用進行了廣泛的研究,提出了其在通信領域的應用前景以及設計實現方法,但文中并未對實現的電路進行簡化,導致工程實現方面缺少理論依據。彭兵[4]等對基于計數器的可編程定時電路進行了詳細研究,分析了實踐過程中的諸多問題,但未對相關難題進行解決。傳統的定時器大多采用純硬件的實現方法,根據特定的需求設計特定的電路,不具備通用性。而基于FPGA的定時器設計簡單,集成度高,滿足了接收機系統的工作要求,提高了定時器的工作效率和速度。

本文在分析定時器和電源功能的基礎上,完成了定時同步信號產生電路的硬件平臺搭建及調試,并編寫了FPGA及其他模塊的軟件程序,實現了該電路的全部功能。

1 設計方案

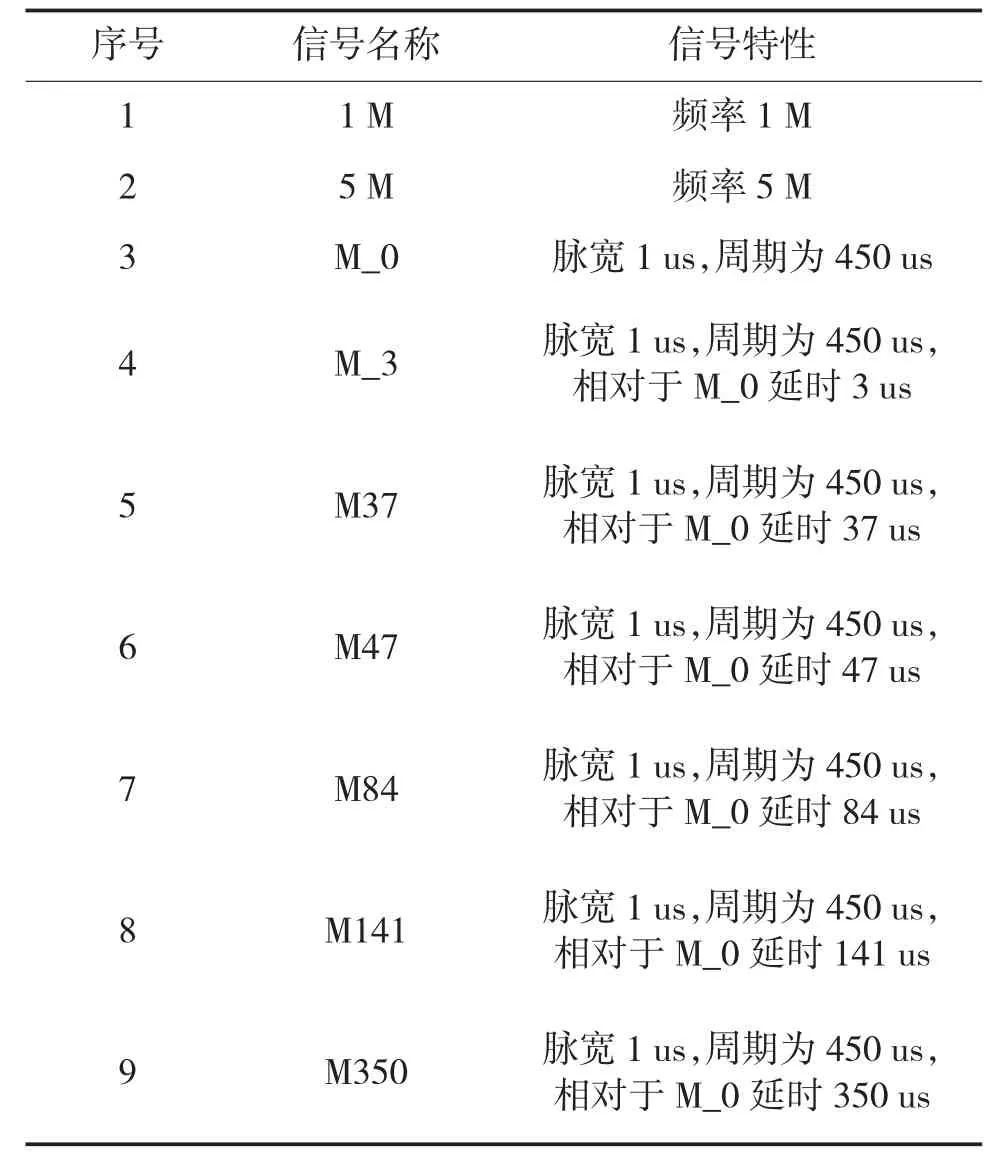

根據接收機運行環境,設計一種基于FPGA的定時器來滿足要求。定時信號板為接收機系統提供必要的定時信號輸入和頻率控制信號,以實現接收機的正常工作激勵。采用FPGA完成定時信號的生成,其中定時信號以外部晶振作為基準產生,基準信號是一個30 M時鐘信號,經過分頻產生5 M和1 M的時鐘信號。再產生一個脈寬為1 us,周期為450 us的信號,在此基礎上對信號進行超前和滯后3 us、滯后 37 us、滯后 47 us、滯后 84 us、滯后 141 us、滯后350 us等一系列的編程,最后再將程序安裝在定時信號板上,輸入一個30 M的時鐘信號以便于檢查輸出的信號是否滿足要求。在此過程中通過定時器對30 MHz時鐘信號進行分頻和延時等操作產生需要的各種信號如表1所示。

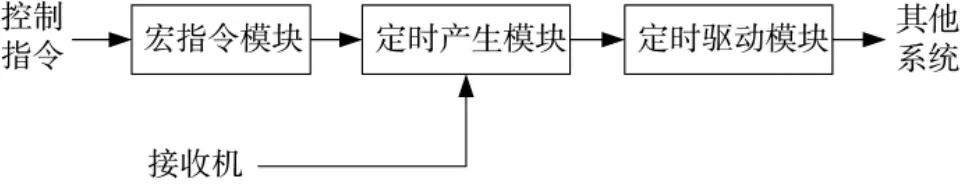

定時同步信號產生電路包括宏指令模塊、定時產生模塊、定時驅動模塊等部分。宏指令模塊通過網絡或快速通信接口接收指令,并送往定時產生模塊。定時產生模塊采用FPGA構成核心的時序產生電路,可方便地對定時時序進行修改調試,產生各路定時信號,送往定時驅動模塊,該模塊根據各分系統的要求,將各路定時信號以不同的信號形式(如TTL、RS-422等)送往各分系統,這部分電路將留有冗余通道備用,并具有對送往不同分系統的信號延時進行補償的功能,原理框圖如圖1所示。

圖1 定時同步信號產生電路原理

經過分頻和延時輸出的各種信號會送到芯片上進行檢驗,最后輸出頻率或者輸出定時信號。用定時信號控制繼電口的開關,從而輸出符合要求的信號。

表1 所需信號表

2 硬件設計

2.1 電路整體設計原理

定時信號以硬件外部晶振作為基準產生,其中基準信號是一個30 M時鐘信號。硬件采用Altera公司EP1K系列的FPGA為數字平臺,利用模塊化設計和Verilog語言在FPGA中設計進行分頻和延時,將30 M時鐘信號,經過分頻產生1 M和5 M的時鐘信號。再產生一個脈寬為1 us,周期為450 us的信號,在此基礎上對信號進行超前和滯后3 us、滯后37us、滯后 47us、滯后 84us、滯后 141 us、滯后 350 us等一系列的編程。

經過分頻和延時產生的各種信號輸入到芯片中,在芯片中進行一系列的處理,檢驗輸入的信號是否符合要求,如果符合要求則輸出信號以供使用,其原理如下頁圖2所示。

2.2 定時器模塊設計

定時器模塊設計采用大容量FPGA,盡可能在FPGA內部實現所有功能,減少外圍器件,以達到統一板級設計、提高定時精度及可靠性、降低成本、實現硬件的靈活配置的目的。

定時器的時序電路設計主要分為主脈沖定時信號的時序電路設計和波門定時信號的時序電路設計兩大部分[5]。產生主脈沖定時信號的時序電路,利用接收機的時鐘,產生重頻的方波、發射主脈沖、移相主脈沖等各種主脈沖導前或滯后信號。產生波門定時信號的時序電路則是根據距離碼產生正常波門、移相波門、波門導前或滯后信號。移相主脈沖定時信號和移相波門定時信號只要分別將產生的正常主脈沖定時信號和正常波門定時信號移相半個周期即可得到。

FPGA具有可重復編程性,可以通過硬件電路的方式實現定時器功能,同時FPGA可以方便地進行調試和仿真[6]。在此設計中選用的FPGA型號是Altera公司的EP1K50TC144,該芯片功能強大,滿足本設計的需求。

圖2 硬件設計原理

2.3 分頻模塊設計

分頻器是FPGA設計中使用頻率非常高的基本設計之一,盡管在目前大部分設計中,廣泛使用芯片廠集成的鎖相環資源。但是在對于時鐘要求不高的設計中,自行設計所需的分頻器能夠達到更好的應用效果。

首先,這種方法可以節省芯片內部的鎖相環資源;再者,可以控制FPGA中邏輯單元的使用情況。在具體的設計中,由于外部時鐘的關系,常常需要對時鐘進行分頻,因此,根據實際情況會需要進行偶數分頻、奇數分頻、半整數分頻和小數分頻等不同形式的時鐘分頻,有時要求等占空比,有時要求非等占空比[7]。

2.4 延時模塊設計

本文是利用FPGA中計數器模塊來實現周期的延時功能,采用對一個已知頻率的基準方波信號進行計數的方法實現時間的延時[8]。利用FPGA技術首先是從整體系統設計入手,經詳細地規劃后,完成控制系統行為方面的設計,并使用完全獨立于具體物理結構的用戶接口來表達功能模塊。

在確定了實現產生延時時間的方法以后,實際上,整個電路的延時過程就計數器的計數過程,也就是說,當計數器計數結束后其延時時間過程也隨之結束。顯然,當觸發信號到來時,計數器開始工作,當一個計數延時過程結束以后,為不影響下一個延時過程的開始,要求在前一個計數過程結束時,必須做好下一步的延時準備工作。

2.5 頻率控制模塊設計

經過分頻和延時產生的各種信號輸入到芯片中,在芯片中進行一系列的處理,檢驗輸入的信號是否符合要求,如果符合要求則輸出信號以供使用。

本文采用STM32F417。具體參數如下[9]:內核:ARM 32位的Cortex-M3 CPU,最高72 MHz工作頻率,在存儲器的等待周期訪問時可達1.25DMips/MHz,單周期乘法和硬件除法。存儲器:從64 K或128 K字節的閃存程序存儲器,高達20 K字節的SRAM。時鐘、復位和電源管理:2.0 V~3.6 V供電和I/O引腳,上電/斷電復位、可編程電壓檢測器,4 MHz~16 MHz晶體振蕩器,內嵌經出廠調校的8 MHz的RC振蕩器,內嵌帶校準的40 kHz的RC振蕩器,產生CPU時鐘的PLL。低功耗:睡眠、停機和待機模式。調試模式:串行單線調試和JTAG接口。多達7個定時器:3個16位定時器,每個定時器有多達4個用于輸入捕獲/輸出比較/PWM或脈沖計數的通道和增量編碼器輸入,1個16位帶死區控制和緊急剎車,用于電機控制的PWM的高級控制定時器,2個看門狗定時器,系統時間定時器:24位自減型計數器。CRC計算單元,96位的芯片唯一代碼。

2.6 電路及接口設計

在串行通訊時,要求通訊都采用一個標準接口,使不同的設備可以方便地連接起來進行通訊。RS-232是目前最常用的一種串行通訊接口。RS-232總線標準設有25條信號線,包括一個主通道和一個輔助通道。在本設計中,利用RS-232實現芯片接收上位機控制單元信號。

在與上位機進行通信時,相對于RS-232,網絡通信模塊通信容量更大,通信速度更快,同時也利用網絡通信模塊與上位機進行通信[10]。

3 軟件編程

3.1 分頻模塊編程

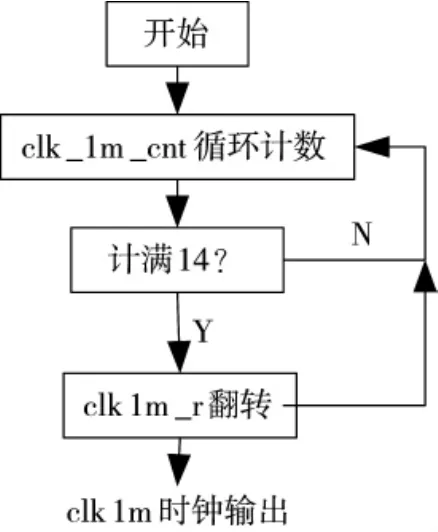

輸入的信號是一個30 MHz的時鐘信號,需要輸出一個1 MHz和一個5 MHz的時鐘信號,要產生兩種信號就需要通過分頻來實現,其流程圖如下頁圖3和圖4所示。

圖3 5M時鐘產生流程

圖4 1M時鐘產生流程

圖3為5 MHz計數器的循環計數,當計數未滿2時,繼續循環計數,當計數滿2時,時鐘翻轉。圖4為1 MHz計數器的循環計數,當計數未滿14時,繼續循環計數,當計數滿14時,時鐘翻轉。

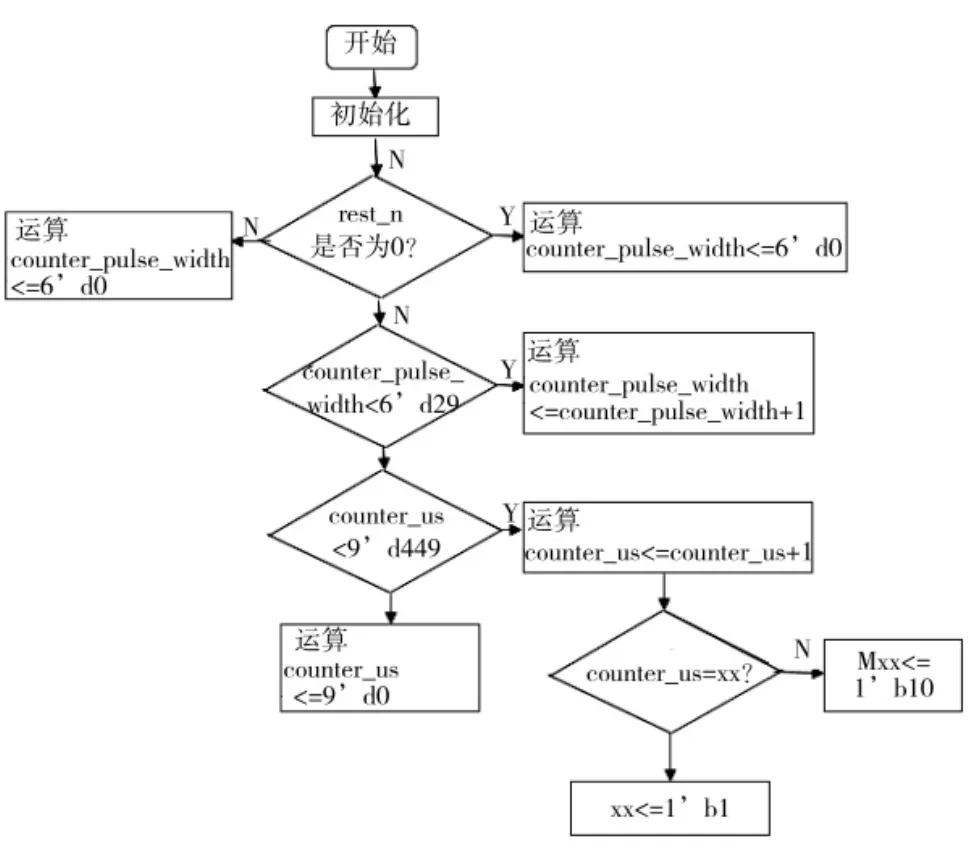

3.2 延時模塊編程

在30 MHz時鐘信號下生成基準信號,需要計數30次才能達到1 us的寬度。在生成脈寬為1 us、周期為450 us的基準信號后,需要對這個基準信號進行延時處理,以生成所需要的其他信號。其中M_0是生成的基準信號,M_3是基準信號延時3 us,M37是在基準信號上延時37 us,M47是在基準信號上延時47 us,M84是在基準信號上延時84 us,M141是在基準信號上延時141 us,M350是在基準信號上延時350 us,如圖5所示。

初始化后,低電平復位,沒有復位進行計數,對信號進行分頻,先得到1 us的時鐘信號,再進行計數一個周期450 us,然后進行延時處理,其中XX是延遲時間,如果延時3 us,則XX=3。

3.3 波形的實現

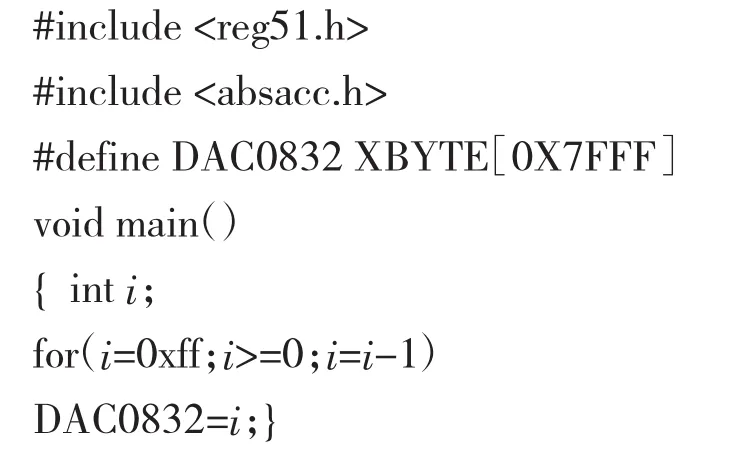

模擬定時器的的兩路觸發脈沖需要DAC0832芯片轉化后經過放大器的放大倒相后才能實現。若讓DAC0832芯片輸出電壓是脈沖電壓,需讓單片機從P0.0~P0.7引腳端輸出不斷增大或減小的數據即可。因此,可以采用由“ABSACC.H”頭文件所定義的指令“XBYTE[unsigned int]”來實現對 DAC0832 的尋址。

圖5 延時信號產生流程

xval=XBYTE[0X000F];//將地址“0x000F”中的數據取出送給xval。

XBYTE[0X000F]=0xA8;//將數據“0xA8”送入地址“0x000F”。

為得到有一定時間間隔的脈沖信號,可在讓單片機從P0.0~P0.7引腳端輸出不斷增大或減小的數據之前或之后設置一段時間延遲。用C語言編寫的輸出波形主要程序為:

偏流脈沖信號由單片機本身產生,在編程過程中,只需在輸入/輸出口的電平設置為0或1(高電平電壓的地址為0xff,低電平地址為0xfe,然后在經過放大器放大后通過示波器顯示出來。

3.4 模擬定時器脈沖寬度的實現

模擬定時器的脈沖寬度也是通過編程實現的。信號所需的脈沖寬度在25 us和4 us~6 us左右,要求在模擬的過程中通過編程將延遲控制在這段范圍左右。

CLR A;//將A 清 0。

C;0011 MOV R7,A;//將 0送給工作寄存 R7。

INC R7;//將 R7 加 1。

CJNE R7,ox64;

若 R7 不等于 ox64(6*16+4=100);則;轉到 C:0011處執行。

根據循環條件,第03行和04行總共要執行100次(ox64=100)。所以,上述程序共消耗機器周期數:N=1+1+(1+2)*100=302。

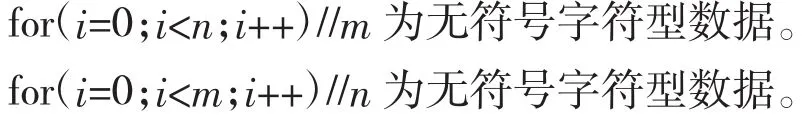

根據以上分析可知,一重循環:for(i=0;i<n;i++),所消耗的機器周期數N=3*n+2。其中N為消耗的機器周期數;n為設定的循環次數(n必須為無符號字符型數據)。在n遠大于2時,可近似為N=3*n。同理可得,二重循環程序:

所消耗的機器周期數N=3*m*n+5*m+2。在n遠大于5時,可近似N=3*m*n。

仿真過程中沒有使用編程而是采用C語言。單片機的晶振頻率為12 MHz,機器周期為1 μs。根據分析,仿真所需的延時應設置n=5左右,才能達到預期效果。非脈沖的延遲時間可適當加長。由于程序和仿真軟件的精度的原因,所實現的脈沖寬度與實際的精度還有一定差距。

最終用C語言編寫的延遲函數為:

其中,n的值決定脈沖寬度的大小。

3.5 模擬定時器脈沖幅度的實現

信號產生系統中對脈沖的幅度有很高的要求,利用編程可控制脈沖幅度在最大和最小的范圍之內變化。單片機的引腳從P0.0~P0.7端輸出不斷減小的數據,其中由最大值決定幅度的大小。設計過程當中,編程設置為最大值,即當數據開始輸出時就以5 V電壓為基準,有次序地下降。

為了達到設計所要求的-22 V的觸發脈沖信號,單純靠單片機編程很難實現,因此,在單片機外圍連接了運算放大電路,通過硬件設計來實現。運算放大器分為兩級放大,兩級的放大倍數分別為2倍~3倍。經過運算放大器放大后,基本就得到了設計所需要的電壓幅度。

4 結論

本文針對接收機系統的定時同步信號產生電路進行了設計,完成了對接收機系統運行環境的構建,主要工作可以概括為:1)確定系統的定時同步信號,同時分析各信號的作用,為接下來的電路設計和程序的編寫提供了依據;2)以ALTERA公司的FPGA為核心進行定時器的硬件設計,對關鍵模塊的設計進行詳細分析;3)在QuartusⅡ環境下采用Verilog語言進行軟件編程,實現所需信號的產生。實驗表明,本設計能夠產生相應信號,滿足設計要求,具有一定的實際應用價值。

[1]李辰.光電技術對提高高炮系統作戰能力的研究[D].長沙:國防科技大學,2006.

[2]吳文博.基于FPGA動態局部可重構技術的雷達定時器設計[D].成都:電子科技大學,2016.

[3]鄒仕祥.通信系統中大量定時器的設計與分析[J].計算機應用,2015,25(11):2715-2716.

[4]彭兵,韓克,敏韓勇.基于計數器的可編程定時電路[J].西北農林科技大學學報,2003,31(5):199-201.

[5]張巖,伍春,趙志坤.基于FPGA的多通道數據采集卡的方案設計[J].東北師大學報(自然科學版),2016,48(4):63-67.

[6]辛君君,黃松嶺,劉立力,等.基于FPGA的超多通道高速數據采集系統設計 [J].電測與儀表,2008,45(10):34-36.

[7]肖祖勝,程明.基于FPGA的數據采集分析系統設計[J].電子技術應用,2009,35(3):49-50.

[8]周潤景,圖雅,張麗敏.基于Quartus II的FPGA/CPLD數字系統設計實例[M].北京:電子工業出版社,2007.

[9]王龍,楊承志,吳宏超,等.基于FPGA的數字基帶多模雷達信號源設計[J].電子技術應用,2016,42(8):87-90.

[10]李紅剛,楊林楠,張麗蓮,等.基于FPGA的高速多通道數據采集系統的設計[J].計算機測量與控制,2016,14(10):1407-1409.