隨鉆測井儀器井下數據及信號通訊傳輸模塊設計

2018-06-19 08:28:56王秋然

西部探礦工程

2018年6期

王秋然

(大慶鉆探工程公司鉆井工程技術研究院鉆井工藝研究所,黑龍江大慶163000)

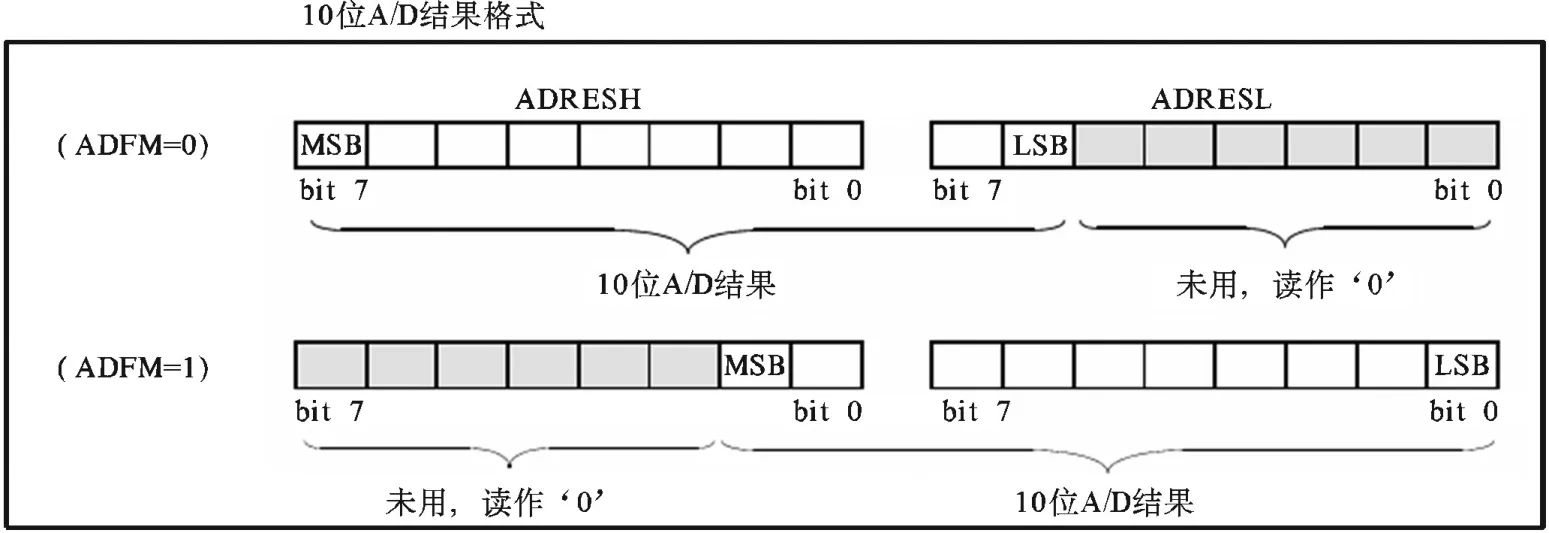

1 主控芯片D/A轉換設計要求

要求:將模擬信號轉化為數字信號,進行處理后輸出模擬信號。輸入延遲從接收模塊到邏輯模塊之間延遲為3.1ns,邏輯模塊到輸出模塊之間延遲為3.1ns。

驗證:將模擬量進行二進制展開,對應的每一位按照由低向高的順序將其加權計算后的計算值相加,所得的總模擬量就與數字量成正比,所得到的結果與數字量一一對應成比例關系。由此可以實現將數字信號轉換為模擬信號。

其中為二進制數按位權展開轉換成的十進制數值。

由此有[1]:

進一步簡化可得:

通過上式可得結論如圖1所示。

圖1 10位A/D結果格式

由此,實現D/A轉換,符合設計標準。

比較器設計要求:輸出電壓響應時間小于5ns,高電平轉低電平信號時間小于10ns,輸出電壓信號噪聲小于0.2mV。

2 計算驗證

比較器電路原理圖如2所示。

圖2 比較器電路原理

設計電路時,差分計算器選用的為PMOS管,其精度高,功耗少,在做雙路差分計算時,誤差更小。這2個信號差分前,并不一致,其中電壓較低的,其打開狀況較好,通過的電流值也更高;差分計算之后,會將輸出電壓拉高,同時反饋給輸入電路。輸入端采用的是NMOS管控制信號,分別為M9和M10,當電源電壓Vc電壓值較低時,M10的柵電壓會被拉升,M9則處于臨界開啟狀態,此時V0輸出的是高電壓信號。圖2中,柵電壓噪聲過高時,相應的電流也會升高,使用M8和M9抑制過高的電壓和電流。電路的輸……

登錄APP查看全文

猜你喜歡

鴨綠江(2021年35期)2021-04-19 12:24:18

考試與評價·高一版(2020年6期)2020-11-02 02:45:24

現代裝飾(2020年7期)2020-07-27 01:27:42

流行色(2020年1期)2020-04-28 11:16:38

中國生殖健康(2019年3期)2019-02-01 06:12:26

藝術啟蒙(2018年7期)2018-08-23 09:14:18

海峽姐妹(2017年7期)2017-07-31 19:08:17

Coco薇(2017年5期)2017-06-05 08:53:16

鑿巖機械氣動工具(2016年3期)2016-03-01 04:00:25

海軍航空大學學報(2015年3期)2015-11-11 17:20:00