高分辨率級聯電容陣列SARADC可行性分析

中星微人工智能芯片技術有限公司 楊建明 夏昌盛 張韻東

逐次逼近型ADC(SARADC)以其低功耗、高精度在無線通訊、醫療器件、通用信號測量領域獲得廣泛應用。電容陣列SARADC結構簡單,模擬主動器件極少,其內嵌DAC可復用為采樣保持電路[1]-[4],面積小功耗低。用于構成電容陣列的半導體電容元件精度有限[5],實際電容陣列SARADC可獲得的精度要低于理論精度。本文旨在分析電容匹配誤差對電容陣列SARADC精度的影響,推導出補償電容匹配誤差的方法,從而獲得高精度SARADC。

1 二進制權值電容陣列

SARADC精度會受內嵌DAC、比較器、基準電壓影響。其中DAC的精度是制約SARADC精度的主要因素。本文忽略電路其他因素,只分析SARADC內嵌的電容陣列DAC精度。

1.1 二進制權值電容陣列模型

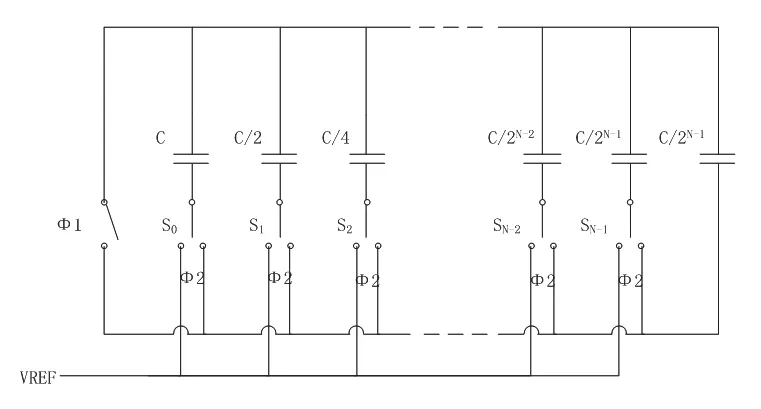

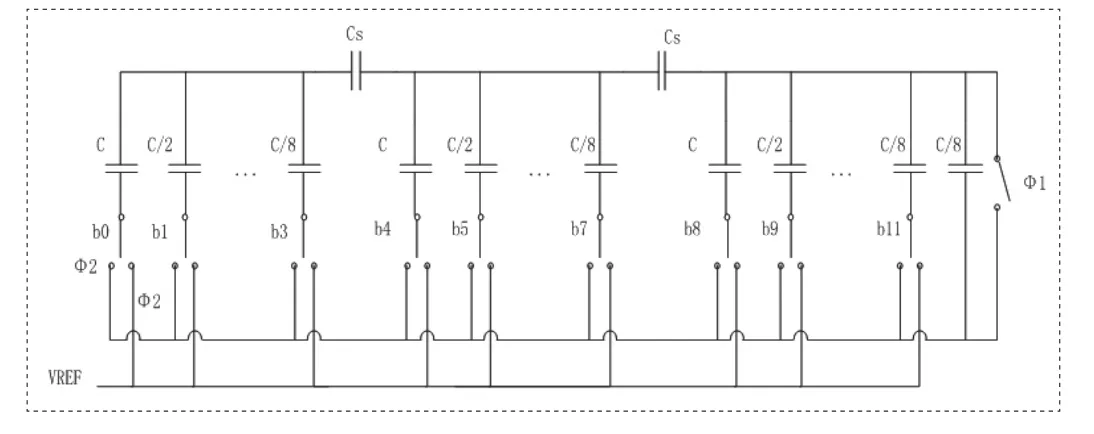

二進制權值電容陣列如圖1所示[6]-[8]。

圖1 二進制權值電容陣列Fig.1 Binary-weighted Capacitor Array

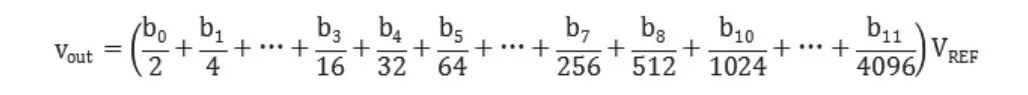

在Φ1期間,陣列所有電容的兩端都接地;Φ2期間,對應位為1的電容與VREF相連,而對應位為0的仍然接地。Φ2期間電容陣列輸出有效。

Φ2期間不存在電容陣列充放電路徑,從Φ1到Φ2期間電荷守恒。與VREF相連的電容Ceq上的電荷與總電容Ctot中的電荷相等。

1.2 INL/DNL

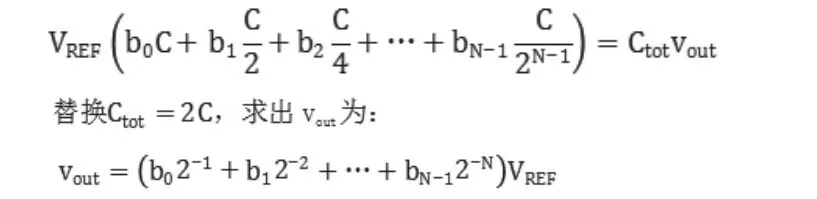

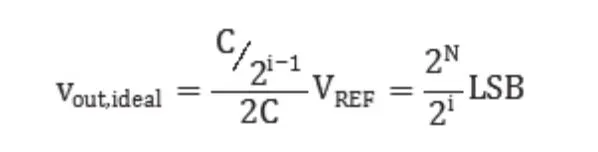

由于半導體電容元件存在匹配誤差,上式系數會偏離理想值2-i。

在最壞情況假設下推導二進制權值電容陣列的積分非線性和微分非線性。對于一個N位二進制權值電容陣列,當第i個電容只與VREF相連時,理想輸出為:

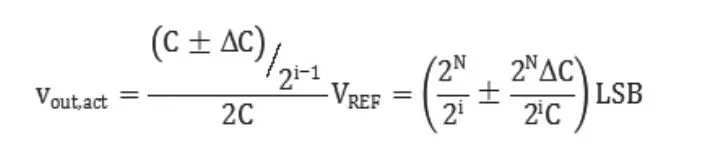

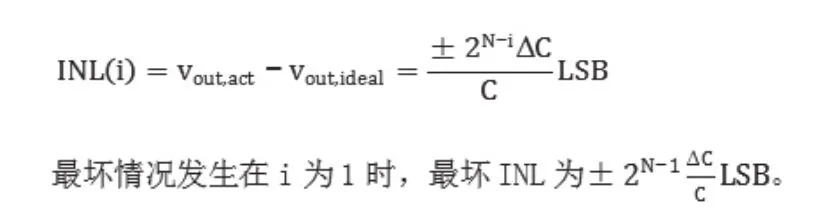

假設電容的容差為,第i個電容在實際的最壞情況下輸出為:

則第i位的INL為:

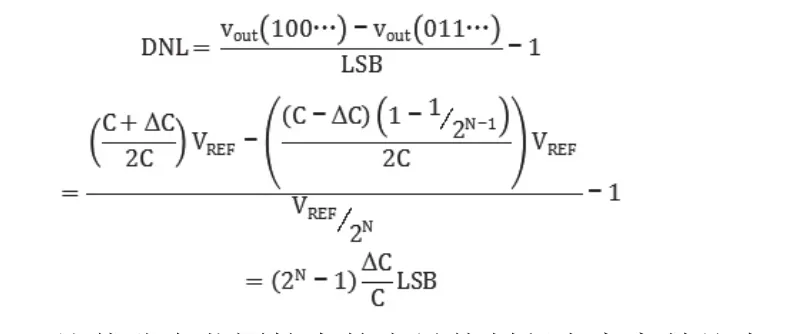

二進制權值電容陣列的最壞DNL出現在MSB變化時。最壞DNL可表示為:

比值分布范圍較大的半導體制程電容容差約為。當二進制權值電容陣列為6位時候,DNL約為0.1LSB。

2 容差與匹配

2.1 容差需求

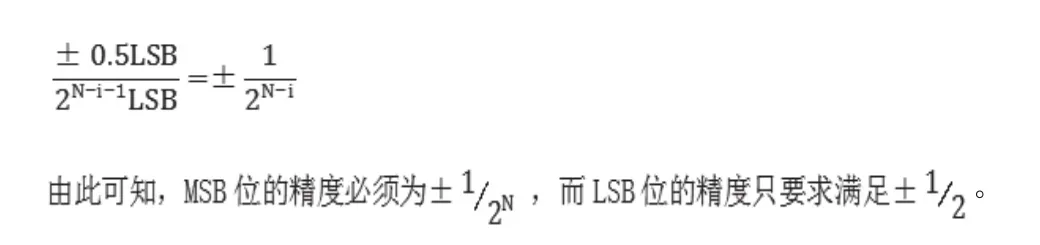

對于一個N位數據轉化器,所有位的容差都要小于。第i位的權重因子可以表示為:

第i位的精度,也就是由權重因子歸一化的容差,即為:

2.2 半導體電容匹配特性

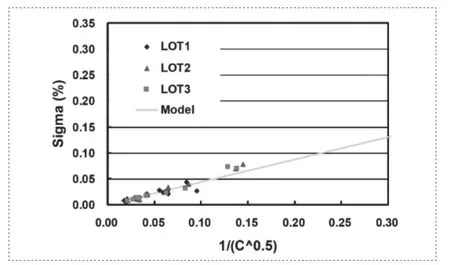

圖3為TSMC 28nm制程FMOM電容匹配測量數據。

圖2 交叉耦合電容匹配誤差Fig.2 MX-coupled capacitor mismatch

從圖2可知,電容元件的匹配精度隨著最大元件與最小元件的比值的增大而降低。考慮到電路功耗面積,最大電容取值存在上限。電容陣列權重因子范圍越大,電容間匹配差;相反電容陣列權重因子范圍越小,電容間匹配好。

高精度SARADC設計思路可以通過減小電容取值分布范圍入手。

3 分割電容陣列

分割電容陣列[12]-[15]通常被用于減小電容陣列取值范圍,提升SARADC精度,降低動態切換功耗與面積。分割電容陣列級數選取,以及分割電容本身精度要求卻很少有文章推導計算。本文側重于理論上澄清這些問題。

3.1 分割電容陣列模型

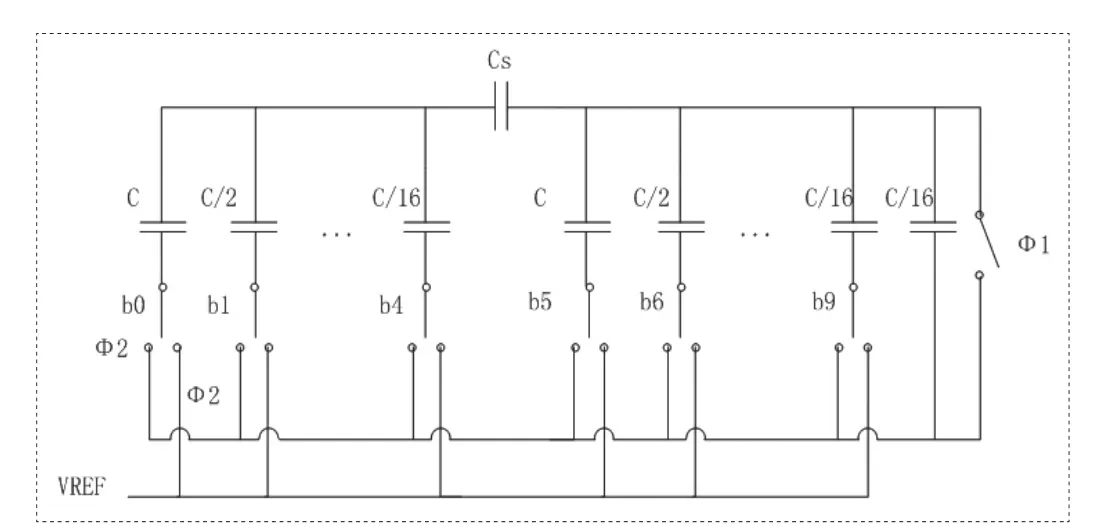

圖3 分割電容陣列Fig.3 Split Capacitor Array

基于圖2電容匹配數據,16:1電容比值范圍內電容匹配誤差小于0.1%。采用分割電容陣列(5位MSB,5位LSB)可以獲得10bit精度,如圖3所示。

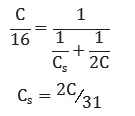

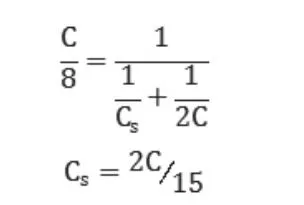

分割電容Cs和LSB陣列的串聯必須等于MSB陣列的最小權值電容。因此可得:

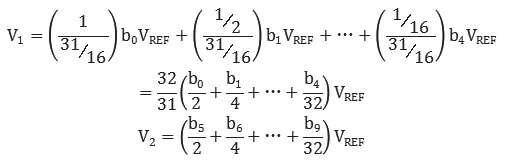

MSB陣列的戴維南等效電壓V1和LSB陣列加上終端電容的等效電壓V2如下:

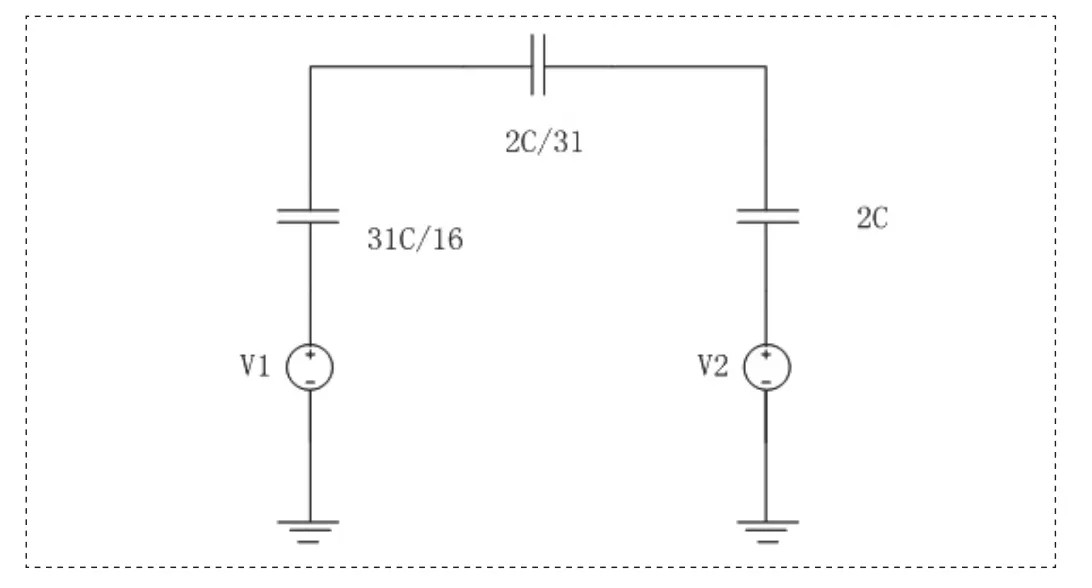

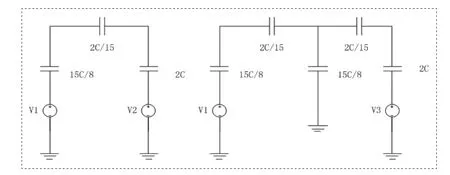

分割電容陣列二端口網絡等效電路如圖4所示:

圖4 分割電容陣列等效電路Fig.4 Split Capacitor Array Equivalent Circuit

根據此圖,理想輸出電壓為:

3.2 分割電容精度

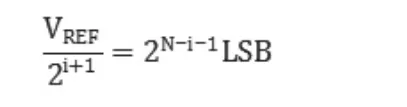

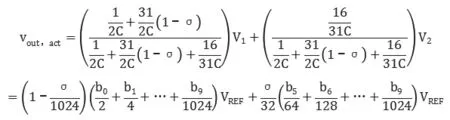

分割電容與電容陣列單位電容不構成整數比例,實際取值會有取舍。簡化計算,假設MSB/LSB電容陣列為理想電容,只考慮分割電容取值誤差帶來的影響。根據圖4,并用泰勒級數展開只保留1次項,輸出電壓為:

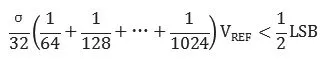

分割電容容差會產生很小的增益誤差與LSB陣列權值誤差。當LSB位從全零跳變到全1時誤差最大,此時對應最壞情況DNL:

推導出只要滿足,最終電容陣列轉換精度即可以滿足DNL<1/2 LSB。

3.3 級聯分割電容陣列

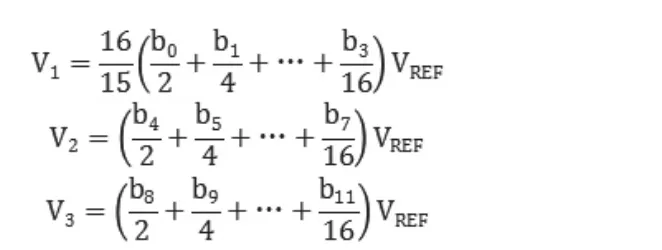

圖3所示分割電容陣列可獲得10位精度。如果需要更高精度,需要進一步減小電容陣列取值范圍,提升電容匹配精度。可以在原分割電容陣列基礎上級聯分割電容陣列,如圖5所示:

圖5 級聯分割電容陣列Fig.5 Cascaded Split Capacitor Array

分割電容Cs和LSB陣列的串聯必須等于高位電容陣列的最小權值電容。因此可得:

高位陣列的二端口戴維南等效電壓V1,2和LSB陣列加上終端電容的等效電壓V3如下:

級聯分割電容陣列兩端口網絡等效電路如圖6所示:

圖6 分割電容陣列等效電路Fig.6 Split Capacitor Array Equivalent Circuit

圖6 左側等效電路對應于LSB陣列輸入信號全零;右側等效電路對應于中間級陣列輸入信號全零。根據疊加原理,輸出信號為:

即為12位電容陣列輸出電壓表達式。

4 驗證

本文觀點通過Matlab驗證了數學模型的可行性,同時基于TSMC28nm制程,通過Spice仿真工具驗證12bit SARADC電路,結果與數學模型吻合。

5 結論

本文分析了SARADC核心部件電容陣列DAC等效模型及電容容差對電容陣列精度的影響。提出提升SARADC精度的方法。同時,推導出分割電容自身取值精度要求。本文認為,結合半導體制程電容匹配特性,減小電容陣列電容比值分布范圍,提升電容間匹配精度,結合級聯分割電容陣列架構,設計上可以獲得高精度SARADC。

[1]M.D.Scott,B.E.Boser,and K.S.J.Pister.An ultra low-energy ADC for smart dust[J].IEEE J.Solid-State Circuits,vol.38,no.7,pp.1123-1129,Jul.2003.

[2]N.Verma and A.P.Chandrakasan.An ultra low energy 12-bit rateresolution scalable SAR ADC for wireless sensor node[J].IEEE J.Solid-State Circuits,vol.42,no.6,pp.1196-1205,Jun.2007.

[3]S.Gambini and J.Rabaey.Low-power successive approximation converter with 0.5 supply in 90 nm CMOS[J].IEEE J.Solid-State Circuits,vol.42,no.11,pp.2348-2356,Nov.2007.

[4]J.Sauerbrey,D.Schmitt-Landsiedel,and R.Thewes.A 0.5V 1uW successive approximation ADC[J].IEEE J.Solid-State Circuits,vol.38,no.7,pp.1261-1265,Jul.2003.

[5]P.R.Gray,P.J.Hurst,R.G.Meyer.Analysis and Design of Analog Integrated Circuits[M].John Wiley & Sons,INC.2008

[6]E.Suarez,P.R.Gray,and D.A.Hodges.All-MOS charge redistribution analog-to-digital conversion techniques—Part I[J].IEEE J.Solid-State Circuits,vol.SC-10,no.6,pp.371-379,Dec.1975.

[7]H.Hong and G.Lee.A 65fJ/conversion-step 0.9-V 200-kS/s rail-torail 8-bit successive approximation ADC[J].IEEE J.Solid-State Circuits,vol.42,no.10,pp.2161-2168,Jul.2007.

[8]R.R.Singh et al.Multi-step binary-weighted capacitive digital-toanalog converter architecture[J].in Proc.IEEE MWSCAS,Aug.2008,pp.470-473.

[9]R.J.Baker,CMOS Circuit Design,Layout,and Simulation,2nd ed[M].New York:Wiley,2004.

[10]E.Culurciello and A.G.Andreou.An 8-bit 800-uW 1.23-MS/s successive approximationADCin SOI[J].IEEE Trans.Circuits Syst.II,Exp.Briefs,vol.53,no.9,pp.858-861,Sep.2006.

[11]Y.Zhu et al.A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS[J].IEEE J.Solid-State Circuits,vol.45,no.6,pp.1111-1121,Jun.2010.

[12]Y.Zhu,U.Chio,H.Wei,S.Sin,S.U,and R.P.Martins,A powerefficient capacitor structure for high-speed charge recycling SAR ADCs[J].in Proc.IEEE ICECS.,Sep.2008,pp.642-645.