基于FPGA的四軸飛行器飛行控制系統設計

徐亞妮 羅文廣 張亮

摘 要:為提高四軸飛行器飛行控制系統的穩定性及安全性,研制了一種基于NIOS II的飛行控制系統,并添加了多冗余控制功能.當其中一套系統失效的情況下,調用多個NIOS II軟核,配合Altera自帶的IP核以及外圍硬件電路,其他的冗余模塊能夠替換壞掉的模塊繼續工作,防止發生飛行故障,從而提高四軸飛行器的穩定性和安全性.同時針對四軸飛行器易受外界干擾的問題,設計了四軸飛行器的自抗擾控制算法,并和串級PID控制器的控制效果進行了比較.仿真結果表明:所設計的自抗擾控制算法可以更好地實現四軸飛行器的姿態控制,并具有較強的魯棒性.

關鍵詞:四軸飛行器;飛行控制系統;FPGA

中圖分類號:TP273 DOI:10.16375/j.cnki.cn45-1395/t.2018.03.008

0 引言

近年來,四軸飛行器在各行業得到廣泛應用,飛行器的可靠性顯得尤為重要,而飛行控制系統(簡稱飛控)是飛行器的控制核心,其性能直接決定了無人機飛行性能及完成任務的效率.研究并設計具有更高數據處理、更低的功耗、更高的集成度的飛控是未來四軸飛行控制系統發展的方向[1],同時可編程片上系統與非傳統硬件模型——多核設計也是發展趨勢.因此優化設計飛控的性能,提高四軸飛行器飛行的穩定性及安全性具有重要的意義.

為了使四軸飛行器具有更好的穩定性,國內外學者作了廣泛的研究:文獻[2]采用PID控制方案,通過集成了紅外相機,實現精確定位.但該方案在硬件上的改進并沒有讓穩定性的提升得到較好的改善.在軟件設計方面,文獻[3]中設計了一種自適應UKF微型航姿系統,對噪聲在線估計,對噪聲的協方差進行在線更新,動靜態精度都有較大的提高,但是收斂速度比較慢.文獻[4]中作者考慮了四軸飛行器在風力干擾情況,設計了基于積分反演算法的內環姿態控制和基于 PID 的外環控制組成的雙閉環控制器,并驗證了該控制器在風力干擾下性能良好且有著較強的魯棒性.但該控制器的設計對飛行器數學模型精度要求非常高,在實際應用中很難實現.

針對上述文獻中對四軸飛行器穩定性研究的不足之處,本文將基于NIOS II的可編程片上系統多處理器技術應用在四軸飛行器上,設計了多冗余CPU的飛行控制系統.主要研究四軸飛行控制系統的硬件結構與軟件結構兩個方面.首先在硬件方面設計了四軸飛行控制器的多重冗余結構,增加了關鍵模塊的備用模塊,使其在飛行控制器上的重要模塊,如加速度傳感器,陀螺儀,羅盤,CPU等失效情況下,能夠替換故障模塊,保障飛行器結構的完整性,使四軸飛行器得以繼續正常飛行;其次是設計了一種適合在多重硬件冗余環境下的軟件結構,能夠快速識別發生故障的模塊,并及時啟用備份模塊.同時針對四旋翼飛行器參數不確定和外部干擾敏感的問題,從分析串級PID控制系統的不足出發,提出了一種基于自抗擾控制算法的四軸飛行器控制系統,彌補了串級PID控制算法中快速性與超調量之間的矛盾.并與串級PID控制系統進行定量比較分析.通過仿真實驗測試,驗證了該系統可以有效提高四軸飛行系統的穩定性與安全性.

1 飛行控制器系統硬件平臺概述

本文所設計的四軸飛行器的飛行控制系統是基于可編程片上系統技術.可編程片上系統技術是一種高效、靈活的嵌入式系統硬件解決方案,也是一種新型嵌入式技術.

可編程片上系統如圖1所示,共有4個CPU:CPU0是主CPU,接收GPS(UART接口)和nRF24L01(SPI接口)等傳感器采集的數據,并進行相關數值處理.CPU1、CPU2、CPU3是3個功能完全一樣的處理器,互為備份,只要一個CPU能正常工作,整個系統功能都不受影響,惡劣條件下工作可靠性大大增強.每個CPU接收各自姿態傳感器輸入的數據,并和CPU0處理的傳感器數據一起計算四軸飛行器的位置、高度、姿態等信息.CPU1、CPU2、CPU3處理后的結果再傳給CPU0做判斷,輸出PWM信號控制電機.

CPU之間的通信原理是:4個CPU通過NIOS II自帶的mutex模塊,互斥訪問同一塊片上存儲器來進行數據通信[5].CPU訪問存儲器前會先監測mutex模塊的標志位,確保存儲器沒被其他CPU占用,然后對存儲器進行讀寫操作.讀寫操作結束后,CPU會釋放對存儲器控制權,mutex標志位會清零.4個CPU會按照一定順序來訪問這塊共享存儲器.具體的硬件搭建如圖2所示.

2 基于可編程片上系統軟核的程序設計

2.1 NIOS II軟件設計

總體任務分為傳感器數據采集、控制算法、輸入、輸出等4部分,并把各個部分的任務按照實時性要求,分配到操作系統的進程中,即完成飛行控制器上的軟件設計.

Quartus自帶的NIOS II Software Build Tool(SBT)for Eclipse產生軟件模塊,每個CPU有2個文件包:BSP和上層軟件環境[6].BSP提供訪問硬件底層的接口函數,自動運行來實現上層軟件所要求的功能.多核處理,需要調度mutex來實現多CPU互斥訪問共享部分存儲器,這部分可以調用NIOS II底層相關函數.

基于可編程片上系統技術的軟件設計是在IP核所搭建的硬件平臺上采用C語言或者C++語言而實現目標功能的開發過程,本設計在硬件基礎上實現的數據存儲、數據顯示等功能是基于NIOS II開發平臺下完成的.

2.2 四軸飛行器控制算法

2.2.1自抗擾控制算法

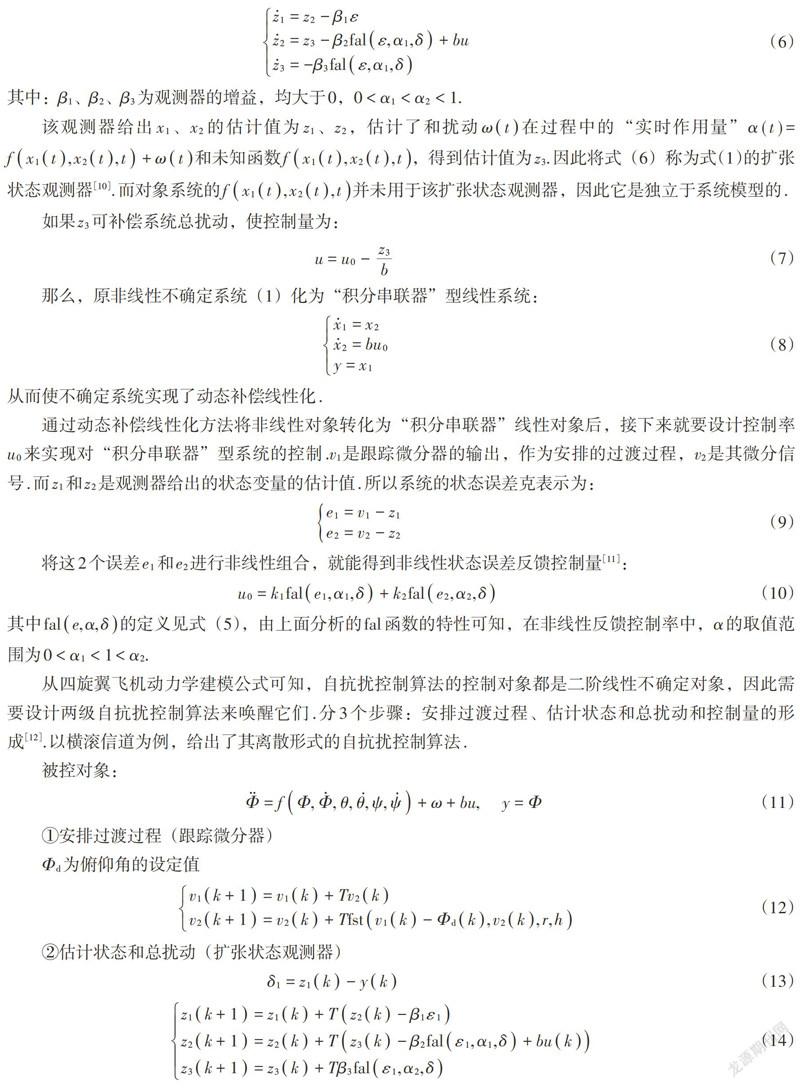

由四軸飛行器動力學建模公式可知,自抗擾控制算法的控制對象均為二階線性不確定對象,因此需要設計二階自抗擾控制算法對其進行控制.自抗擾控制器分為微分跟蹤器、擴張狀態觀測器、非線性狀態誤差反饋控制器[7].

對于一個二階不確定系統:

2.2.2 串級PID控制器

串級PID比經典PID控制性能更好更穩定.四軸飛行器的飛行過程干擾因素多,實時性要求高且無法建立精準數學模型.如突遇外力干擾,在PID控制器只用單環的情況下,因為磁力傳感器以及加速度傳感器采集的數據不準確,所以被姿態解算出來的歐拉角不精確,系統不穩定.因此在控制器中加入角速度內環,如圖4所示.陀螺儀反映靈敏,抗干擾能力強,且采集輸出角速度變化靈敏,一般不會受外界影響.同理,在當高度環中引入z軸加速度環可以有效避免外界對氣壓傳感器的干擾,增強了系統的魯棒性[13].

本設計中roll與pitch采用串級PID控制器控制角度變化,以提高飛行器的平衡能力,而yaw直接用傳統PID控制器控制即可,過程控制如圖5所示.

3 實驗測試

3.1 可編程片上系統飛行控制器系統仿真測試

NIOS II SBT for eclipse支持調用ModelSim來仿真,但一次只能仿真一個軟件包,相當于仿真一個CPU的軟硬件程序.軟件編譯通過后,點擊軟件工程右鍵RUN AS選擇NIOS II ModelSim,即可以進行仿真,調出各個CPU控制和數據總線上的信號,可以看出CPU1、CPU2、CPU3都已經工作了.

NIOS II SBT for eclipse支持在線調試,可以配合FPGA芯片進行聯調.采用基于Altera EP4S15C8型號FPGA芯片的板卡,在SBT窗口底部console可以看CPU工作的打印信息,如圖6所示,可以看出CPU通過mutex互斥訪問共享memory,CPU得到mutex權限,就會有一條打印信息.

上述板卡信息表明,3個冗余CPU都可以正常工作,可以訪問主CPU,達到了設計安全性更高的多冗余CPU飛行控制器系統的目的.

3.2 飛行控制算法仿真及實驗結果

自抗擾控制算法主要部分均用S-Function模塊編輯程序實現如圖7所示,比較部分如圖8所示.

模型建立好后,期望值按照表1設定為常數,如模型所示,PID參數3個通道全部先采用第一部分中姿態控制模塊中設置的參數,再將期望值換成階躍信號和脈沖信號,仿真驗證,如圖9所示.

圖9的波形圖中,上面的波形是自抗擾控制算法的控制效果圖,下面的波形是串級PID控制算法的控制效果圖.可以看出,在不同的信號下,自抗擾控制算法下的四旋翼飛行器俯仰角達到期望值的時間較短且超調較小,所以自抗擾控制算法針對四軸飛行器飛行姿態角的控制穩定性要優于串級PID的控制效果.

4 結束語

基于FPGA四軸飛行器的多冗余飛行控制系統采用嵌入式設計方案以及模塊化管理的思想,進一步提高整個飛行控制器系統的集成度、靈活性和數據處理能力,以及四軸飛行器的整體性能.本文在設計完成四軸飛行器硬件系統與軟件系統之后,通過板卡信息可以看出,3個冗余CPU都可以正常工作,可以訪問主CPU,達到了設計安全性更高的多冗余CPU飛行控制器系統的目的.通過自抗擾控制算法與串級PID控制器進行仿真實驗相比較后發現,自抗擾控制算法應用于飛行控制系統的穩定性更好,魯棒性更強.

參考文獻

[1]鐘佳朋.四旋翼無人機的導航與控制[D].哈爾濱:哈爾濱工業大學,2010.

[2]面向橋梁檢測的四旋翼飛行器控制系統研究[D].重慶:重慶交通大學,2013.

[3]劉宇,劉瓊,周帆,等.基于自適應UKF微型航姿系統噪聲在線估計[J].重慶郵電大學學報(自然科學版),2016,28(3):285-290.

[4]何勇靈,陳彥民,周岷峰.四旋翼飛行器在風場擾動下的建模與控制[J].中國慣性技術學報,2013,21(5):624-630.

[5]段國強,張岳軍,李衍杰,等.四旋翼無人直升機控制算法仿真比較研究[J].計算機仿真,2014,31(4):78-82.

[6]韓京清.自抗擾控制技術[M].北京:國防工業出版社,2008(1):25-32.

[7]賴愛芳,郭毓,鄭立君.航天器姿態機動及穩定的自抗擾控制[J].控制理論與應用,2012,29(3):401-407.

[8]李堯.四旋翼飛行器控制系統設計[D].大連:大連理工大學,2013.

[9]黃依新.四旋翼飛行器姿態控制方法研究[D].成都:西南交通大學,2014.

[10]陸偉男,蔡啟仲,李剛,等.基于四軸飛行器的雙閉環PID控制[J].科學技術與工程,2014,14(33):127-131.

[11]劉偉.四旋翼無人飛行器設計與實驗研究[D].哈爾濱:哈爾濱工程大學,2011.

[12]李克儉,李洋,柯寶中,等.基于FPGA的尋址與運算操作數存儲IP核設計[J].廣西科技大學學報,2017,28(4):72-79.

[13]柯寶中,侯麗,潘紹明,等.與8位微處理器系統連接的計數器IP核的設計[J].廣西科技大學學報,2017,28(2):48-54.