基于Artix?7FPGA的異步高速串行通信IP設計

王蕾 韓立峰

摘 要: 設計一種基于Artix?7 FPGA的異步高速串行通信IP核,包含協議解析和抗干擾設計、跨時鐘域緩沖區設計、用戶接口和物理層接口設計,實現最小硬件系統。該IP核可結合高速串口驅動芯片簡單對接至主流處理器,如DSP,ARM,PowerPC等,以擴展處理器的異步串行通信接口數量和通信速率。其中,通信速率最高可至30 Mb/s,擴展數量視FPGA內部資源而定,理論上無上限。在機載和地面設備中可廣泛應用。

關鍵詞: 高速率通信; 異步串行通信; DSP; ARM; Artix?7; 處理器

中圖分類號: TN919.6?34 文獻標識碼: A 文章編號: 1004?373X(2018)19?0006?05

Abstract: An asynchronous high?speed serial communication IP core based on Artix?7 FPGA was designed, for which the protocol analysis, anti?jamming capability, clock crossing domain buffer, user interface and physical layer interface are designed to realize the minimum hardware system. The IP core combined with high?speed serial driving chip can simply connect to the mainstream processors such as DSP, ARM and PowerPC to increase the extension quantity of asynchronous serial communication interface and improve the communication rate. The maximum communication rate can reach up to 30 Mb/s, and the extension quantity is determined by the internal resource of FPGA and has no upper limit theoretically. This IP core can be widely used in airborne and ground equipments.

Keywords: high?speed communication; asynchronous serial communication; DSP; ARM; Artix?7; processor

0 引 言

通用異步收發器(Universal Asynchronous Receiver/Transmitter,UART)包括RS 232,RS 499,RS 423,RS 422和RS 485等總線標準規范。UART協議作為一種串行通信協議,廣泛應用于通信、語音、圖像、儀器儀表、軍事域等各種場合,具有電路結構可靠、通信接口簡單、傳輸距離遠等特點。隨著硬件處理能力的提升和通信技術的快速發展,無線信道上的數據速率和帶寬也穩步提升。簡單的UART協議在集成度較高的處理器標配外設平臺上通信速率較低,不能滿足高速率數據接口和多源接入的要求。

本文設計的異步高速串行通信IP繼承UART傳統優點并進行改進設計。基于Xilinx公司的Artix?7 FPGA芯片進行實現,并成功應用于某型地空通信電臺數據輸入輸出接口。按照RS 422電平標準通過硬件平臺測試后,通信距離可達10 m,通信速率可達30 Mb/s。異步高速串行通信IP具有高可靠通信速率、容量可擴展的數據緩沖區、便于多目例化實現等優點,在軍事裝備領域具有廣泛的應用前景。

1 軟件協議

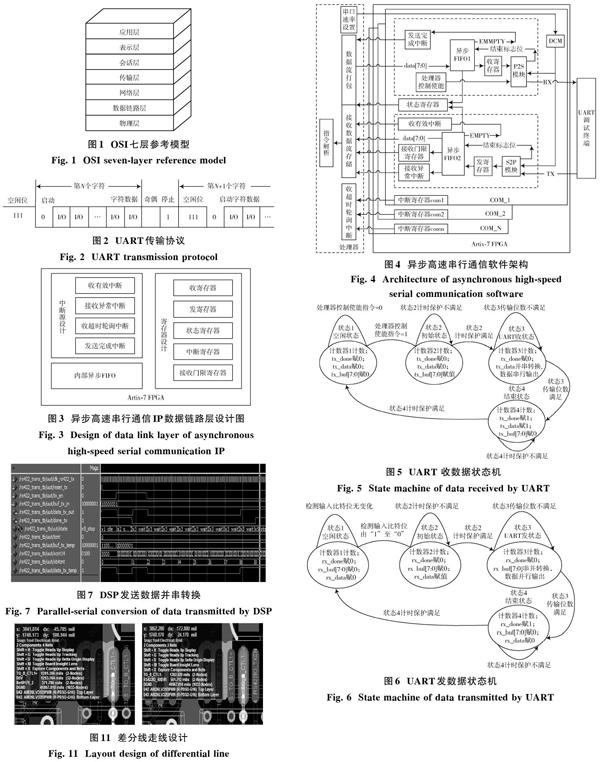

開放式系統互連參考模型(OSI)描述了計算機網絡通信的基本框架,其采用分層的結構體系,模型如圖1所示。它作為一個概念性框架規定了各層次位置和提供的服務,協調和組織各層協議的制定和執行,滿足開放系統環境互聯和應用可移植性[1]。通信協議設計時可參考OSI模型,根據系統信息交換問題分解到一系列可控的軟硬件模塊層中,各層進行獨立修改和功能擴充。本文設計的異步高速串行通信IP根據應用場景,需要應用物理層和數據鏈路層協同通信,物理層利用硬件傳輸介質為數據鏈路層提供物理連接。數據鏈路層負責將數據分幀,處理流控制。

1.1 物理層設計

異步高速串行通信IP采用UART起止式異步協議。基本的UART通信需要4條信號線: 接收端RXD±和發送端TXD±。UART數據發送和接收的幀格式: 第一位為起始位,置“0”,表示通信開始; 最后一位為停止位,置“1”,表示通信結束。每一個字符的前面都有一位起始位:低電平,邏輯值“0”。字符本身由8 bit數據位組成,字符后面是一位校驗位,最后一位是停止位高電平,邏輯值“1”。停止位和空閑位都規定為高電平,這樣就保證起始位開始處一定有一個下降沿。傳輸時,數據的低位在前,高位在后。字符之間沒有固定的時間間隔要求[2]。其格式如圖2所示。協議分析:異步通信按字符傳輸,每傳輸一個字符,就用起始位通知收方,以此來重新核對收發雙方同步,從而避免由于接收設備和發送設備之間的時鐘頻率偏差累積而導致的錯位,加之字符間的空閑位也為這種偏差提供一種緩沖,所以起止式異步協議具有較高的傳輸可靠性[3]。

1.2 數據鏈路層設計

本文設計的異步高速串行通信IP采用中斷源與外部處理器進行通信;內部設計寄存器用作狀態和數據存儲;數據收發時使用異步FIFO,保證外部處理器和Artix?7 FPGA之間實現跨時鐘域正常通信,具體數據鏈路層設計如圖3所示。

其中,中斷源設計如下:

處理器收超時輪詢中斷:在多串口多中斷情況下處理器內部對每個中斷源輪詢查找,按優先級別控制執行中斷執行源;處理器收有效中斷:通知處理器接收數據;處理器接收異常中斷:對中斷異常情況處理,保證系統接收穩健性;處理器發送完成中斷:通知處理器整包解析發送完成,可進入下一次發送狀態。

寄存器設計如下:

UART發寄存器:存儲需要串并轉換的字節數據;UART收寄存器:存儲需要并串轉換的字節數據;UART狀態寄存器:將異步FIFO狀態的輸出按位組合為狀態寄存器發送至處理器進行狀態判斷;中斷寄存器:高低電平轉換控制具體串口中斷發生;處理器接收門限寄存器:異步FIFO可讀門限值,保證數據轉換完整,可正確地按序讀取,提高系統運行時間[4]。

FIFO存儲深度設計:FIFO存儲深度根據系統需求設定,深度大會占用不必要的FPGA資源,深度小不能提供大容量的數據轉存[5]。

2 FPGA IP邏輯設計實現

2.1 軟件模塊

異步高速串行通信軟件架構如圖4所示。串行通信傳輸系統中多目串口例化時,設置多個中斷寄存器[1~n]輸出,控制外部處理器響應對應串口[1~n]中斷進程。處理器收超時輪詢中斷:在中斷源多的情況下,處理器內部對每個中斷源輪詢查找,根據中斷優先級別高低執行中斷進程,若等待超時即進入下個中斷源。將2個異步FIFO輸出的FULL,GROG_FULL和EMPTY,共計6個信號按位組合為狀態寄存器,傳輸給處理器進行狀態判斷執行。

數據并串轉換流程:處理器內部完成數據打包并寫入異步FIFO1中;處理器發送控制使能信號至P2S模塊,準備并串轉換;根據先進先出原則按字節存入UART收寄存器中,輸出至并串轉換P2S模塊;P2S模塊按比特位輸出至UART收通道,一個字節轉換完成。并串轉換結束標志位和異步FIFO1的EMPTY輸出同時作用控制讀取速率,直至完成整個FIFO1的讀取,一包數據解析完成,執行發送完成中斷信號。

數據串并轉換流程:UART發通道輸出至S2P模塊;S2P模塊完成串并轉換按字節輸出存儲在UART發寄存器中。串并轉換結束標志位控制寫入FIFO2的速率。接收門限寄存器中門限值的設定控制處理器讀取FIFO2的讀取起始時機。異步FIFO2的HALF_FULL有效輸出,FPGA發出收有效中斷,通知處理器進入執行接收狀態。處理器根據先入先出原則按字節讀取FIFO2中的數據。

2.2 高速波特率的實現

針對數據傳輸需求,將串口傳輸速率設為可調模式。包括三檔速率:115.2 Kb/s,1.44 Kb/s,10 Mb/s。在DSP中控制串口速率,FPGA中配置為相應的DCM核進行分頻。用不同的波特率控制串口收發。串口調試終端按協議發送、接收數據,實現通信交互[6]。

2.3 UART數據轉換

2.3.1 UART 收數據狀態機設計

UART 收狀態工作流程如圖5所示,共計4個狀態。

狀態1:空閑狀態。狀態機在收狀態前或完成后處于空閑狀態。計數器1負責計數等待;轉換結束標志(tx_done)賦0;待發送串行數據(tx_data)賦0;待轉換并行數據(tx_buf[7:0])賦0。處理器發出控制使能指令控制狀態跳轉。

狀態2:初始化狀態。tx_buf按設計的FIFO1讀取速率賦初值等待轉換。計數器2計時保護確保數據正確保存,作為狀態跳轉信號。

狀態3:UART收狀態。根據計數器3計數做并串轉換,tx_data按UART時鐘按位輸出。計數器3計時保護滿足8位比特位傳輸進入狀態跳轉。

狀態4:結束狀態。計數器4負責計數等待;完成一個并串轉換流程,狀態機復位。狀態4跳轉回狀態1,完成一次狀態機工作。

2.3.2 UART發數據狀態機設計

UART 發狀態工作流程如圖6所示,共計4個狀態。

狀態1:空閑狀態。狀態機在發狀態前或完成后處于空閑狀態。計數器1負責計數等待;轉換結束標志(rx_done)賦0;待轉換串行數據(rx_data)賦0; 待發送并行數據(rx_buf[7:0])賦0。檢測輸入比特位的電平高低跳變情況作為狀態跳轉信號。

狀態2:初始化狀態。rx_data根據UART發數據速率依次保存比特位,計數器2計時保護確保數據正確保存,作為狀態跳轉信號。

狀態3:UART發狀態。根據計數器3計數做串并轉換,rx_buf按字節輸出。計數器3計時保護滿足8位比特位轉換完成進入狀態跳轉。

狀態4:結束狀態。計數器4負責計數等待;完成一個串并轉換流程后狀態機復位。狀態4跳轉回狀態1,完成一次狀態機工作。

2.4 仿真測試結果

本文系統在ModelSim 10.1環境中進行驗證。模擬DSP發送數據并串轉換,仿真結果如圖7所示。當buf_tx_in 輸入為“10000001”時,data_tx_out按時鐘輸出“0,1,0,0,0,0,0,0,1,1”,done_tx在轉換結束后輸出“1”。

模擬串口發送數據串并轉換,仿真結果如圖8所示。當data_rx_in按時鐘輸入“0,1,1,0,1,1,1,0,1,1”,buf_ rx_out輸入為“0xBB”時,done_rx在轉換結束后輸出“1”。

3 硬件系統邏輯

3.1 硬件系統架構

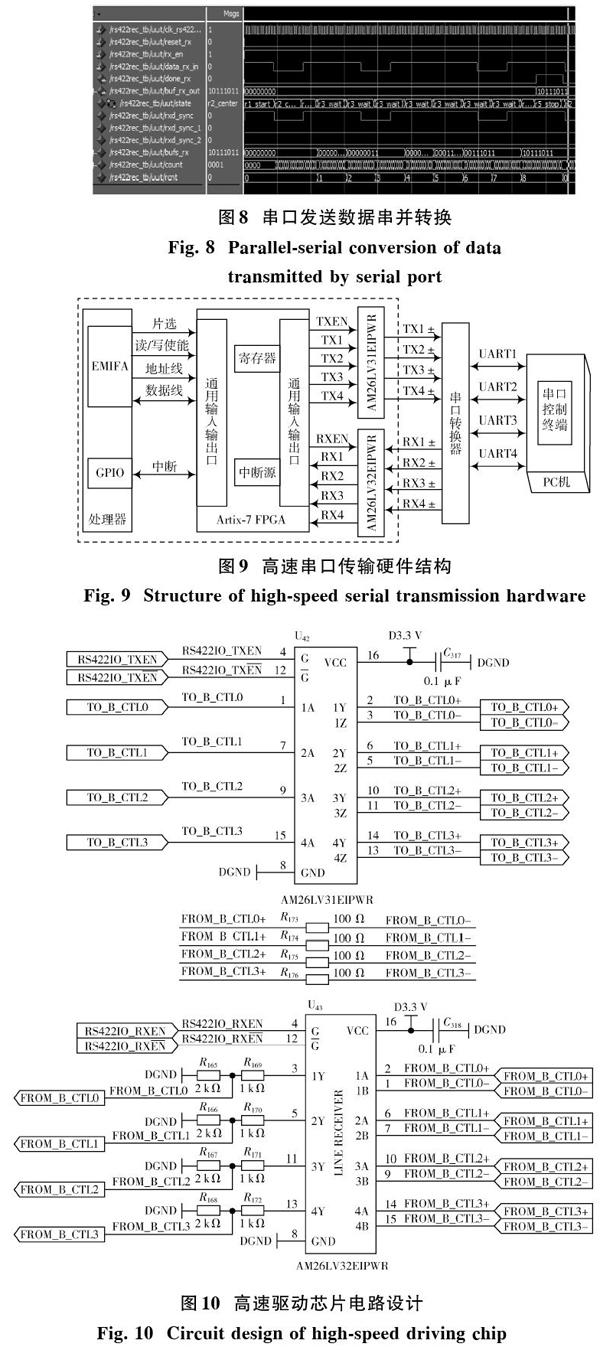

高速串口傳輸系統硬件結構系統硬件架構如圖9所示。Artix?7 FPGA使用通用輸入輸出接口與處理器的EMIFA總線接口連接,包含片選線、地址總線、數據總線、讀寫使能線等。寄存器、各種交互信息和高速通信數據都通過EMIFA總線傳輸[7]。中斷源通過通用輸入輸出接口與處理器GPIO口連接,管腳電平跳變控制中斷是否發生。處理器實現數據組包、解析、糾錯、指令控制等[8]。通過芯片使能線和4路數據線將Artix?7 FPGA與高速串口驅動芯片AM26LV31E,AM26LV32E連接。AM26LV31E支持4路RS 422數據發送單端轉差分,最高轉換速率為為32 MHz,4路共用一組使能控制線。AM26LV32E支持4路RS 422數據接收差分轉單端,最高轉換速率為32 MHz,4路共用一組使能控制線。系統使用RS 422作為平衡通信接口,經過9針D型串行接口通過串口轉換器合并連接至PC端機,并根據需求擴展串口線路數量以實現10 Mb/s的傳輸速率[9]。

3.2 差分串行總線設計

RS 422差模傳輸抗干擾能力強,理論傳輸距離為1 200 m。終端匹配采用終極電阻方法,在總線電纜遠端并接電阻100 Ω匹配電纜阻抗特性[7]。本文使用的高速驅動芯片電路設計如圖10所示。AM26LV31芯片差分輸出阻抗匹配100 Ω,AM26LV32芯片差分輸入阻抗4~17 kΩ。

在實現高速數據高可靠性傳輸時,使用差分串行抵消通信傳輸時的外部干擾。差分總線作為一個整體,外部干擾疊加在兩條差分線上后相抵消。通信電路設計完成后進行PCB設計布圖時,差分輸入輸出應考慮差分線走線等長。對PCB布圖中AM26LV31E第二通道差分輸出長度進行測量,如圖11所示:TO_B_CTRL1+長度為1 281.356 mils,TO_B_CTRL1-長度為1 282.93 mils,設計長度滿足走線需求。

3.3 硬件測試結果

PC端機中設有串口測試終端[10]。測試軟件使用C++語言編程,終端界面負責下達、數據收發檢測、實時狀態上報、誤碼率判斷等工作。測試時將發送波特率設定為10 Mb/s,驗證串口傳輸誤碼率,重復次數為10 000次時,誤碼率為0,驗證了該通信方法的可靠性。

4 結 語

本文設計的異步高速串行通信IP基于Xilinx公司的Artix?7實現,具有可編程性以及面向DSP、存儲器和連接功能支持的集成式模塊的合理組合,是Xilinx公司的成熟產品。系統應用在任務處理機硬件平臺上,經過實際測試達到10 Mb/s通信速率,滿足實時性要求高、數據量大的數字通信系統通信需求,硬件擴展性強,可靠性高,調試直觀,可廣泛應用于機載和地面設備中。

參考文獻

[1] 何亞蘭,周劉紀.基于FPGA+DSP的調頻電臺傳輸系統[J].單片機與嵌入式系統應用,2013(10):1?4.

HE Yalan, ZHOU Liuji. FM radio transmission system based on FPGA+DSP platform [J]. Application of SCM and embedded system, 2013(10): 1?4.

[2] 田佳,王一平.基于FPGA的帶CRC校驗的異步串口通信[J].現代電子技術,2010,33(20):5?7.

TIAN Jia, WANG Yiping. Asynchronous serial port communication with CRC verification based on FPGA [J]. Modern electronics technique, 2016, 33(20): 5?7.

[3] 蔡艷輝,胡銳,程鵬飛,等.一種基于FPGA+DSP的北斗兼容型高精度接收機系統設計[J].導航定位學報,2013(2):1?6.

CAI Yanhui, HU Rui, CHENG Pengfei, et al. Design of a Beidou compatible high precision receiver based on FPGA+DSP [J]. Journal of navigation and positioning, 2013(2): 1?6.

[4] 李瑩,賈彬.一種基于狀態機的串口通信協議的設計與實現[J].電子設計工程,2012,20(7):100?103.

LI Ying, JIA Bin. A serial port communication protocol based on state machine and its implementation [J]. Electronic design engineering, 2012, 20(7): 100?103.

[5] 李偉.基于FPGA的多串口通信設計與實現[J].數字技術與應用,2015(2):174?175.

LI Wei. Design and implementation of multi?serial port communication based on FPGA [J]. Digital technology and applications, 2015(2): 174?175.

[6] 胡焱.基于FPGA+DSP 的數字中頻收發機的設計[J].現代電子技術,2016,39(15):78?80.

HU Yan. Design of digital medium frequency transmitter based on FPGA+DSP [J]. Modern electronics technique, 2016, 39(15): 78?80.

[7] 王沖,汪寶祥.基于FPGA 的串行通訊接口設計[J].微處理機,2016,37(3):73?76.

WANG Chong, WANG Baoxiang. Design of serial communication interface based on FPGA [J]. Microprocessors, 2016, 37(3): 73?76.

[8] 王斌,張林,鄧軍,等.一種基于高速串口通信的高效數據處理方法[J].自動化技術與應用,2016,35(6):57?60.

WANG Bin, ZHANG Lin, DENG Jun, et al. A high efficiency data processing method based on high?speed serial port communication [J]. Technology of automation and applications, 2016, 35(6): 57?60.

[9] 桂江華,邵健,潘邈.一種高可靠串行通信協議[J].電子與封裝,2016,16(2):40?43.

GUI Jianghua, SHAO Jian, PAN Miao. A high reliable serial communication protocol [J]. Electronics and packaging, 2016, 16(2): 40?43.

[10] 丁毅,趙笑龍,豐偉.基于在線調試的串口通信協議測試方法[J].航空電子技術,2016,47(2):30?33.

DING Yi, ZHAO Xiaolong, FENG Wei. Test method of serial port communication protocol based on online debugging [J]. Aero?electronic technology, 2016, 47(2): 30?33.