基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng)

趙飛燕 藺勇

摘 要: 為解決傳統(tǒng)通信信號(hào)采集系統(tǒng)信號(hào)采集強(qiáng)度低的問(wèn)題,設(shè)計(jì)了基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng)。對(duì)多路并行通信信號(hào)采集模擬電路進(jìn)行優(yōu)化,降低信號(hào)采集過(guò)程中受到的干擾。結(jié)合模糊規(guī)則原理對(duì)多路通信信號(hào)采集流程進(jìn)行簡(jiǎn)化處理;利用十字交叉路口信息采集理論設(shè)計(jì)通信系統(tǒng)相位采集控制,優(yōu)化通信系統(tǒng)信號(hào)采集神經(jīng)網(wǎng)絡(luò),實(shí)現(xiàn)對(duì)多路并行的信號(hào)采集。實(shí)驗(yàn)結(jié)果證實(shí),基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng)比傳統(tǒng)系統(tǒng)的采集強(qiáng)度提高了10%以上,從而驗(yàn)證了系統(tǒng)的有效性。

關(guān)鍵字: 自適應(yīng)控制; 仿真模擬; FPGA技術(shù); 通信頻率; 信號(hào)采集; 多相位控制

中圖分類號(hào): TN911?34; U665 文獻(xiàn)標(biāo)識(shí)碼: A 文章編號(hào): 1004?373X(2018)19?0027?04

Abstract: A multi?channel parallel communication signal acquisition system based on FPGA technology was designed to improve the signal acquisition intensity of the traditional communication signal acquisition system. The analog circuit of the multi?channel parallel communication signal acquisition is optimized to reduce the interference existing in the signal acquisition process. The fuzzy rule principle is combined to simplify the acquisition process of multi?channel communication signal. The intersection information acquisition theory is used to design the phase acquisition control of the communication system, optimize the neural network for signal acquisition of the communication system, and realize the multi?channel parallel signal acquisition. The experimental results show that the signal acquisition intensity of the multi?channel parallel communication signal acquisition system based on FPGA technology is increased by 10% than that of the traditional communication signal acquisition system, which can verify the effectiveness of the proposed system.

Keywords: adaptive control; simulation; FPGA technology; communication frequency; signal acquisition; multi?phase control

0 引 言

通信信號(hào)采集系統(tǒng)在信息的傳輸和接收過(guò)程中易受到外界因素的干擾,難以保障通信信息的準(zhǔn)確采集和傳輸,一旦在多路并行的復(fù)雜路段出現(xiàn)通信問(wèn)題,易造成嚴(yán)重的交通擁堵現(xiàn)象,甚至威脅駕駛?cè)藛T的生命安全。傳統(tǒng)數(shù)據(jù)采集系統(tǒng)采取單片機(jī)來(lái)控制主要系統(tǒng)模塊,完成數(shù)據(jù)信號(hào)的采集,該系統(tǒng)速度性能相對(duì)較差,難以保障系統(tǒng)運(yùn)行的實(shí)時(shí)性[1]。隨著射頻技術(shù)、無(wú)線通信等技術(shù)的快速發(fā)展,利用FPGA技術(shù)進(jìn)行信號(hào)采集,可有效提高系統(tǒng)的工作速度和效率。因此本文設(shè)計(jì)基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng),解決當(dāng)前數(shù)據(jù)信號(hào)采集系統(tǒng)中存在的問(wèn)題。實(shí)驗(yàn)結(jié)果顯示,基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng)不僅在性能上優(yōu)于傳統(tǒng)的單片機(jī)控制采集系統(tǒng),在數(shù)據(jù)處理方面也十分強(qiáng)大,具有廣闊的應(yīng)用前景。

1 基于FPGA技術(shù)的多路并行通信系統(tǒng)設(shè)計(jì)

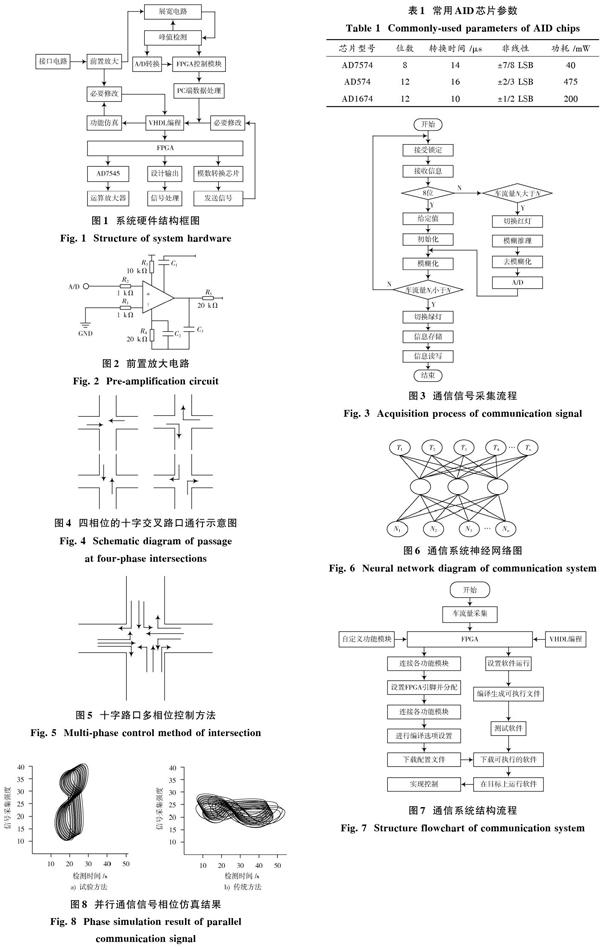

如果在信道中對(duì)發(fā)送的信息進(jìn)行有針對(duì)性的干擾,就會(huì)破壞接收信號(hào)的質(zhì)量,從而導(dǎo)致信息量減少或者中斷,破壞了通信系統(tǒng)傳輸?shù)馁|(zhì)量。借助于對(duì)被測(cè)信號(hào)在時(shí)域或變換域的特性分析,提高信號(hào)利用程度[3]。隨著DSP和FPGA技術(shù)的開(kāi)發(fā)取得了飛躍性的發(fā)展,本文使用DSP和FPGA技術(shù)設(shè)計(jì)信號(hào)采集系統(tǒng)[4],系統(tǒng)硬件結(jié)構(gòu)框圖如圖1所示。

1.1 模擬電路設(shè)計(jì)

模擬電路和數(shù)字電路是系統(tǒng)硬件電路的兩大組成部分[5]。模擬電路主要對(duì)輸入的信號(hào)進(jìn)行放大處理,包括放大器等精密儀器。處理后得到三路輸出信號(hào),其中兩路信號(hào)被輸送到數(shù)字電路系統(tǒng)作為控制信號(hào),另一路則被送到A/D轉(zhuǎn)換電路。FPGA(EPF10K20TC144?4)芯片由數(shù)字電路集成,由A/D轉(zhuǎn)換芯片(AD1674)將數(shù)據(jù)轉(zhuǎn)換成數(shù)字信號(hào)后,協(xié)調(diào)控制信號(hào)和各控制模塊[6]。當(dāng)探測(cè)器探測(cè)到信號(hào)后,將信號(hào)傳送到放大電路,通過(guò)第一級(jí)前置線性放大電路對(duì)傳送至放大器的脈沖信號(hào)進(jìn)行放大處理,如圖2所示。

模數(shù)電路將模擬量轉(zhuǎn)換為數(shù)字量以達(dá)到快速編譯脈沖信號(hào)的目的,方便計(jì)算機(jī)處理[7]。模數(shù)轉(zhuǎn)換電路的設(shè)計(jì)精度影響著分辨率和轉(zhuǎn)換精度,因此,轉(zhuǎn)換速度、轉(zhuǎn)換精度成為選擇分析器的AID芯片時(shí)的主要參數(shù)[8]。表1對(duì)比了幾種不同的AID芯片參數(shù)。

1.2 通信信號(hào)采集流程設(shè)計(jì)

通過(guò)模仿人類對(duì)模糊信息的表達(dá)方式推演出模糊控制算法,利用人的知識(shí)累積模糊規(guī)則庫(kù)數(shù)據(jù)與模糊化后的參考值進(jìn)行匹配后,輸出反模糊化數(shù)據(jù),該數(shù)據(jù)表達(dá)出的最終決策能達(dá)到與人腦類似的邏輯推理。模糊規(guī)則庫(kù)建立的過(guò)程可以比作有經(jīng)驗(yàn)的交警有時(shí)憑借工作以來(lái)積攢的交通指揮經(jīng)驗(yàn)來(lái)控制紅綠燈的開(kāi)啟,模糊規(guī)則庫(kù)就相當(dāng)于交警的指揮經(jīng)驗(yàn)[9]。模糊控制通過(guò)計(jì)算機(jī)與模糊規(guī)則庫(kù)對(duì)比后轉(zhuǎn)換成可以識(shí)別的語(yǔ)言,通過(guò)計(jì)算代替人做出合理的控制策略[10]。通信信號(hào)采集流程如圖3所示。

在交通控制系統(tǒng)中,對(duì)接收到的數(shù)字信號(hào)進(jìn)行變換等相應(yīng)的處理[11]。一般情況下,采用普通MCU控制的通信控制系統(tǒng)因?yàn)楸旧碇噶钪芷诘挠绊懲\(yùn)行速度慢,所以采用具有容易編程、運(yùn)行速度快的FPGA芯片。在信號(hào)采集系統(tǒng)的設(shè)計(jì)中,基于FPGR技術(shù)采用兩塊FPGA芯片,分別放置在采集系統(tǒng)的發(fā)送端電路以及由A/D轉(zhuǎn)換器和運(yùn)算放大器組成的信號(hào)接收端電路[12]。

2 實(shí)現(xiàn)通信信號(hào)采集處理

2.1 通信系統(tǒng)相位采集控制

控制器對(duì)整個(gè)信號(hào)采集系統(tǒng)協(xié)調(diào)工作起著重要的作用[13],ADC0809地址選擇器控制每一路通道的采集,然后程序?qū)⒋鎯?chǔ)在RAM中的ADC0809二進(jìn)制數(shù)據(jù)進(jìn)行讀寫模型描述[14],四相位的十字交叉路口通行示意圖如圖4所示。

在十字路口同時(shí)完成兩個(gè)方向所用的時(shí)間稱之為相位。分析各個(gè)相位的交通控制環(huán)境對(duì)設(shè)計(jì)交通控制系統(tǒng)顯得尤為重要。在實(shí)際交通控制中,一個(gè)十字路口通常分為東西南北四個(gè)方向的直行和轉(zhuǎn)向,所以一個(gè)十字路口有四種相位。保障系統(tǒng)能夠快速地對(duì)通信信號(hào)進(jìn)行采集和識(shí)別,在多路并行情況下及時(shí)變換信道位置信息,避免外界因素對(duì)信息波段產(chǎn)生干擾。因此本文提出多相位控制方法,如圖5所示。

該方法由若干個(gè)小的相位程序組成一個(gè)大相位程序,并對(duì)各個(gè)程序任務(wù)彼此之間的信息進(jìn)行交匯處理,完成系統(tǒng)通信信息資源采集和共享工作。系統(tǒng)中任一個(gè)小程序都可以跟隨另一個(gè)程序任務(wù)的執(zhí)行節(jié)拍進(jìn)行同步信息采集任務(wù),并通過(guò)最終的通信機(jī)制進(jìn)行信息傳遞和處理工作。

2.2 通信系統(tǒng)信號(hào)采集神經(jīng)網(wǎng)絡(luò)構(gòu)建

為了實(shí)現(xiàn)智能控制,首先對(duì)通行車輛進(jìn)行相關(guān)參數(shù)的測(cè)定。將控制器放在十字路口的中心位置,隨后將車流量檢測(cè)器放置在每條路段的入口處,把地感線圈檢測(cè)器鋪設(shè)在相距100 m左右的每條路面下面。測(cè)量當(dāng)前相位行駛車輛的通過(guò)頻率,將其作為是否測(cè)量下一相位的依據(jù)。根據(jù)實(shí)時(shí)采集的車流量數(shù)據(jù)對(duì)相位的順序進(jìn)行調(diào)整,以適應(yīng)不同情況下的交通需求。

根據(jù)模糊算法的定義,當(dāng)測(cè)得某一相位的車流量較少時(shí),可以減少該相位開(kāi)啟的時(shí)間。為了避免誤檢,保證后面排隊(duì)的車輛安全通過(guò),檢測(cè)器在相位開(kāi)啟后10 s才開(kāi)始工作。當(dāng)某一相位上車流量較多時(shí),適當(dāng)延長(zhǎng)相位開(kāi)啟的時(shí)間,但是考慮到其他相位上的車輛,所以不能超過(guò)預(yù)設(shè)的最長(zhǎng)時(shí)間。為了更好地對(duì)相位開(kāi)啟的時(shí)間進(jìn)行控制,設(shè)計(jì)控制系統(tǒng)神經(jīng)網(wǎng)絡(luò)結(jié)構(gòu)如圖6所示。

基于FPGA設(shè)計(jì)的交通控制系統(tǒng)計(jì)算速度快、穩(wěn)定性好,完全可以實(shí)現(xiàn)對(duì)各個(gè)相位進(jìn)行及時(shí)的交通調(diào)控。能夠快速地采集車流量并及時(shí)做出相應(yīng)的控制策略。為了克服現(xiàn)有交通控制系統(tǒng)的缺點(diǎn),更好地解決城鎮(zhèn)交通擁堵問(wèn)題,采用VHDL語(yǔ)言編程設(shè)計(jì)基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng),同時(shí)對(duì)設(shè)計(jì)系統(tǒng)進(jìn)行Quartus Ⅱ軟件平臺(tái)仿真模擬。仿真結(jié)果證明,該系統(tǒng)能夠根據(jù)車流量的實(shí)時(shí)變化及時(shí)做出相應(yīng)策略,有效地解決了交通擁堵的問(wèn)題。系統(tǒng)結(jié)構(gòu)如圖7所示。

3 實(shí)驗(yàn)結(jié)果與分析

為滿足系統(tǒng)的功能和技術(shù)要求,對(duì)系統(tǒng)進(jìn)行模擬測(cè)試。測(cè)試結(jié)果表明:各個(gè)電路模塊系統(tǒng)的各項(xiàng)功能均符合邏輯,系統(tǒng)運(yùn)行數(shù)據(jù)處理結(jié)果與軟件仿真后的結(jié)果一致,可以有效地進(jìn)行交通控制。仿真結(jié)果如圖8所示。

通過(guò)對(duì)比傳統(tǒng)并行通信信號(hào)相位進(jìn)行檢測(cè),發(fā)現(xiàn)利用現(xiàn)代計(jì)算機(jī)技術(shù)對(duì)實(shí)際交通狀況進(jìn)行微觀仿真模型研究能更準(zhǔn)確地預(yù)測(cè)交通狀況,該方法對(duì)多路并行通信信號(hào)的采集強(qiáng)度明顯優(yōu)于傳統(tǒng)方法,且在信號(hào)較多的情況下系統(tǒng)運(yùn)行相對(duì)穩(wěn)定,信號(hào)傳輸過(guò)程基本一致,不存在偏差,且比傳統(tǒng)方法節(jié)省了50%以上的檢測(cè)時(shí)間。從仿真的結(jié)果來(lái)看,所設(shè)計(jì)的交通控制系統(tǒng)涉及的各項(xiàng)功能都是可行的,控制系統(tǒng)功能已經(jīng)達(dá)到了預(yù)期目標(biāo)。

4 結(jié) 語(yǔ)

隨著人們生活質(zhì)量的提高和經(jīng)濟(jì)的飛速增長(zhǎng),城市車輛擁有量呈現(xiàn)出大幅度上升趨勢(shì),所以近年來(lái)交通擁堵問(wèn)題也越發(fā)引起人們關(guān)注。交通控制系統(tǒng)是交通系統(tǒng)中的核心,因此本文設(shè)計(jì)了基于FPGA技術(shù)的多路并行通信信號(hào)采集系統(tǒng)。該系統(tǒng)可快速采集車輛實(shí)時(shí)通過(guò)頻率,實(shí)現(xiàn)了系統(tǒng)和數(shù)據(jù)源的交換,進(jìn)而做出相應(yīng)的控制策略,可以較好地解決交通擁堵問(wèn)題,具有較高的實(shí)用性和廣闊的應(yīng)用前景。

參考文獻(xiàn)

[1] 李言武.基于FPGA和單片機(jī)的多路信號(hào)光纖傳輸系統(tǒng)設(shè)計(jì)[J].計(jì)算機(jī)測(cè)量與控制,2016,24(2):222?224.

LI Yanwu. Multi?channel signal optical fiber transmission system based on FPGA and MCU [J]. Computer measurement & control, 2016, 24(2): 222?224.

[2] 詹從來(lái),龍偉,丁遠(yuǎn)超,等.基于FPGA的多路數(shù)據(jù)采集與處理系統(tǒng)設(shè)計(jì)[J].深圳大學(xué)學(xué)報(bào)(理工版),2016,33(2):127?133.

ZHAN Conglai, LONG Wei, DING Yuanchao, et al. Design of multi channel data collection and processing system based on FPGA [J]. Journal of Shenzhen University (science & engineering), 2016, 33(2): 127?133.

[3] 李明.大數(shù)據(jù)環(huán)境下無(wú)線終端智能通信信號(hào)采集系統(tǒng)設(shè)計(jì)[J].電子設(shè)計(jì)工程,2017,25(16):94?98.

LI Ming. Design of wireless terminal intelligent communication signal acquisition system in big data environment [J]. Electronic design engineering, 2017, 25(16): 94?98.

[4] 喻鵬,肖大為,姬慶.基于FPGA的水下多路數(shù)據(jù)采集存儲(chǔ)系統(tǒng)[J].船電技術(shù),2016,36(10):58?60.

YU Peng, XIAO Dawei, JI Qing. Multi?channel signals sampling/storage system based on FPGA [J]. Marine electric & electronic technology, 2016, 36(10): 58?60.

[5] 李亮,方勇華,趙彥東,等.基于FPGA的紅外光譜信號(hào)采集系統(tǒng)設(shè)計(jì)[J].大氣與環(huán)境光學(xué)學(xué)報(bào),2016,11(4):313?320.

LI Liang, FANG Yonghua, ZHAO Yandong, et al. Design of infrared spectrum signal acquisition system based on FPGA [J]. Journal of atmospheric and environmental optics, 2016, 11(4): 313?320.

[6] 衛(wèi)建華,劉琪,齊攀,等.基于FPGA的可配置時(shí)序信號(hào)發(fā)生系統(tǒng)設(shè)計(jì)[J].國(guó)外電子測(cè)量技術(shù),2017,36(10):107?109.

WEI Jianhua, LIU Qi, QI Pan, et al. Design of configurable timing signal generator based on FPGA [J]. Foreign electronic measurement technology, 2017, 36(10): 107?109.

[7] 張一荻.基于FPGA的脈沖信號(hào)參數(shù)高精度測(cè)量技術(shù)研究[J].儀器儀表用戶,2017,34(1):32?33.

ZHANG Yidi. Research on precision measurement technology of pulse signal parameters based on FPGA [J]. Instrument user, 2017, 34(1): 32?33.

[8] 焦佳偉,石云波,鄒坤.基于FPGA和以太網(wǎng)的多通道數(shù)據(jù)采集系統(tǒng)[J].電子器件,2016(1):168?171.

JIAO Jiawei, SHI Yunbo, ZOU Kun. Multi?channel data acquisition system based on FPGA and Ethernet [J]. Electron device, 2016(1): 168?171.

[9] 鄭艷芳,唐海娣,李雪寶.基于FPGA的可調(diào)節(jié)FIR濾波器的設(shè)計(jì)與實(shí)現(xiàn)[J].微型機(jī)與應(yīng)用,2017,36(4):29?31.

ZHENG Yanfang, TANG Haidi, LI Xuebao. Design of adjustable FIR filter based on FPGA [J]. Microcomputer & its applications, 2017, 36(4): 29?31.

[10] 汪睿琪,石守東,林宜丙.基于FPGA改進(jìn)的Canny實(shí)時(shí)邊緣檢測(cè)系統(tǒng)[J].無(wú)線通信技術(shù),2017,26(3):32?37.

WANG Ruiqi, SHI Shoudong, LIN Yibing. Improved Canny real?time edge detection system based on FPGA [J]. Wireless communication technology, 2017, 26(3): 32?37.

[11] 張婉明,李琦,李金海,等.基于ARM與FPGA的便攜式GNSS信號(hào)采集回放系統(tǒng)設(shè)計(jì)[J].電子技術(shù)應(yīng)用,2016,42(10):58?61.

ZHANG Wanming, LI Qi, LI Jinhai, et al. Design of portable GNSS signal capture and playback system based on ARM and FPGA [J]. Application of electronic technique, 2016, 42(10): 58?61.

[12] 陳豐,吳裕斌,曹丹華.基于STM32和USB虛擬串口的EEG信號(hào)采集儀設(shè)計(jì)[J].儀表技術(shù)與傳感器,2016,68(12):65?68.

CHEN Feng, WU Yubin, CAO Danhua. Design of EEG acquisition system based on STM32 and USB virtual serial port [J]. Instrument technique and sensor, 2016, 68(12): 65?68.

[13] 張慧慧,孟令軍,韓朝輝.基于CPCIe的重型采煤機(jī)狀態(tài)監(jiān)測(cè)信號(hào)采集板卡設(shè)計(jì)[J].實(shí)驗(yàn)室研究與探索,2017,36(3):120?124.

ZHANG Huihui, MENG Lingjun, HAN Zhaohui. Heavy shearer condition monitoring data acquisition board design based on CPCle [J]. Research and exploration in laboratory, 2017, 36(3): 120?124.

[14] ZHANG J L, WU Q, DING Y P, et al. Techniques for design and implementation of an FPGA?specific physical unclonable function [J]. Journal of computer science & technology, 2016, 31(1): 124?136.