一種帶自動帶寬調(diào)整的10 Gbps跨阻放大器的研究與設計

鄭 薇,任 軍,劉 浩,尹 浩

(成都嘉納海威科有限責任公司,四川 成都610000)

0 引 言

社會的快速發(fā)展帶來了信息交換量的爆炸式增長。光纖通信因為傳輸速度快,信道容量大,體積小,重點輕等優(yōu)點成為熱門研究方向。隨著技術的進步,下一代接入網(wǎng)將以10 Gbps速率為主。作為關鍵部件之一的光接收機的第一級即為跨阻放大器,它與光電二極管相連,對其最重要的要求是較高的靈敏度以適應長距離通信的要求和較大的動態(tài)范圍以適應各種通信距離的要求。如何在保證帶寬的情況下,實現(xiàn)較高的靈敏度和較大的動態(tài)范圍一直是近年來跨阻放大器研究的重難點。本文基于65 nm CMOS工藝,設計了一種用于10 Gbps光接入網(wǎng)的跨阻放大器芯片。

1 電路設計

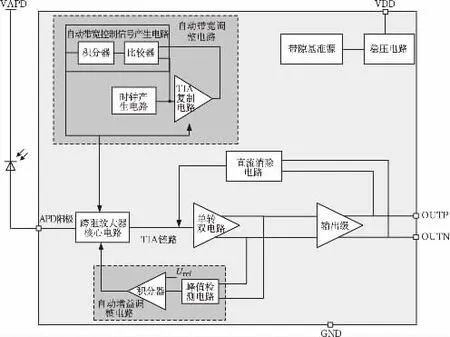

本文所研究的10 Gbps跨阻放大器的系統(tǒng)架構如圖1所示,主要由跨阻放大器、單轉雙電路、輸出驅(qū)動級、自動增益控制電路、自動帶寬控制電路、直流失調(diào)消除電路、帶隙基準源和穩(wěn)壓電路組成。以下將對跨阻放大器核心電路,自動帶寬控制電路及自動增益控制電路進行詳細研究。

圖1 跨阻放大器系統(tǒng)框圖

1.1 跨阻放大器(Transimpedance Amplifier TIA)核心電路

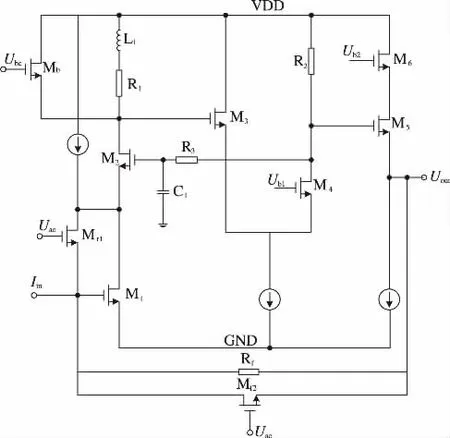

跨阻放大器核心電路位于整個跨阻放大器的第一級,其最關鍵的指標為-3 dB帶寬和輸入噪聲電流。本文所設計的TIA核心電路圖如圖2所示,輸入級采用共源共柵結構。反饋電阻Rf跨接在輸入和輸出之間,在小信號情況下,輸入級增益約為Rf。負載端采用有源電感L1拓展帶寬,為了避免R1消耗過大的電壓空間,采用了一個電流抽取結構,輸入管M1中的電流大部分從該電流抽取結構中流走,由此可以使負載電阻R1的取值盡量大,保證輸入級的增益足夠大,從而減小了由R1引起的噪聲。

圖2 跨阻放大器核心電路示意圖

1.2 自動增益控制電路(Auto Gain Control AGC)

TIA直接與APD相連,放大光電流。該光電流的變化范圍較大,典型值從5μA~2 mA變化,為了處理變化范圍如此寬的電流信號,設計了自動增益控制AGC環(huán)路對跨阻放大器核心電路中的增益進行調(diào)整,當輸入電流達到一定量時,AGC開啟,產(chǎn)生一個與輸入信號有關的控制信號Uac,將TIA核心電路的增益降低,保證電路在大信號時仍能正常工作。

AGC環(huán)路的電路拓撲結構如圖1中自動增益調(diào)整模塊所示。該AGC環(huán)路的原理是通過峰值檢測電路,檢測信號通路第二級單轉雙電路的輸出信號幅度,得出一個電壓;該電壓與參考電壓Uref進行比較,通過積分器產(chǎn)生一個與輸入幅值成比例能夠連續(xù)變化的電壓Uac;將Uac用來控制TIA核心電路中與輸入管相并聯(lián)的MOS管Mf1的柵極和與Rf并聯(lián)的MOS管Mf2,在小信號情況下,AGC環(huán)路未開啟,此時 Mf1、Mf2管處于亞閾區(qū),整個TIA的增益約為跨阻Rf。大信號情況下,這兩個MOS管開啟后均工作在線性區(qū),其導通電阻為

Mf1和Mf2設計為不同的尺寸,通過改變其導通電阻可以有效的改變TIA輸入電路的增益,使得輸入TIA在較大輸入電流下,輸出波形保持不失真。

1.3 自動帶寬控制電路(Auto Bandwidth Control)

帶寬是跨阻放大器中極為重要的一個指標,通常情況下,當工作溫度變化,芯片的生產(chǎn)工藝角有偏差時,芯片的帶寬均會有明顯的變化。當帶寬變大時,會引入更多的噪聲,從而惡化靈敏度;當帶寬變小時,會引入更多的碼間干擾(ISI)。本文設計了一種自動帶寬調(diào)整電路(ABC),在芯片內(nèi)部根據(jù)各種因素引起的帶寬變化進行自動調(diào)整,保持帶寬的恒定。該自動帶寬調(diào)整電路拓撲圖如圖1中自動帶寬調(diào)整電路框圖所示。

自動帶寬調(diào)整電路主要由三個部分組成,時鐘產(chǎn)生電路、自動帶寬控制信號產(chǎn)生電路、TIA復制電路。其工作原理為:由時鐘產(chǎn)生電路產(chǎn)生一個一定頻率的時鐘信號;該信號通過時鐘整形電路后同時送入比較器和TIA復制電路中;該復制電路與TIA核心電路具有相同的結構,在各種工藝角和溫度下,它的增益、帶寬與TIA核心電路具有相類似的變化趨勢。

時鐘信號經(jīng)過復制電路得到一個信號,該信號可以準確的反映跨阻放大器電路的工藝角和溫度情況,該信號與時鐘整形信號做比較,然后送到積分器中得到一個控制電壓Ubc。該控制電壓隨工藝角、溫度的變化而變化,將該控制電壓用來控制跨阻放大器核心電路中與負載阻抗相并聯(lián)的MOS管的柵極,通過控制該MOS管的開啟程度來實現(xiàn)自動調(diào)整TIA核心電路的帶寬。

2 測試結果

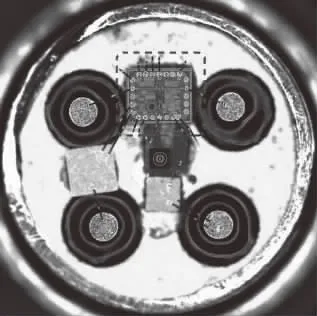

跨阻放大器芯片采用65 nm CMOS工藝進行加工和生產(chǎn)。將裸芯片與APD以TO-CAN的形式封裝進行測試,實物如圖3所示,其中圖片虛線框內(nèi)的芯片即為所設計的跨阻放大器芯片。

圖3 跨阻放大器TO-CAN封裝實物圖

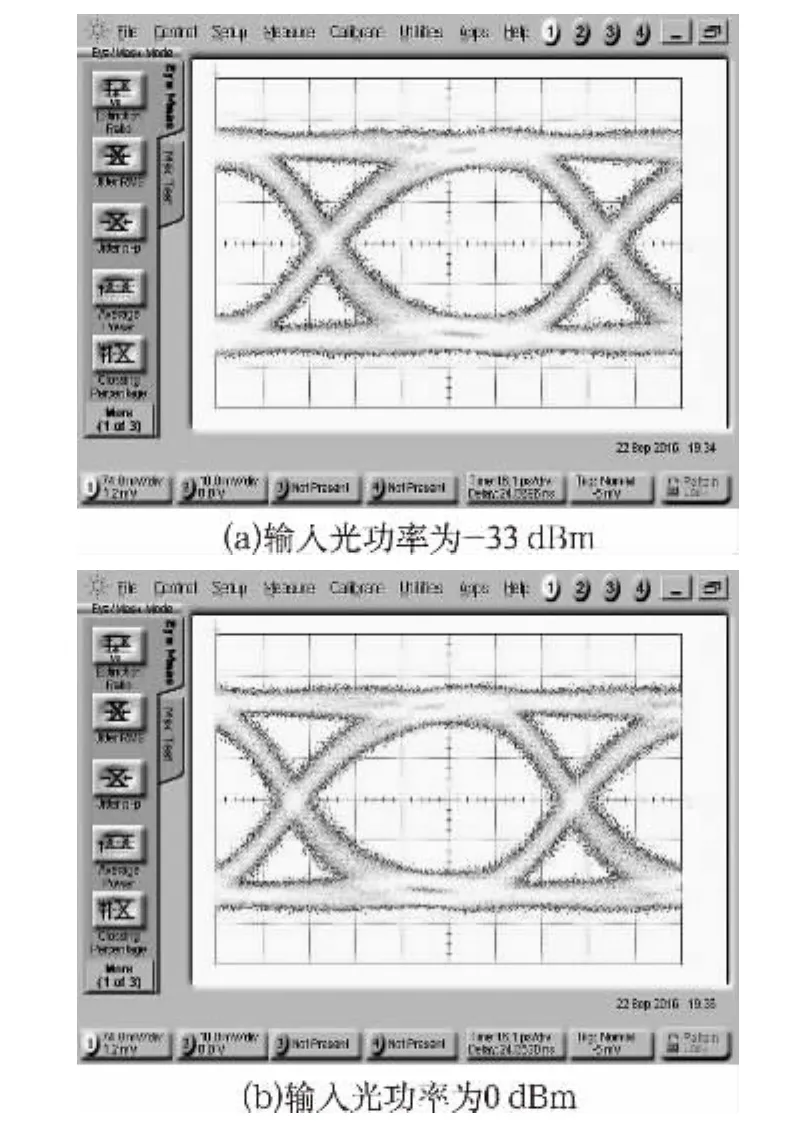

對輸出信號眼圖進行了測試,如圖4所示,輸入信號為10 Gbps,231-1的偽隨機碼信號,在靈敏度和過載光功率附近,跨阻放大器芯片眼圖均張開良好,圖形較對稱,上升較快,抖動較小。

實測的關鍵性能指標如下:工作電壓:3.3 V;工作 電 流:29 mA;-3 dB帶 寬:7.5 GHz;差 分 跨 阻:5.2 kΩ;動態(tài)范圍:33 dB;等效輸入噪聲:850 nA。

靈敏度:-33 dBm@ APD ER=8.2 dB BER=10-3PRBS=231-1;

過載:-2 dBm @ APD ER=8.2 dB BER=10-3PRBS=231-1。

圖4 輸出信號眼圖

3 結 論

本文采用65 nm CMOS芯片設計并實現(xiàn)了一種10 Gbps跨阻放大器芯片。實測結果表明,該芯片可達到-33 dBm的10-3碼靈敏度,0dBm過載功率,33 dB動態(tài)范圍,5.2 kΩ跨阻增益,7.5 GHz的-3 dB帶寬,采用3.3 V單電源供電,靜態(tài)功耗為95.7 mW,完全滿足10 Gbps光通信接收機的要求。