高速電路信號完整性分析與設計

沈俊杰

(杭州國芯科技股份有限公司,浙江杭州,310000)

1 高速電路信號完整性的概念

信號完整性是指在信號可以在電路中作出正確的反應和完整傳遞信息的能力,即在電路中信號可以有序的、按時的、符合規律的運行。良好的信號完整性是符合信號在電路中有序運行規律的,例如符合電路信號的完整性,要求信號從電路的始端到末端速度一致,并且輸送標準正確的信息,但是往往受到電磁兼容、串擾、傳輸線效應等現象的影響,信號的完整性會受到一定的影響,在嚴重的情況下,就會產生信號的不完整性,進而導致電路系統的失效。實際上高速電路中信號浮動速度過快,會產生突發的、難以預測的信號短路,在下面的幾個章節中,我們將具體的進行闡述。

2 信號完整性常見的問題

高速電路的運行速度通常過快,容易產生電壓不穩定的現象,這時高速電路非常容易產生特征抗阻,高速電路在運行過程中會產生傳輸端口和接收端口的傳遞信息和接收信息不相匹配的現象,不能完全傳遞的信息會形成反射現象,造成電路發生振鈴現象。另外,高速電路產生的故障類型不僅僅只有信號的反射現象,還包括傳輸線之間的串擾問題,傳輸時序問題,傳輸線之間的干擾問題,高速信號傳遞的下沖和過沖問題,等等。其實這些都是高速電路信號完整性常見的問題。下面一個章節我們具體對這些常見的問題進行分析,以期得出具體的解決措施。

■2.1 反射

信號的反射會造成系統信號振鈴現象,這是由于信號接收端口與傳輸線之間發生了阻抗不匹配現象,傳輸過程中信號并未被接收端口充分的接收和匹配,造成的信號返回,從而造成部分能量的反射,進而引發振鈴現象。

■2.2 串擾

串擾顧名思義就是不同信號之間的相互干擾,產生原因是相互傳輸的兩個信號所依托的傳輸線距離較近,受到電磁兼容等的影響會造成電磁干擾現象,影響不同信號傳輸的途徑,導致信號之間的串擾,這一現象損耗的信號完整性為兩個或兩個以上。

■2.3 時序

時序問題也是影響信號完整性的主要問題之一,當傳輸線過長或者受到某一因素影響造成的傳輸時效過長,就會導致信號從起始端口到接收端口的傳輸時間過長,時間越長對于信號的完整性越不利,當超過有效的信號傳輸時序后,接收端接收的信號可能就會造成元器件功能混亂,產生無法估量的錯誤。

■2.4 過沖與下沖

過沖與下沖現象的出現是信號傳輸速度過快或者變化較快導致的,信號的過沖和下沖會導致元器件功能的混亂,影響元器件的功能和使用,極易引起高速電路系統的失效。

■2.5 電磁干擾

電磁干擾是由周圍環境下產生的電磁輻射導致的,在高路運行環境下難免會產生相互零部件之間的電磁干擾,使得電子設備受到電磁干擾,甚至會造成電子設備的失靈。只有當高速電路運行時會產生較強的電磁干擾,所以高速電路極易受到電磁干擾的影響,應當在日常運行環境下加強對高速電路的電磁保護,減少周圍造成的電磁干擾.

3 信號完整性仿真技術以及模型示例

不同部分的信號完整性仿真技術可以減少高速電路設計過程中的錯誤,提前考慮信號完整性問題,下面具體分析信號完整性仿真技術的內容。進行實驗設計,完善高速電路的信號完整性,減少電路因為各種原因造成的信號完整性障礙。我們仍需要需要積極對相關技術進行創新,同時大膽分析信號完整性存在缺陷的各種原因,在錯誤中尋求答案和解決方法,以期運用到實際的高速電路信號完整性設計和應用中,對整個電路設計工作提供合理的正確的參考。

■3.1 反射分析與端接技術

3.1.1 反射的分析

上述簡單概述了反射產生的原因和具體現象,反射主要的表現是系統信號振鈴,振鈴現象出現的原因就是由于線路的反射現象的出現。反射現象出現的原因是信號接收端口與傳輸線之間發生了阻抗不匹配,傳輸過程中信號并未被接收端口充分的接收和匹配,造成的信號返回,從而造成部分能量的反射,進而引發振鈴現象。圖1為信號傳播模型。

圖1 信號傳播模型

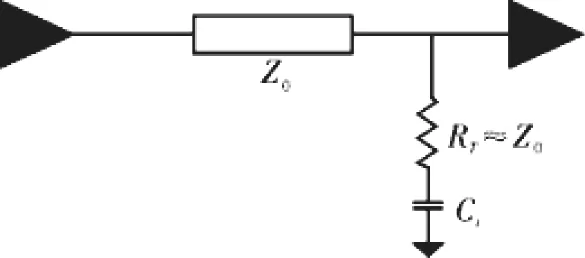

3.1.2 RC網絡端接

由于反射現象的存在,可以采用RC電路,為了降低信號傳播的速度,實現端接阻抗,電容通常取100 ~ 1 000 PF,端接電阻 R應等于傳輸線阻抗。RC電路端接的運用節省了較大的直流功耗,采用RC端接后信號反射現象得到改善。圖2為RC網絡端接模型,圖3為末端接與RC端接后仿真波形圖。

下面以圖3為例,圖3所顯示的是一個50MHz的時鐘,在沒有端接情況下的模型和在已經連接了RC端接的對比,線 1是源端時鐘, 線 2代表著接收端信號,由圖可知,左面的線路存在明顯的振鈴現象,右圖是采用了 RC端接時的波形圖,由圖可知,振鈴現象減弱甚至是沒有出現。

圖2 RC網絡端接模型

圖3 未端接與RC端接后仿真波形圖

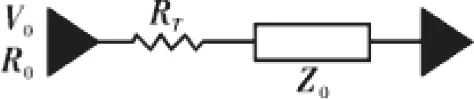

3.1.3 串行端接模型

為了實現信號源匹配抗組,需要設置串行端接,具體操作為在盡量靠近源端的位置串行插入一個電阻R T(范圍在10 Ψ–75 Ψ之間,本文采用的模型數值是33 Ψ)到傳輸線中,串行端接的功率消耗量較小,只需要每條線設置一個端接電阻即可,但是這回延緩信號的傳播效率,可見串行端接模型并不適合高頻電路,但是從中我們可以明顯的得出一個顯著的結論,就是利用串行端接后的模型,其信號反射現象明顯的減弱,甚至幾乎可以不再出現信號的反射現象了。圖4是串行端接模型的圖示。

圖4 串行端接模型

■3.2 串擾的分析和修正

3.2.1 串擾的分析

串擾顧名思義就是不同信號之間的相互干擾,產生原因是相互傳輸的兩個信號所依托的傳輸線距離較近,受到電磁兼容等的影響會造成電磁干擾現象,影響不同信號傳輸的途徑,導致信號之間的串擾。信號之間的串擾會造成耦合現象。當兩條導線存在較長接近段時會形成容性耦合,容性耦合還會形成噪聲干擾,這會造成在電路運行中產生噪音,損害整個電路系統;感性耦合是電流電路產生的磁場在鄰近的回路中引起變化的磁通,產生感應電壓的干擾 。

3.2.2 串擾的修正

串擾修正的方法有很多,例如,第一可以采用減小負載阻抗可以降低耦合的干擾的方法,原理是無論是容性耦合還是感性耦合,造成的串擾受到產生的負載阻抗影響,阻抗越大串擾越強,因此,為了降低串擾,應該減小負載阻抗。第二種方法是,最簡單也是最直接的就是令兩根相互影響的傳輸線原理,加大兩者的距離,避免電磁兼容現象出現。第三種方法是,減少平行線的長度。第四種方法是避免感性耦合現象的發生,具體做法就是避免信號共用回路,盡量減少回路數量和回路面積。

4 總結

綜上所述,隨著電子產品升級換代之迅速,對于高速電路信號完整性的要求越來越高,因此,應該提高高速電路信號完整性,提升高速電路系統的質量,實現電子產品在更新換代過程中的額穩步推進。但是高速電路信號完整性的探究并非一帆風順的,但也并不是非常困難的,只要我們積極探索,刻苦研究,就一定能攻克關于高速電路信號完整性這一艱難的課題,真正實現高速電路信號的完整性,從而為其他的高速電路設計研究項目和課題提供有用的參考和借鑒,實現我國高速電路信號設計的完善和成熟。