從1.0到6.0的飛躍之路PCIe總線技術發展解析

李實

PCIe作為目前PC系統中最主要的總線,從最初的1.0時代,發展到現在的6.0版本草案,經歷了多次PC架構的演化,也帶來了用戶體驗的一次次升級。現在,PCIe技術發展到了一個比較關鍵的路口,隨著人們對帶寬無止境的需求,現有的PCIe技術已經漸漸跟不上形勢的發展,新的技術究竟該怎么走,帶寬是否還能繼續翻倍發展呢?這一切,值得觀察和思考。

帶寬嚴重不足——需要新技術的PCI、AGP時代

1992年6月22日,英特爾發明了名為外部鏈接標準也就是PeripheralComponent Interconnect的接口規范,縮寫為PCI。PCI接口的特性在于采用的是并行傳輸方式,根據連接的數據寬度和頻率不同,能夠達到不同的數據傳輸速度。PC中使用的PCI主流標準有兩種,都采用32bit帶寬,頻率分別為33MHz和66MHz,帶寬分別是133MB/s和266HB/$。

PCI的帶寬有限.對日益強悍的GPU等高性能單元來說逐漸成為了瓶頸。因此,基于PCI的技術又發展出了AGP等專用于圖形卡的總線接口標準。AGP依舊是并行傳輸數據,考慮到插槽長度的問題,依舊采用了32bit的接口,但是采用多倍數傳輸數據的方式,頻率從66MHz起跳,最終達到533MHz(實際物理傳輸頻率依舊是66MHz),數據帶寬最大可達2133MB/s。

PCI和AGP等接口帶來了2000年左右PC市場的繁榮。隨著系締性能進一步提升,對帶寬要求越來越大。此時PCI和AGP的劣勢逐漸顯現了出來。實際上,PCI或AGP這樣的并行傳輸技術,無法在當時的技術條件下帶來性能的進一步提升。原因也很簡單,PCI或者AGP這樣的并行傳輸技術帶寬來自于兩個關鍵參數:位寬和頻率。32bit位寬在當時工藝下和插接口尺寸相關,很難在寸土寸金的主板上采用更大的比如64bit位寬(這一點僅在服務器主板采用的PCI-X插接口上實現了)。同時頻率受制于并行發送多個數據難以同步,高頻率數據容易遭受干擾以及主板制造成本等問題也門乎卡在了66MHz左右。因此,并行的PCI接口需要徹底改變才能適應未來的帶寬發展計劃。

終于在2001年8月3日,非營利組織PCI-SIG召集了九大廠商,包括英特爾、AMD、惠普、康柏、博通、IBM、微軟、德州儀器和鳳凰科技等,進行投票表決,并全票通過了新總線標準的相關協議,隨后這個標準就被正式命名為PCI Express,也就是我們今天看到的PCIe總線標準。

強悍“身板”——PCIe的技術基礎

在演進到PCIe之后,整個計算機架構的發展可謂走上了快車道。在這一部分,本文將解讀PCIe的技術基礎以及它為什么能夠在10多年之后依舊擁有強大的生命力。

從概念上來說,PCIe總線架構實際上是舊的PCI總線的高速串行替代產品,其最大的差別在于總線的拓撲結構:PCI總線使用的是共享并行總線架構,所有的PCI主機和所有的設備共享一組通用的地址、數據和控制線。PCIe基于點對點的拓撲結構,單獨的串行鏈路將每個設備連接到host(root compoex),由于其共享式總線拓撲結構,因此采用的是仲裁方式訪問,單個方向上一次只允許一個主設備存在。

在數據傳輸方面,舊的PCI時鐘方案采用的是總線上最醫的設備頻率作為基準數據傳輸頻率(不管有多少設備,也不管其他設備的情況如何),因此整體傳輸效率會被較慢的設備拉低。鑒于此,在傳統的PCI-AGP系統中,AGP總線需要單獨的控制器才能訪問和控制,并和通用的PCI鏈路徹底隔離。這樣顯然增加了系統的復雜程度。相比之下,PCIe改用了全新的任意兩個端點的全雙工通信,同時對多個端點的并發訪問沒有限制,系統只需要保留一個或者數個多通路的PCIe控制器,就可以實現對不同帶寬需求的設備進行控制。比如顯卡需要PCIEX16,SSD需要PCIEX4,聲卡需要PCIEX1,這些設備都可以掛接在一個PCIe控制器上,互相之間也不會受到影響。

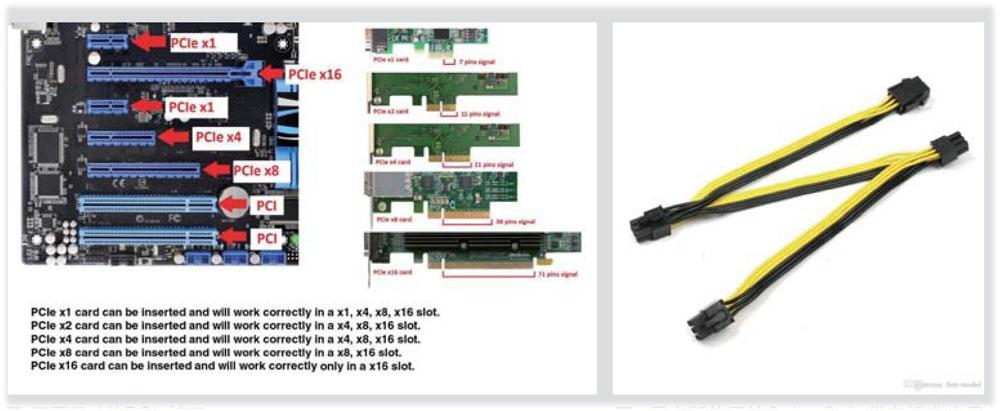

在總線協議方面,PCIe的通信數據使用了特殊的數據包封裝,打包和解包數據以及狀態消息流的工作由PCIe的端口事物層處理,不需要CPU的干涉。此外,PCIe總線在鏈接酉己對方面存在極高的靈活性。兩個設備之間的PCIe鏈路可以在x1和x32之間自由變動,此時吞吐量將隨著鏈路變動而變動。在實際工作中,鏈路之間的通道數量可以在設備初始化期間自動協商連接,可以采用最低鏈路的設備規格,也可以采用其他規格。舉例來說,可以將只支持PCIe x1的設備插入PCIe x4或者x16的插槽中,初始化時將自動設置為最高可相互支持的物理鏈接通道數。反之.也可以自行配置較少的通道數,這樣能夠在設備出現壞道或者不可靠通道時提供容錯性。

信號方面,PCIe規定了每一個通道中包含兩組差分信號對,其中一對差分信號用于接收數據,另外一對差分信號用于發送數據。因此每個PCIe通道都需要4條線纜或者信號跡線。一般來說,人們對這種同時可以收發的信息通道稱作“全雙工”信息傳輸通道。每次傳輸、鏈路端點之間的兩個方向上都會傳遞8位字節格式的數據包。采用串行信息的優勢在于,每個通道的每個方向只有一個差分信號,并且嵌入了時鐘信息,這使得整個系統的抗干擾能力大大增強,并且頻率極限被提升至干兆赫茲。

PCIe的初始標準定義了七種鏈路寬度,對應七種不同的物理插槽規格。這七種鏈路規格的通道數量分別為1組、2組、4組、8組、12組、16組和32組,對應的標識分別采用x1、x2、x4、x8、x12、x16和x32,不同規格的鏈路也和相應長度的物理插槽規格相匹配。一般來說,x16插槽是最常見的插槽規格,它用于接駁顯卡或者萬兆網絡、超高速SSD等高性能高帶寬設備。x32的插槽不太多見,往往用于服務器或者特殊場合。值得一提的是,由于PCIe規范的靈活性,人們往往設計智能切換方案來進行插槽鏈路配置,而不再需要和物理鏈路規格綁定。舉例來說,一個x16的PCIe鏈路,可以同時面向一個x16規格的物理插槽和一個x4規格的物理插槽。當x4物理接口沒有插入任何設備時,在優先級配置規范的指引下,PCIe鏈路將全部分配給x16的物理插槽;當x4規格接口插入設備后,PCIe鏈路可以限據配置需要,分配x12或者x8的鏈路給原本為x16的物理插槽,新的x4接口可以在不啟用和獲得x4帶寬之間自由選擇。

除了上述傳輸方面的設計外,PCIe在電源方面也作出了加強。根據PCIe規范,PCIe設計了數個專用的+12V和+3.3引腳,最大可供電能力為75W,這個供電能力已經完全可以滿足大部分普通設備的需求了。不過在實際使用中,受制于主板設計、PCB設計以及系統供電等原因,PCIe插槽的供電能力有可能達不到75W,各家廠商也會在相應的產品中予以說明。

1.0-3.0時代——PCIe鋒芒盡顯

初始時代:PCIe 1.0標準小試牛刀

PCIe 1.0a在2003年由PCI-SIG正式推出相關規范。PCIe 1.0a的每通道運行頻率為250MHZ,相應的數據傳輸速率為250MB/s,不過更正規的寫法被寫成2.5GT/s,也就是每秒2.5干兆次傳輸。這里需要注意的是,PCIe的每通道數據是打包傳輸的,其中不但包括需要傳遞的目標數據,還包括校驗信息。PCIe 1.0a實際傳輸10bit的信息,其中2bit為校驗信息,只有8bit為真正有用的信息,其傳輸帶寬開銷為20%,因此實際的有效信宮傳遞能力為每通道200MB/s。不過,初始的PCIe 1.0a版本在發布后很陜就被更新的PCIe 1.1規范替代。相比之前的1.0a版本,PCIe 1.1版本增加了一些功能和穩定性設計,帶寬和關鍵性指標完全相同,因此一般將其統一歸為PCIe 1.xs寸代。

支持PCIe 1.x規范的首款芯片組為英特爾在2004年6月發布的915P芯片組.支持的處理器為Pentium 4、雙核心的Pentium D以及面向頂級玩家的Pentium xE,首款支持PCIe技術的顯卡為AMD Radeon 9550的PCIe版本。此時的主板芯片組還尚未停止對PCI接口的支持,PCIe在此時主要用于緩解顯卡和CPU之間的通訊帶寬不足,而芯片組的其余部分擴展接口或多或少都擁有數個PCI插槽。

從數據上來看,相比AGP x8的2133MB/s的接口帶寬,為顯卡準備的PCIe 1.x x16的接口單向帶寬達到了4GB/s,雙向帶寬更是高達8GB/s,單向帶寬就相比AGP x8基本翻倍。不過,由于當時的顯卡本身性能較弱,再加上并非為PCIe高帶寬設計等因素,在幾乎相同規格的AGP x8接口和PCIe 1.0x16的性能對比中,PCIe 1.0 X16并沒有帶來類似于帶寬翻倍那樣顯著的3D性能提升,兩者性能差距并不大。作為初代產品,PCIe在此時展示的是強悍的擴展能力和幾乎無盡的潛能。此外,市場上還存在大量AGP接口的GPU芯片。為了滿足PCIe設備的需要,ATI和英偉達還設計了不同的橋接芯片來對GPU的數據接口規格進行轉換,并引發了一系列市場競爭的故事,比如著名的“有路何必修僑”就是由ATI提出,所謂原生PCIe接口顯卡更有優勢的市場宣傳口號。

PCIe 1.x時代持續的時間從本代實際產品上市(英特爾915P,2004年6月)到新一代實際產品上市(PCIe 2.0,英特爾X38,2007年8月)大約持續了3年多,接下來登場的就是長壽命的PCIe 2.0。

PCIe 2.0一統天下

PCIe 2.0規范發布于2007年1月,其規范主要變化在于相比PCIe 1.x,PCIe 2.0的每通道頻率翻倍來到了500MHz,相應的傳輸能力翻倍,達到了500MB/s,也就是5GT/s,不過數據編碼依舊使用了8bit/10bit的方式,也就是依舊需要使用20%的校驗帶寬。即使如此,PCIe 2.0在典型應用比如PCIex16接口的單向帶寬也達到了8GB/5,雙向帶寬更是達到了16GB/s。

除了帶寬暴增外,PCIe 2.0還帶來了不少新的技術,包括新增的輸入輸出虛擬化技術,可以讓多臺虛擬機共享PCIe設備;PCIe線纜子規范還加入了銅纜連接方案,每條線纜速度都可以達到2.5Gbps,滿足高速網絡連接的需求;另外還加入了動態鏈路管理和鏈路寬度管理以及電源控制等多項功能,繼續完善著PCIe的技術和生態體系。

首款使用PCIe 2.0技術的芯片組是英特爾2007年8月發布、面向頂級玩家的X38芯片組,AMD也推出了AND790FX與之呼應。首款支持PCIe 2.0技術的顯卡是英偉達的GeForce 8800GT,在止L2_后,AMD的Radeon HD 3800等一大批顯卡都加入了PCIe 2.0規范。

相比PCIe 1.x標準而言,PCIe 2.x的壽命是非常長的,從2007年8月實際產品發布開始,一直到接近4年半后的2012年4月,隨著新的處理器亡市,PCIe 3.x的實際產品才開始登臺亮相,并逐漸替換PCIe 2.x。即使到現在,也有不少市售主板依舊采用PCIe 2.x的設備和接口。

鋒芒盡顯:PCIe 3.x時代來臨

PCI-SIG在發布PCIe 1.x和PCIe 2.0相關技術標準時都比較順利,沒有遇到太多的技術難題。但是在PCIe 3.0上,PCI-SIG遇到引艮多技術難題。PCIe3.0的預覽規格早在2007年就宣布了(恰好是PCIe 2.0發布后沒多久),但是實際的首個版本PCIe 3.0規范在三年后的2010年11月18日才推出。

PCIe 3.0遇到的難題主要來自工程實現。PCIe信號在傳輸中采用的是銅介質,銅介質實際上是有其物理傳輸頻率上限的,目前的技術估計其物理上限大約在12GT/s。在PCIe 3.x規范研發之初,業內有消息稱新的PCIe的傳輸頻率會在PCIe 2.x的基礎上繼續翻倍,來到大約1GHz的水平,傳輸速率為10GT/s的水平。不過在當時的技術條件下,人們發現單純的頻率翻倍難以實現,包括相應連接器件的設計和線路布局都面臨困難,成本也可能大幅度上升。作為一個普適性的標準而言,這樣的情況讓人難以接受。不過,最終技術人員采用了巧妙的手段避開了頻率翻倍的問題。

PCIe 3.0的最終標準采用的是800MHz的運行頻率,其數據傳輸速率為8Gx/s,相比之前的PCIe 2.0提升了60%,并未翻倍。但是在數據校驗方面,PCIe 3.0s勺校驗不再采用8bit/10bit的小包校驗方式,轉而采用了全新算法的128bit/130bit大包校驗方式,以及全新的硬件加擾和解碼模塊等,其校驗帶寬開銷從之前的20%大跌至1.54%,甚至幾乎可以忽略,極大地提升了有效數據的傳輸帶寬。這樣一來,PCIe 3.0不需要翻倍傳輸速率就能夠達到實際帶寬基本翻倍的目的。

不過問題還沒有結束,即使是采用8GT/s的數據傳輸速率,PCI-SIG組織也懷疑當時的技術難以完成。為此,PCIe 3.0規范加入了一些增強信號指令,以及對數據完整性的優化,包括發送器和接收器以及拓撲結構等,再加上重新優化的PLL、數據通道等。但這還不夠,PCI-SIG還進行了為期六個月的技術分析,包括現有低成本材料是否能夠滿足PCIe 3.0高帶寬的需求等,好在最終一切順利。

最終完成的PCIe 3.0標準每通道帶寬為985MB/s,在PCIe x16帶寬下能夠達到15.7GB/s的水平,相比之前的PCIe 2.x基本做到了翻倍。此外,PCIe3.0標準的更新版本PCIe 3.P在2014年11月發布。加入了包括電源管理、性能優化和功能拓展等多項改變,當然本質的數據傳輸能力沒有變化。

由于PCIe 3.0的研發遇到了一些困難,因此PCIe 3.0的相關產品推出也比較晚。在處理器端支持PCIe 3.0的首款產品是英特爾第三代酷睿處理器,典型產品包括Core i7-3770,發布于2012年第二季度,搭配芯片組為英特爾6系列,包括Z68、P67等,不過CPU提供的PCIe 3.0 x16鏈路主要用于顯卡,其他設備基本無緣。主板方面,支持PCIe 3.0的產品就要晚很多了直到2015年9月英特爾發布100系列芯片組,其他設備才有幸使用到PCIe 3.0的帶寬。

從目前的產品和應用角度來看,PCIe 3.0依舊是當下的主力數據傳輸接口,尤其是對顯卡、SSD、高端萬兆網卡等設備來說,PCIe 3.0的出現和應用,解放了長期以來對這些產品在帶寬方面的約束,大幅度推動了產品的發展速度。尤其是SSD,在使用了相關PCIe規范的NVMe接口后,有效改善了電腦啟動、存儲數據時間長的不足。

從4.0到6.0——繼續翻倍、繼續前行

在PCIe 3.0之后,人們又將眼光瞄向了4.0時代。實際上也可以看出,隨著PCIe帶寬越來越大,PCIe技術每一代之間的時間間隔也越來越長。PCIe 1.x到PCIe 2.x之間只有3年,PCIe2.x到PCIe 3.x之間差不多4年半(PCIe 2.0直到現在也沒“下崗”),而PCIe 3.0到PCIe 4.0之間更是長達7年之久。

出現這樣的問題,依舊是銅傳輸的極限即將來臨。不過在PEIe 3.0之后,PCIe總線做出了很多改進,包括信號可靠性和完善性的改進,新的重定時器、發射器、接收器等,又將整個傳輸的性能和帶寬大大向前推進了一步,在這種情況下,PCIe 4.0誕生。

PCIe 4.0:帶寬暴增卻生不逢時?

PCIe 4.0的相關規范于2011年11月29日由PCI-SIG宣布。從表面規格來看,PCIe 4.0相比之前的3.x,傳輸速率直接翻倍來到了16GT/s,因此相比之下帶寬再度比PCIe 3.0翻倍。在6年后的2017年6月8日,PCI-SIG宣布PCIe4.0規范完成。

在傳輸方面,PCIe 4.0中加入了通道寬裕度設計通道寬裕度的功能在于隨時隨地監測PCIe的通訊情況,包括評估接收器波形圖相關數據的寬度在時間和空間上的差值,同時可以自動確認PCIe通道的余量,所有過程都是自動的,不需要任何人工干涉。另外,PCIe 4.0還加入了擴展的標簽和功能,這些功能可以協同工作,共同加強數據傳輸的可靠性、降低延遲并提高全帶寬的飽和度。其他的一些技術還包括整體減少的系統延遲、I/O虛擬化、平臺集成,可擴展性提升、增強的可靠性、可用性和可維護性(RAS)等內容。考慮到PCIe 4.0在技術上存在比較大的變化,因此可能需要新的硬件設備才能實現比較好的支持,確保使用的穩定性。

除了帶寬暴增之外,PCIe 4.0規范增加了不少新的內容,包括全新的通知機制Readiness Notification、精確時間管理Precision Time Measurement、獨立參考時鐘設計Separate Refclk IndependentSSC、全新的拓展方式Downstream PortContainment(DPC)和enhanced DPC以及輕量通知協議Lightweight Notification(LN)protocol等等。此外,在電源和功耗方面,新的PCIe 4.0也增加了諸如超低功耗狀態1 PM等,能夠帶來更低的休眠功耗,有利于移動設備使用。

目前支持PCIe 4.0的設備只有AMD銳龍3000系列處理器和X570主板,以及AMD新的Radeon RX 5700系列顯卡。此外業內一些存儲廠商還在第一時間推出了支持PCIe 4.0技術的SSD產品。從性能來說,PCIe 4.0的每通道帶寬高達約2GB/s,PCIe 4.0 x16的單向帶寬高達約31.5GB/s,雙向帶寬高達約63GB/s,性能非常出色。但是,目前英特爾反而宣布暫時沒有對PCIe 4.0的支持計劃,旗下所有產品都未提供對PCIe 4.0的支持。那么,英特爾是不打算支持更新的PCIe標準?顯然不是這樣.在PCIe 4.0發布之后,PCIe 5.0和PCIe 6.0的消息接踵而來。并且發布時間也非常近。這意味著PCIe 4.0可能曇花一現,也可能是生不逢時?

PCIe 5.0和PCIe6.0——近在眼前?

根據目前的消息,PCI-SIG組織已經在2019年5月發布了PCIe 5.0標準。相關的詳細信息目前還沒有太多資料,但是舊比PCIe 4.0,PCIe 5.0的帶寬再度翻倍,典型的PCIe 5.0 x16場景下,單向帶寬達到了約64GB/s,雙向帶寬高達128GB/s。為了達到如此的帶寬高度,PCIe 5.0采用了全新的信號完整性設計可以向后兼容的CEM連接器等設備,整體技術架構還是發生了比較大的變化。

根據業內估計PCIe 5.0的相關設備將在2019年亮相,并在2020年左右上市。不過PCI-SIG認為PCIe 5.0早期成本比較高,和PCIe 4.0暫時不會構成競爭關系。其中PCIe 5.0用于滿足數據中心、AI計算等高吞吐、高性能需求,而PC等設備將繼續使用PCIe 4.0。

由于PCIe 5.0的規范已經發布,那么接下來的PCIe 6.0也開始進行草案和相關技術準備了根據PCI-SIG的消息,PCIe 6.0相比PCIe 5.0帶寬再度翻倍,在典型的比如PCIe 6.0 x16場合下,單向帶寬可達到128GB/s,雙向帶寬則高達256GB/s。PCIe 6.0的主要技術要點包括:數據驗證改用了全新的Pulse Amplitude Modulation(PAM,脈沖幅度調制)方式,之前在PCIe 5.0上使用的NRZ不再使用。新的PAM是一種廣泛用于網絡傳輸的編碼技術,因此部署起來應該不算太難,這個技術允許PCIe 6.0在相同的時間內封裝更多數據。另外,PCIe 6.0還加入了低延遲向前糾錯方式(Forward ErrorCorrection),以有效地利用帶寬節約資源。PCI-SIG還有一些未公布的技術,用于更好地提高傳輸效率。在信道范圍方面,PCIe 6.0和之前的規范保持一致,大約為36dB。在兼容性方面,PCIe 6.0兼容之前的規格。在上市時間方面,PCI-SIG組織希望在2021年前完成相關規范的制定,最理想的情況下,相關產品在2022年上市。

總的來看,PCIe總線雖然不直接承擔各種計算、渲染任務,但對于電腦系統來說卻非常重要。就像一條道路,如果使用只有一條車道的村級道路將原材料運送給工廠:那么生產效率肯定不能同使用雙向4車道、雙向8車道乃至雙向10車道高速公路運送原材料的工廠相比。讓人欣慰的是,PCIe總線技術在近年來仍保持高速發展,PCIe 4.0-6.0的快速問世標志著未來可能出現的各類高性能GPU、SSD傳輸帶寬都能得到滿足,這些產品的性能可以得到充分的發揮。對于這些產品的廠商來說,他們只需要專注提升GPU、sSD的性能即可。因此在很長的一段時間內,PCIe總線仍將是電腦系統內各成員的主要“道路”,并成為不斷改善用戶體驗的重要保障。