用可編程邏輯器件實現火警報警電路顯示系統

朱建武

摘 要 采用了大規模可編程邏輯器件,用數字電路的設計方法,將優先編碼器和七段數碼管結合在一起實現了火警報警顯示電路。

關鍵詞 FPGA 編碼器 優先編碼器 七段數碼管 傳感器 開發板 集成電路

中圖分類號:TP202 文獻標識碼:A

1設計要求

假設分別有八層樓,每層樓裝有一個火警報警傳感器,當傳感器報警時,能在控制中心的顯示屏上顯示發生火警的樓層數,在FPGA開發板上模擬火警報警顯示電路。

2分析

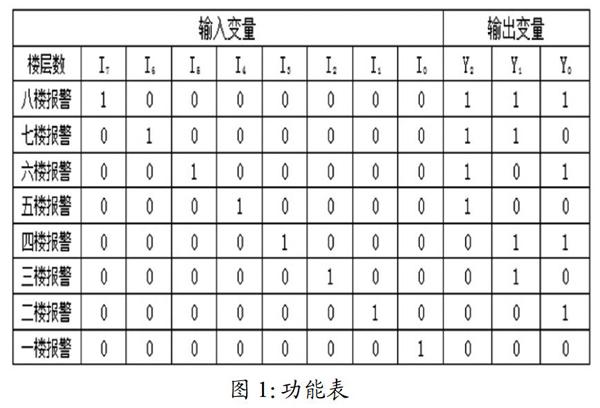

此電路的設計需要用到8-3線二進制編碼器74LS148,顯示譯碼器74LS48,七段數碼管,QuartusII開發工具,Altera公司的FPGA實驗開發板。用I0、I1、I2、I3、I4、I5、I6、I7變量分別代表八層樓的狀態,當邏輯值為1的時候,代表該樓層失火,當邏輯值為0的時候代表該樓層沒有失火。用Y0、Y1、Y2變量分別代表火警報警系統的三個輸出端,根據輸出端輸出不同的二進制的值從而可以判斷出火警發生的樓層數。

3大規模可編程邏輯器件

FPFA是一種可以編程的數字集成電路(IC,Integrated Circuit),其內部集成上千百萬個門陣列供使用,在功能上可以取代傳統規模的IC芯片組合的方式實現數字系統;更重要的是,其現場可編程特性允許設計人員在工作現場完成對邏輯塊和連線的配置,實現或更改復雜的電子系統的功能,所有的FPGA結構中都包含可配置的邏輯塊、可配置的I/O模塊和可編程互聯資源三個部分。

FPGA的主要開發流程:(1)設計輸入;(2)邏輯綜合;(3)功能仿真;(4)布局布線;(5)時序分析;(6)時序仿真;(7)編程及配置。

4存在的問題

(1)電路設計時考慮的是理想狀態,即樓層失火時不會出現兩層樓同時失火的情況,在現實中不會出現理想狀態只有一層樓失火的情況。……