基于FPGA的多路采集與TCP/IP傳輸系統設計

余恒松,鄧皓文,伍 春

(1.西南科技大學 國防科技學院,四川 綿陽 621000;2.西南科技大學 信息工程學院,四川 綿陽 621000)

0 引 言

在數據采集應用領域中,為了應對環境復雜多變的采集應用場景和滿足人們對采集精度越來越高的要求,除了采用高精度AD外,采集系統的遠程可控制和數據實時準確傳輸的能力也至關重要[1-3]。以太網是當今最通用的局域網通信協議標準,具有通信可靠、傳輸速度快、遠距離傳輸和適配多種傳輸介質等優點[4]。而TCP/IP協議具有開放的協議標準,不依賴固定的硬件或軟件系統,可以將TCP/IP協議集成于不同的網絡標準中。韓國WIZnet公司推出的W5500是一款集成了TCP/IP協議棧的全硬件以太網芯片,可以有效解決基于硬件的TCP/IP協議開發難度大且周期長的問題[5]。因此,本文設計了一種基于FPGA+W5500的多路數據采集與以太網TCP/IP傳輸系統,不僅可以實現16路模擬信號的并行采集,還可以滿足多路采集系統遠程可控制和數據實時準確傳輸的能力。

1 系統整體結構設計

本系統主要由信號采集部分和TCP/IP傳輸部分組成,其中信號采集部分由信號調理模塊和模數轉換器(ADC)組成。TCP/IP傳輸部分的主體為W5500,FPGA作為主控,需對采集和傳輸部分進行控制。系統的總體結構如圖1所示。

具體地,16路模擬信號并行進入采集系統的信號調理模塊,經過調理后的信號分成兩組(每組8路)輸入ADC中進行轉換,再由FPGA實現16路并行采集,最后由FPGA控制W5500將采集數據通過以太網發往PC機。

2 信號采集部分設計

信號采集部分由信號調理模塊和ADC組成。信號調理模塊包含低通濾波器和兩級放大器,信號采集部分的結構如圖2所示,信號采集部分則由FPGA進行控制。

模擬信號的輸入電壓幅值包含多個檔位,頻率范圍為10 Hz~20 kHz。為保證采集精度,需要采取低通濾波器開關可選和分級放大的方式,且放大器的增益可調。系統采用的ADC芯片為AD7609,采集精度為18 bit,支持8通道同步采樣。

圖2 信號采集部分的結構

3 TCP/IP數據傳輸系統設計

W5500支持TCP、UDP、IPv4、ICMP、ARP、IGMP和PPPoE協議,支持10/100M以太網通信。FPGA基于SPI協議對W5500內部的寄存器區和內存進行讀寫訪問。寄存器區由通用寄存器區和8個Socket_n(0≤n≤7)寄存器區組成。通用寄存器區用于配置網關、子網掩碼、源IP和源MAC地址等。Socket_n寄存器區用于配置Socket端口號、模式、配置命令等,且提供了Socket的狀態和中斷信息。W5500的內存大小為32 kB,分為接收內存和發送內存,各占16 kB,分別用于緩存網絡傳輸中已接收和待發送的用戶數據。

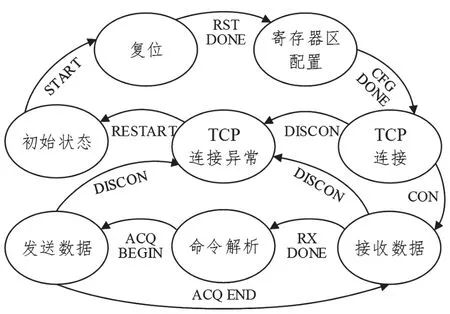

根據具體的采集應用場景,W5500(服務端)接收上位機(客戶端)的采集配置命令,并回傳采集數據。為簡化設計,采用狀態機控制W5500,狀態轉移圖如圖3所示。

圖3 主狀態機狀態轉移

經過復位、寄存器區配置、建立TCP連接后,用戶可由上位機下發采集配置信息,如低通濾波開關、通道選擇和放大器增益等。FPGA從W5500接收緩存讀取用戶配置信息,然后進行命令解析(將配置信息下發到信號采集部分),并啟動采集。16路數字信號并行進入FPGA,由異步FIFO轉換為串行數據流寫入W5500的發送緩沖。待采集結束后,返回接收數據狀態,繼續等待一下組命令。若TCP連接發生中斷、超時等異常情況,FPGA將重啟W5500。

TCP連接建立、數據接收和數據發送,是整個W5500控制狀態機的核心。選取Socket_0作為與上位機程序進行數據通信的端口。

(a)TCP連接建立的流程如圖4(a)所示。FPGA向Socke_0的配置寄存器Sn_CR[7∶0]寫入“OPEN”和“LISTEN”命令,分別將Socket_0端口初始化和配置為TCP服務器,通過檢查狀態寄存器Sn_SR[7∶0],判斷命令是否生效。配置完成的TCP服務器將一直監聽信道,等待客戶端的連接請求。

(b)TCP數據接收的流程如圖4(b)所示。中斷寄存器Sn_IR[7∶0]提供了Socket_0的中斷信息,當Sn_IR[2]為“1”時,表示W5500收到數據。Sn_RX_RD[15∶0]為接收讀指針寄存器,Sn_RX_WR[15∶0]為接收寫指針寄存器,分別提供了數據在接收內存中存儲的首地址和末地址,兩地址相減可得接收數據的長度。數據接收完成后,需將Sn_RX_RD[15∶0]的值更新為之前獲取的末地址值。

(c)TCP數據發送的流程如圖4(c)所示。發送寫指針寄存器Sn_TX_WR[15∶0]提供了發送內存中的首地址,FPGA需從這個首地址開始將數據寫入發送內存中,并將Sn_TX_WR[15∶0]更新為“首地址+數據長度”的值。發送“SEND”命令后,可輪詢檢查中斷寄存器的Sn_IR[4],若為“1”,表示數據發送完畢。

4 模擬信號采集實驗

4.1 TCP/IP傳輸實驗

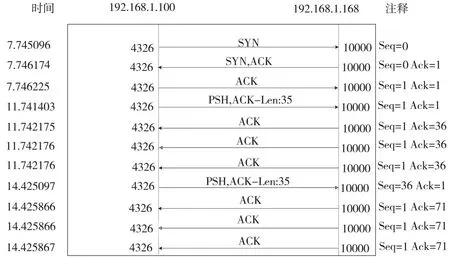

在進行TCP/IP協議通信測試時,將采集系統配置為服務器(IP:192.168.1.168,端口號:10000),上位機為客戶端(IP地址192.168.1.100,端口號為4326),采集系統與上位機的TCP/IP通信流量統計的結果如圖5所示。

圖5給出了TCP建立連接的“三次握手”、數據發送與回復ACK確認的過程,說明TCP/IP通信傳輸正常。

4.2 信號采集實驗

為了驗證數據采集系統的功能,選擇對一組小信號進行采集。使用FLUKE 5522A高精度校準儀產生一組正弦波模擬信號,信號幅度的有效值和頻率為15.91 mV、1 kHz。系統以200 kHz的采樣率進行采集,并經W5500上傳到上位機進行解析和顯示。

采集該信號時,FPGA需配置放大器的增益為200倍(第一級放大2倍,第二級放大100倍),放大后的峰值電壓為±4.5 V,上位機顯示采集信號的時域和頻域的波形如圖6所示,所采信號的增益精度滿足±0.1%的需求。

圖4 TCP建立和數據接收發送流程

圖5 TCP流量統計結果

圖6 采集信號的時域和頻域結果

5 結 論

本文設計了一種基于FPGA的多路采集與TCP/IP傳輸系統,采用FPGA+W5500架構,可以實現基于硬件的TCP/IP協議通信,并詳細介紹了系統的信號采集部分和TCP/IP數據傳輸部分的設計方法。經實驗表明,系統可以實現多路模擬信號的采集和可靠傳輸,且系統穩定可靠,具有一定的實用價值。