基于FPGA的LED點陣顯示控制方法

蔣中榮 甘俊杰 歐偉明

摘 要:為了研制基于FPGA的LED點陣顯示系統,文中論述顯示系統的硬件設計方案,給出16x16 LED點陣與FPGA芯片的接口電路,詳細介紹FPGA的基于IP核的設計方法。顯示數據存放在FPGA片內,其內部的控制邏輯單元與ROM存儲器分別進行設計,很方便地實現了22個字符的左移動態掃描顯示。充分利用了FPGA運行速度快、I/O引腳多、設計靈活的特點,該文提出的LED點陣顯示控制方法具有較好的實際應用價值。

關鍵詞:LED;點陣顯示;硬件設計;動態掃描;存儲機制;硬件調試

中圖分類號:TN873.3-34

文獻標識碼:A

文章編號:1004-373X(2019)24-0016-04

0 引言

隨著科學技術的發展進步,現場可編程門陣列(Field Programmable Gate Array,FPGA)作為嵌入式的一種,被廣泛應用于各個領域[1-2]。FPGA擁有豐富的硬件資源,具有較強的可重配置能力和靈活的設計方式,已經成為嵌入式系統設計的主流硬件平臺之一。與數字信號處理器(Digital Signal Processor,DSP)相比,FPGA能夠實現數字信號處理算法硬件流水或復雜的數字控制,可以滿足高速數字控制和硬件系統高度集成化的需求;與單片機( Micro-Controller Unit,MCU)或者是ARM相比[3-4],FPGA具有更豐富的I/0引腳和更高速的性能,并且FPGA是純硬件電路實現,工作時沒有CPU程序運行,從而可以提高系統可靠性和工作速度。

LED點陣顯示屏是隨著計算機技術、半導體微電子技術、光電子技術的迅猛發展而形成的一種新型信息顯示媒體,它利用發光二極管構成的點陣模塊或像素單元組成可變面積的顯示屏幕,以可靠性高、使用壽命長、環境適應能力強、性價比高、使用成本低等特點,迅速成長為平板顯示的主流產品,在信息顯示領域得到了廣泛的應用[5-10l。近幾年有關LED點陣顯示屏的研究論文,主要基于MCU和ARM實現[3-4],存在運行速度慢、控制單元與LED點陣顯示屏的接口電路復雜等不足。本文研究基于FPGA的LED點陣顯示控制方法,充分利用FPGA運行速度快、I/0引腳多、設計靈活的特點,以FPGA控制16x16 LED點陣實現左移字符串顯示為例,介紹系統的整體結構、FPGA芯片與LED點陣的接口電路、FPGA基于IP核的設計方法。

1 系統硬件設計方案

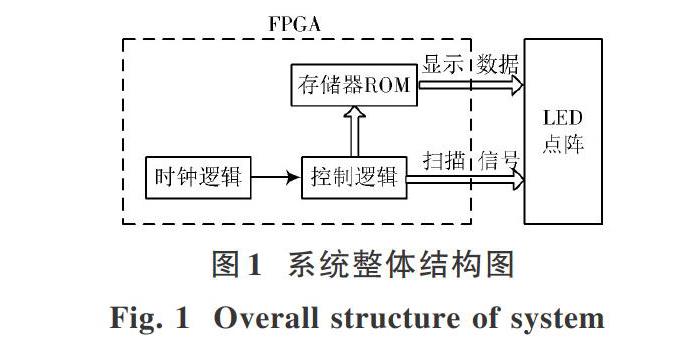

1.1 系統整體結構圖

基于FPGA的LED點陣字符和圖像顯示系統,由FPGA和LED點陣兩部分組成,如圖1所示。FPGA向LED點陣發送顯示數據和掃描信號,控制LED點陣的工作,實現字符和圖像的顯示。

FPGA芯片內部由3個單元電路組成:時鐘邏輯單元產生起同步作用的系統時鐘脈沖信號;存儲器ROM單元用于存放顯示數據,是基于FPGA的IP核而實現的,其中的顯示數據決定于所顯示的內容,顯示內容包括字符或者圖像;控制邏輯單元產生讀取存儲器ROM的地址信號和控制LED點陣的掃描信號,是基于FPGA的文本設計輸入方法實現的,如何完成其設計取決于LED點陣的顯示內容和顯示方式,LED點陣的顯示方式分為靜態顯示和移動顯示。

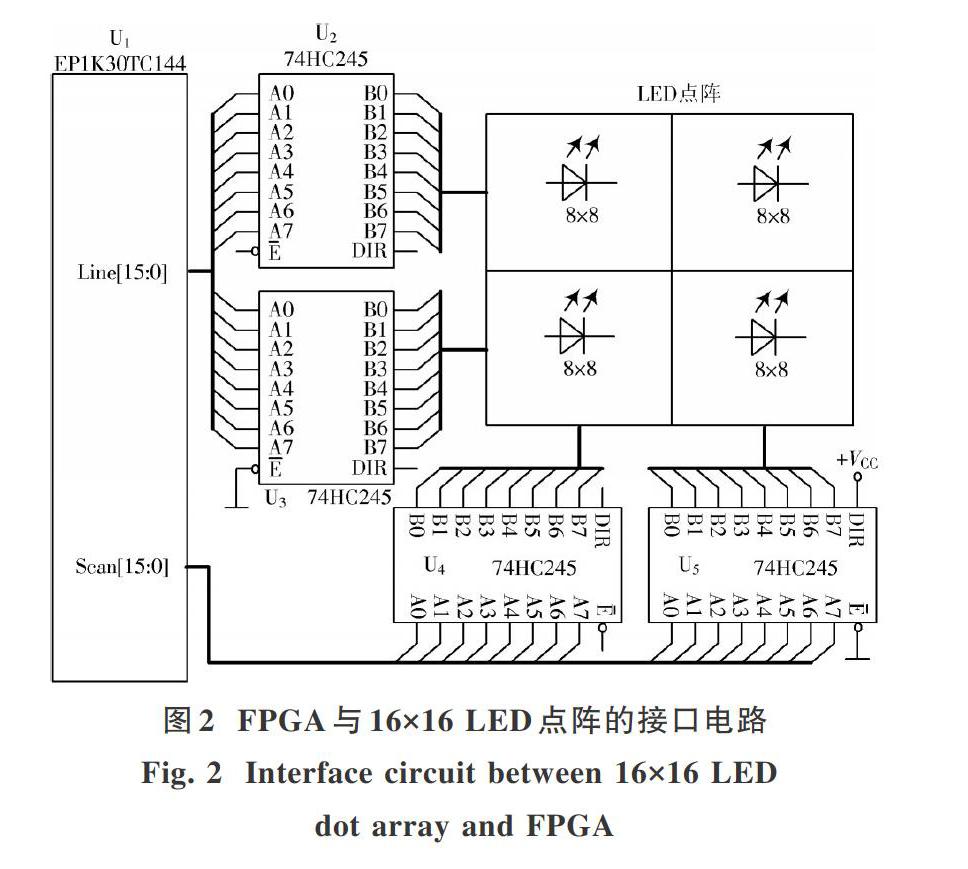

1.2 FPGA與LED點陣的接口電路

一般而言,LED點陣采用低電壓掃描控制方式來完成顯示,為了敘述的方便,本文采用16x16 LED點陣,并且采用列掃描控制方式。FPGA芯片與16x16 LED點陣的接口電路如圖2所示,U1是FPGA芯片,其型號為EPIK30TC144;U2-U3是8 bit總線驅動器,其型號為74HC245;16x16 LED點陣是由4塊8x8 LED點陣模塊拼接而成的。需要說明一下,本文選用的8x8 LED點陣模塊是行共陽、列共陰的。

由圖2可知,接口電路由4片總線驅動器U2-U5組成,其中,U2和U3接收FPGA提供的行顯示數據Line[15:0],并控制16x16 LED點陣的16行,行顯示數據是高電平有效;U4和U5接收FPGA提供的列掃描信號Scan[15:0],并控制16x16 LED點陣的16列,列掃描信號是低電平有效。

芯片U2和U3的每一個輸出引腳,最多提供1個發光二極管的陽極電流,所以U2和U3的驅動能力是足夠的。芯片U4和U5的每一個輸出引腳,最多提供16個發光二極管的陰極電流之和,U4和U5的驅動能力也是足夠的,但是當LED點陣顯示屏增大時,需要提供的最大陰極電流之和隨之增大,這時U4和U5的驅動能力不足,這種情況下可以在U4和U5的輸出端添加達林頓晶體管來滿

圖2所示接口電路的特點是,在每一個時鐘周期,在FPGA提供列掃描信號Scan[15:0]的同時,行顯示數據Line[15:0]也送到了LED點陣的行引腳,無論是行顯示數據,還是列掃描信號,FPGA是直接送達LED點陣引腳的,不需要FPGA外部芯片進行串并轉換和地址譯碼,因此,充分發揮了FPGA芯片的運行速度快和1/0引腳多的特點,即使LED點陣顯示屏增大時,接口電路也只是增加8 bit總線驅動器和達林頓晶體管,從而簡化了接口電路,完全能夠保證LED點陣顯示屏的刷新率和顯示亮度。

2 FPGA片內邏輯電路的設計

2.1 FPGA芯片內部電路框圖

由圖1可知,FPGA芯片內部由3個單元電路組成:時鐘邏輯單元、存儲器ROM單元和控制邏輯單元。FPGA片內邏輯電路的設計,是在FPGA開發環境Quar-tusⅡ下完成的,時鐘邏輯單元的設計很簡單,下面主要介紹控制邏輯單元、存儲器ROM單元的設計方法。

2.2 控制邏輯單元設計方法

如何完成控制邏輯單元的設計,取決于LED點陣的顯示內容和顯示方式,為了敘述的方便,擬定顯示內容為字符串,顯示方式為左移動態掃描顯示方式。因此,控制邏輯單元的功能是:產生讀取存儲器ROM的地址信號;產生LED點陣的列掃描信號。使用FPGA的VHDL硬件描述語言文本設計輸入方法,完成控制邏輯單元的設計,VHDL程序關鍵代碼如下:

Entity ControILogic is

Port(

clk:in std_logic;

//1 kHz,同步時鐘信號

ROM_Addr: out std_logic_vector(9 downto O) ;

//ROM地址信號

Scan : out std_logic_vector( 15 downto O )

//LED點陣列掃描信n號 );End Entity ControlLogic ;Architecture Artl of ControlLogic is Signal counter : std_logic_vector( 3 downto O) : = B"II11" ; Signal f_slow : std_logic ; Signal x: natural range O t0 287 := O; Signal y: natural range O t0 271 := O;

//271=287-16 , y控制左移Begin ROM_Addr <= conv_std_logic_vector( x , 10) ;

//存儲器 ROM的地址信號pl : Process ( clk) Begin if rising_edge(clk) then

if counter = B"OOOO" then

counter <= B"11lI";

else

counter <= counter- I ;

end if; end if; End Process pl ;p2 : Process( clk)

//256分頻器 Variable tmp: natural range O t0 255; Begin if rising_edge( clk) then

if (tmp=10#255#) then

tmp := O;

else

tmp := tmp +1;

end if; end if; End Process p2 ;p3 :

Process ( f_slow )

//y控制左移 Begin if rising_edge ( f_slow ) then

if (y=10#271#) then

else

end if; end if; End Process p3 ;p4 : Process ( counter)

//產生列掃描信n號 Begin Scan <= ( others => ' I ' ) ; case counter is

when B"0000" => Scan(0) <= 'O' ;

when B"0001I" => Scan( 1) <= 'O' ;

when B"O010"=> Scan(2)<='O';

when B"0011"=>Scan(3)<='0':

when B"0100"=>Scan(4) <='O':

when B"0101"=>Scan(5)<='O':

when B"0110"=>Scan(6)<='O';

when B."0111"=>Scan(7)<='0':

when B"1000"=>Scan(8)<='0':

when B"1001"=>Scan(9)<='0';

when B"1010"=>Scan(10)<='0':

when B."1011""=>Scan(11)<='O,:

when B"1100『t=>Scan(12)<='0,;

when B"1101"=> Scan( 13)<='0':

when B"111101t=>Scan(14)<='0';

when B"1111.t=>Scan( 15)<='0':

when others=>Scan<=(others=>1):

end case:

End Process p4;

End Artl;

2.3 創建只讀存儲器初始化數據文件

在FPGA芯片內部開發的存儲器ROM單元用于存放顯示數據,其中的顯示數據決定于所顯示的內容,首先根據顯示內容變換成顯示數據,再由顯示數據創建只讀存儲器的初始化數據文件。

顯示內容變換成顯示數據的過程,是在取字模數據軟件中完成的。例如,取字模數據的軟件有“PC-toLCD2002完美版”,其是一個綠色軟件。文章前面已述及,顯示內容為字符串“歐偉明指導數字系統設計2018年11月28日”,在取字模數據的軟件PCtoLCD2002完美版中,可以很方便地獲取字符串對應的字模數據(即顯示數據),當然也可以很方便地獲取顯示內容為圖像的字模數據。

根據得到的字模數據(即顯示數據),在開發環境QuartusⅡ中,就可以創建只讀存儲器的初始化數據文件ROM_data.mif.只要將字模數據拷貝到ROM_data.mif文件中即可。

2.4 創建只讀存儲器

本文在FPGA芯片內部實現存儲器ROM單元的設計,是基于FPGA的免費IP核而實現的。在開發環境QuartusⅡ中,利用開發商提供的免費IP核,設計了一個包含1 024個字,字長為16 bit的只讀存儲器ROM_1024_ 16。需要提醒的是,在設計過程中,要選中前面已經創建好的只讀存儲器初始化數據文件ROM_data.mif這樣就很方便地在FPGA芯片中,完成了存儲單元中存放有顯示數據的只讀存儲器ROM_1024_16的設計。

3 硬件調試結果

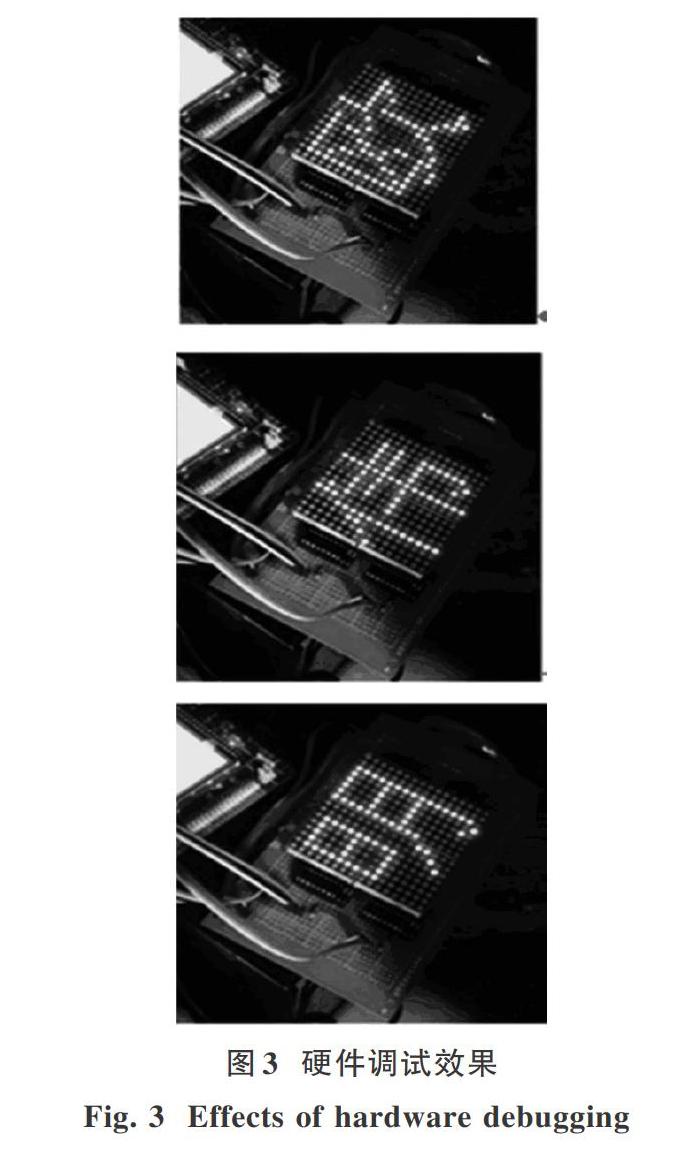

為了驗證本文所討論的LED點陣顯示系統實際效果,本文按照圖2所示電路,制作了基于FPGA的16x16LED點陣顯示系統,實現了在16x16 LED點陣上,向左移動顯示由22個字符組成的字符串“歐偉明指導數字系統設計2018年11月28日”。調試結果表明,LED點陣顯示穩定、清晰、亮度適中、無閃爍感,如果改變控制邏輯單元的時鐘脈沖頻率,就可以改變字符串向左移動顯示的速度。硬件調試效果如圖3所示。

3.1 硬件系統結構特點

對于采用MCU或ARM的LED點陣顯示系統而言[3-4],由MCU或ARM發送的顯示數據一般是串行傳送給具有鎖存功能的移位寄存器,比如8 bit的移位寄存器74HC595,如果要將一個8 bit的顯示數據送到74HC595芯片,就需要8個時鐘周期。然而一屏完整的顯示數據往往是遠大于8 bit,所以就需要更多的時鐘周期;而且移位寄存器中的顯示數據送達LED點陣,是在鎖存時鐘脈沖信號控制下完成的,所以還需要一個時鐘周期,因此,這樣嚴重制約了系統的整體工作速度,并影響LED點陣顯示屏的刷新率和顯示亮度。本研究的硬件系統主要由FPGA,LED點陣及其驅動器74HC245組成,結構非常簡單。由于采用FPGA芯片,一屏完整的顯示數據并行地由FPGA發送給驅動器74HC245,經其驅動后送達LED點陣,只需要一個時鐘周期。

3.2 FPGA的設計靈活性

系統中的FPGA芯片內部電路結構清晰且結構簡單,FPGA芯片內部電路的設計,是在開發環境QuartusⅡ下完成的,控制邏輯單元的設計采用VHDL硬件描述語言,可以利用VHDL語言很強的行為描述能力,從而實現復雜的數字控制算法。存儲器ROM單元的設計采用基于FPGA的IP核設計方法,這樣可以簡化設計過程,很容易獲得任意字長、包括任意多個字的只讀存儲器,并將顯示數據以初始化文件的方式融合到存儲器ROM單元的創建過程中。另外,設計完成后,FPGA是純硬件電路,工作時沒有CPU程序運行,從而可以提高系統可靠性和穩定性。

4 結論

本文以16x16 LED點陣為例,論述了基于FPGA的LED點陣顯示控制方法。實驗結果對于本技術領域的技術人員而言,很容易將這種控制方法用于更大的LED點陣。實驗結果表明本文介紹的基于FPGA的LED點陣顯示控制方法,充分利用了FPGA運行速度快、1/0引腳多、設計靈活的特點,具有較好的實際應用價值。

注:本文通訊作者為歐偉明。

參考文獻

[1]歐偉明,聶輝,李圣清.基于FPGA的機械抖動測量方法[J]核電子學與探測技術,2014,34(8):998-1001.

OU Weiming, NIE Hui, LI Shengqing. Measurement methodof mechanical dither based on FPGA [J]. Nuclear electronics&detection technology, 2014. 34(8): 998-1001.

[2]李銳,田帆,鄧賢君,等.基于FPGA的全數字延時鎖相環的設計[J]現代電子技術,2019,42(6):69-75.

LI Rui, TIAN Fan. DENG Xianjun, et al.Design of all-digitaldelay-locked loop based on FPGA [J]. Modern electronics tech-nique, 2019, 42(6): 69-75.

[3]歐偉明,劉歡,李圣清.燃弧時間傳感器的研制[J]電子測量與儀器學報,2014,28(4):441-446.

OU Weiming, LIU Huan. LI Shengqing. Development of anarc time sensor [J]. Journal of electronic measurement and in-strument. 2014. 28(4): 441-446.

[4]張學成.基于電力線載波模塊的LED點陣圖文顯示系統[J]液晶與顯示,2011,26(3):350-353.

ZHANG Xuecheng. LED dot matrix graphics and text displaysystem based on power line carrier module [J]. Chinese journalof liquid crystals and displays, 2011. 26(3): 350-353.

[5]鄭爭兵.基于FPGA的圖形點陣液晶顯示系統設計與實現[J]液晶與顯示,2013,28(3):403-407.

ZHENG Zhengbing. Design and implementation of graphic dotmatrix LCD display system based on FPGA [J]. Chinese journalof liquid crystals and displays, 2013, 28(3): 403-407.

[6]朱曉青,馬定寰,李圣清,等,于BP神經網絡的微電網蓄電池荷電狀態估計[J].電子測量與儀器學報,2017,31(12):2042-2048.

ZHU Xiaoqing, MA Dinghuan, LI Shengqing, et al.Estima-tion of state of charge for micro-grid battery based on BP neu-ral network[J].Journal of electronic measurement and instru-ment, 2017. 31(12): 2042-2048.

[7]袁謙,黃波,張多英,等,基于FPGA的可見光波段便攜式光譜儀的設計[J],現代電子技術,2019.42(6):100-104.

YUAN Qian, HUANG Bo. ZHANG Duoying,et al.Design ofFPGA - based portable spectrometer working in visible lightband [J]. Modern electronics technique, 2019, 42 (6): 100-104.

[8]劉歡.基于FPGA的多路溫度開關檢測系統的設計[D].株洲:湖南工業大學,2015.

LIU Huan. Design of multichannel temperature switch detec-tion svstem based on FPGA [D]. Zhuzhou: Hunan University ofTechnology, 2015.

[9]歐偉明,聶輝,張婷,電氣開關接點機械抖動次數的測量[J]電子測量與儀器學報,2014,28( 11):1268-1273.

OU Weiming, NIE Hui, ZHANG Ting. Measurement of themechanical dithering number of electric switch contact [J]. Jour-nal of electronic measurement and instrument, 2014, 28( 11):1268-1273.

[10]歐偉明,凌云,李圣清.基于同步串行通信的汽車TPMS低功耗設計[J]汽車安全與節能學報,2018,9(4):427-432.

OU Weiming, LING Yun. LI Shengqing. Low power consump-tion design of automobile TPMS based on synchronous serialcommunication [J]. Journal of automotive safety and energy,2018. 9(4):427-432.

作者簡介:蔣中榮(1964-),男,副教授,主要研究方向為PLC控制技術與嵌入式系統應用。

歐偉明(1962-),男,碩士,教授,碩士生導師,主要研究方向為信號處理、嵌入式系統。