基于改進型窗口比較器的多級輸入狀態檢測與邏輯判斷電路設計

劉加松,宋玉宏,周捷信

(順德職業技術學院,廣東 佛山 528300)

0 引 言

電路系統或電路模塊的輸入狀態正常與否,影響整個系統的工作狀態,一般需要進行輸入狀態的檢測。如果是多級,還需要進行邏輯判斷[1-3]。當電壓作為系統的輸入時,具有欠壓、過壓及正常三種狀態。及時判斷輸入電壓的狀態,有利于提高電路系統的工作性能和壽命。

檢測多級輸入電壓的狀態進行邏輯判斷一般有兩種方法,即硬件電路法和單片機軟件編程法。采用硬件電路法時,一般通過比較器對電壓信號進行比較檢測得到邏輯電位,而后將檢測得到的邏輯電位信號直接傳遞給邏輯復合電路進行邏輯判斷,得出一個實際控制信號供給電位保護電路。純硬件電路常用于單個輸入電壓狀態檢測[4]。采用單片機軟件編程法時,必須先通過模數轉換模塊采樣檢測電壓信號,而后通過單片機軟件編程進行邏輯判斷,以方便地進行多級輸入信號判斷[5]。

單片機軟件編程法相對于硬件電路法在性能上的受制約因素更多[6]。硬件電路法相比于單片機軟件編程法,對電壓信號的直接邏輯判斷響應更及時、更靈敏,且電位測量范圍廣、誤差范圍小,整體電路的實現成本低。在相同性能情況下,單片機軟件編程法的響應不如硬件電路法及時,且不易于集成化,整體電路的實現成本相對較高。

本文進行硬件的輸入狀態檢測與邏輯判斷電路設計,根據多限窗口比較器進行改進,使其成為改進型窗口比較器,并按提出的改進方案進行仿真,最終將設計方案用于一款雙電壓等級(雙級)輸入的逆變器進行驗證。

1 多限窗口比較器電路

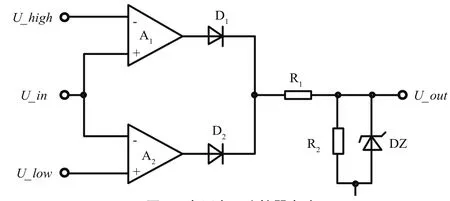

單電壓等級(單級)輸入狀態的檢測和判斷可以通過電壓窗口比較器實現[7]。圖1是一個標準電壓窗口比較器電路(也稱雙限比較器)[4,8],其中U_high表示窗口比較器高閾值電壓,U_low表示窗口比較器低閾值電壓,U_in表示窗口比較器被比較電壓,U_out表示窗口比較器比較輸出電壓,且U_high>U_low。

圖1 電壓窗口比較器電路

該電路由兩個電壓比較器(A1、A2)組合而成,每個比較器的輸入端都接有閾值電壓和被比較電壓。兩個電壓比較器通過比較兩個電位的高低,分別得到兩路比較輸出電壓。兩路比較輸出電壓通過兩個二極管(D1、D2)構成的“或門”邏輯電路,復合成一路邏輯輸出電壓。邏輯輸出電壓又通過分壓器(R1、R2)和穩壓二極管DZ進行降壓穩壓,最終得到U_out。該電路的輸出特性如圖2所示。

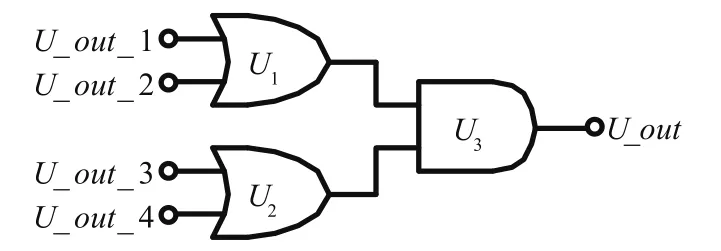

圖4 邏輯復合電路

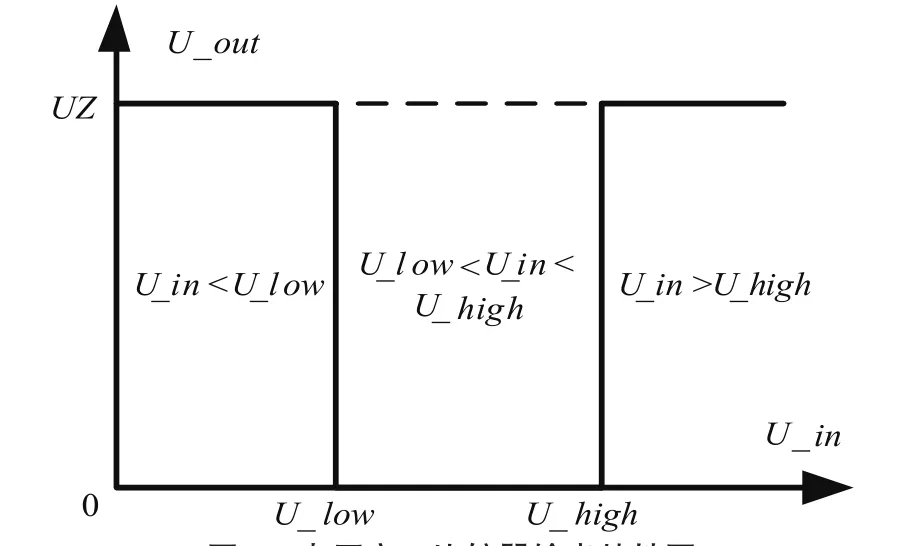

圖2 電壓窗口比較器輸出特性圖

從原理上看,將U_in<U_low情況稱為欠壓電位邏輯,將U_in>U_high情況稱為過壓電位邏輯。根據該電路的輸出特性,圖1的電路可以看成是單路欠壓邏輯信號與單路過壓邏輯信號的“加法”(邏輯或)復合而成,即該電路實現了單級輸入欠壓與過壓狀態檢測與邏輯計算。

基于上述的電壓窗口比較器電路,若被比較電壓具有兩個等級——兩種欠壓與過壓狀態,即四種狀態時,可以借鑒窗口比較器的工作原理設計出多限比較器電路,如圖3所示。

圖3 多限比較器電路

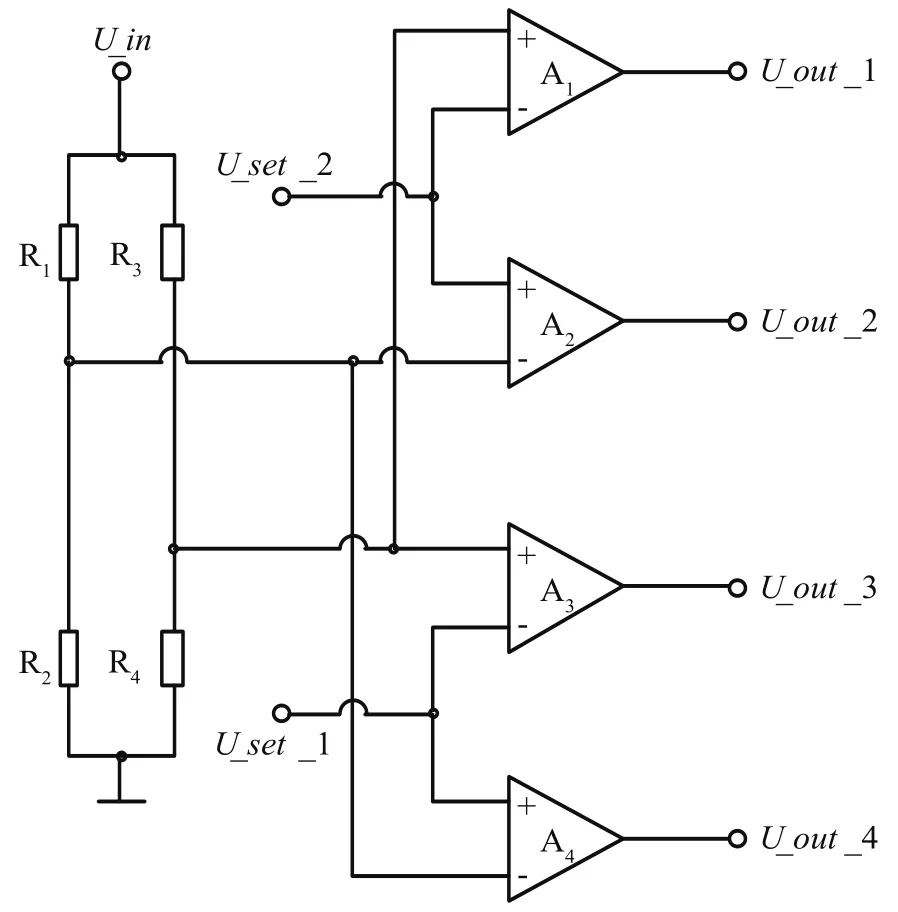

它的主要原理是將兩個窗口比較器先從被比較輸入端進行復合,即四個電壓比較器共用同一個被比較電壓U_in。同時,每個電壓比較器都有屬于自己的比較閾值電位,即U_high_1、U_low_1、U_high_2、U_low_2,且U_high_2>U_low_2>U_high_1>U_low_1。而后將得到的比較輸出電壓即U_out_1、U_out_2、U_out_3、U_out_4,通過邏輯電路進行電壓的邏輯復合,即可得到多限比較輸出電壓。它的邏輯復合電路如圖4所示。

在圖4電路中,四路邏輯輸入信號U_out_1、U_out_2、U_out_3、U_out_4分為兩組,U_out_1與U_out_2為一組、U_out_3與U_out_4為一組。每組信號輸入一個二或邏輯門(U1、U2),兩組信號通過或運算后得到兩組運算輸出信號,而后將得到的兩路運算輸出信號送入與邏輯門(U3),最終得到復合輸出信號U_out(假設U_out高電平為U_max,低電平為0)。

若假設U_out_1為A,U_out_2為B,U_out_3為C,U_out_4為D,U_out為Y,可知該邏輯復合電路的一般表達式為:

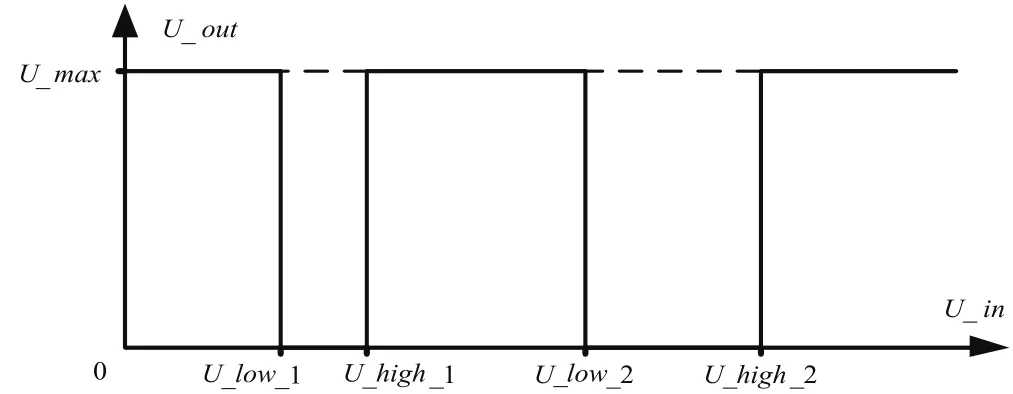

基于此,將圖3與圖4電路相結合,可以得到多限比較器電路的輸出特性,如圖5所示。

圖5 多限比較器電路輸出特性圖

2 改進型窗口比較器電路

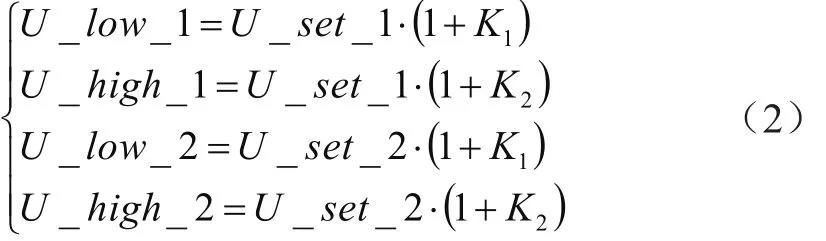

圖3的電路中涉及四個不同的閾值點電位。通常,每個閾值點電位值的設定由一個基準電位電路產生。同時,每個基準電位電路的相關設定值受電子元件相關參數的制約,可能在實際設計中得不到一個最理想的閾值點電位值,使得本電路在實際應用中受到制約。因此,針對以上實際問題,結合多限電壓比較器的特點,對窗口比較器電路進行改進,減少閾值點個數。在雙級入情況下,僅需設置兩個不同的閾值點U_set_1和U_set_2。

當系統輸入U_in為兩種電壓等級U_in_1、U_in_2時,保證系統正常工作的輸入上限與下限值一般是明確的,即U_low_1、U_high_1、U_low_2和U_high_2已知,且有U_high_2>U_low_2>U_high_1>U_low_1。閾值點U_set_1和U_set_2根據方程式(2)確定:

上述方程有4個未知量,可以求解出U_set_1、

U_set_2以 及K1、K2。U_set_1、U_set_2滿 足U_set_1<U_set_2。根據圖5的輸出特性,令:

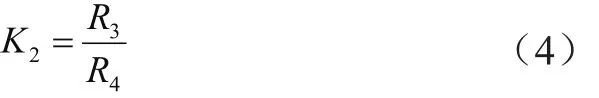

可設計出雙級復合型窗口比較器電路,如圖6所示。

圖6 雙級復合型窗口比較器電路

可見,該電路將圖3多限比較器電路所需的四個電壓閾值點電位個數減少為兩個(U_set_1、U_set_2)。同時,將輸入被比較電壓U_in通過兩路不同的分壓支路(R1與R2、R3與R4)進行分壓,然后將得到的兩路分壓后的電壓分別送入比較器的同相端和反相端與閾值電位比較。隨后,將得到比較輸出電壓,即U_out_1、U_out_2、U_out_3、U_out_4。通過邏輯電路進行電壓的邏輯復合,即可得到一路多限比較輸出電壓。在這里,按照方程求解的K1、K2控制好電阻分壓支路的分壓比,再結合圖4邏輯復合電路,即可實現如圖5所示的輸出特性。

可見,兩路電壓輸入下限值U_low_1、U_low_2和上限值U_high_1、U_high_2成為對應輸入下的等效欠壓狀態和過壓狀態下的閾值點電位。輸入電壓通過分壓電路取值后,與U_set_1、U_set_2比較,等效于輸入電壓直接與U_low_1、U_high_1、U_low_2和U_high_2比較。此種方法把欠壓與過壓區轉化成兩路,在電路中只要使用兩個比較閾值點電位即可構成所需的電位鑒別。這正是該電路的創新之處,相比常規多限比較器電路在閾值點電位上所需個數少。

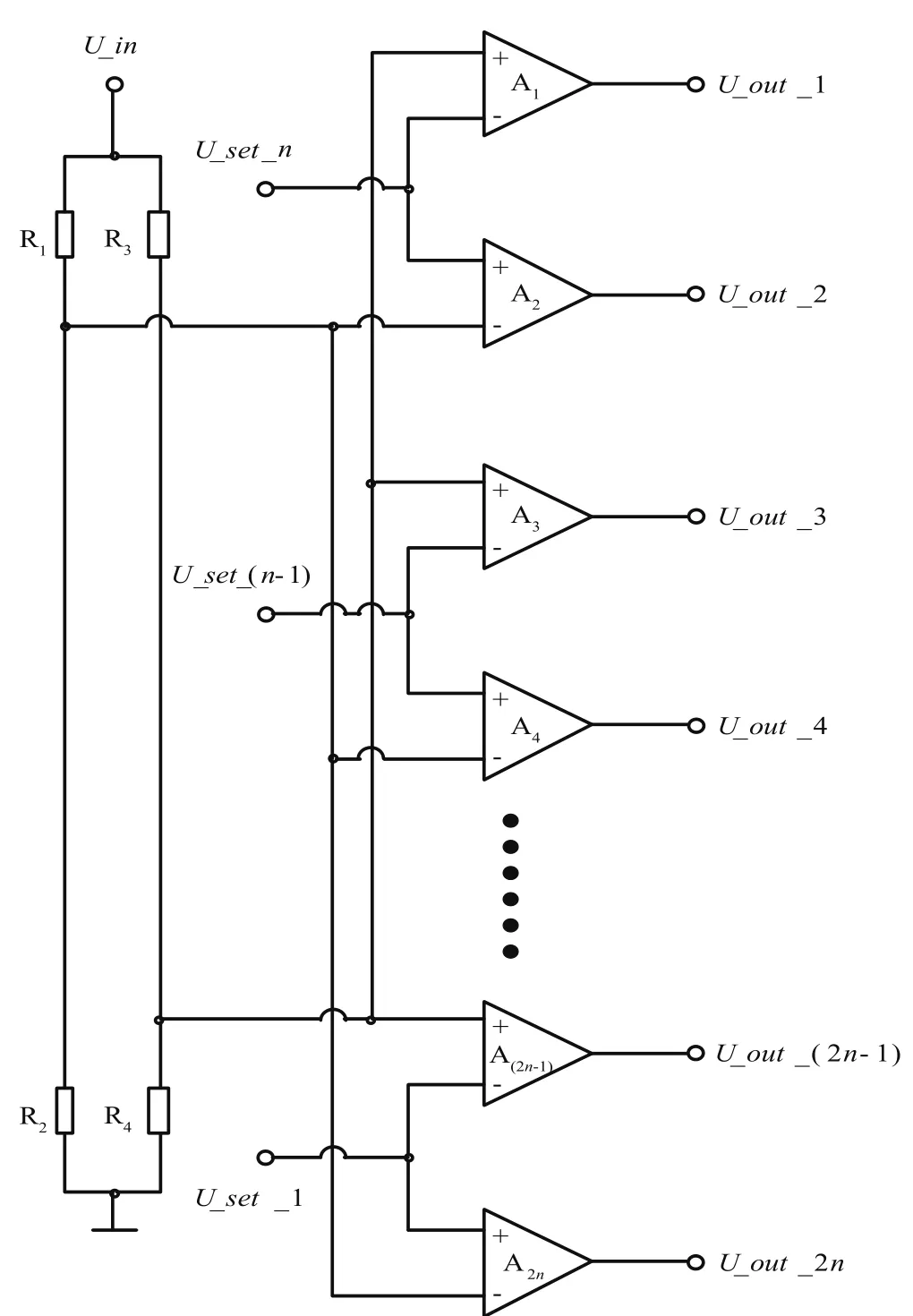

拓展上述原理,設計出多級復合型窗口比較器電路,如圖7所示。其中,U_set_1、U_set_2、…、U_set_n是電路所設定的閾值電位點,n級輸入電路則設置n個閾值電位點。

在此,由電位上限與下限值的性質可知,在n級輸入中,每一級電位的上限與下限值滿足:U_high_n>U_low_n>U_high_(n-1) >U_low_(n-1) >…>U_high_1>U_low_1。同時,多級復合型窗口比較器電路的各個閾值點電位應滿足U_set_n>U_set_(n-1)>…>U_set_1。

所以,各閾值點U_set_1、U_set_2、…、U_set_n的值可由式(5)確定:

圖7 多級復合型窗口比較器電路

圖7多級復合型窗口比較器電路的各個閾值點電位值的計算,與雙級復合型窗口比較器的閾值點計算推導類似,不再贅述。

3 實際應用設計

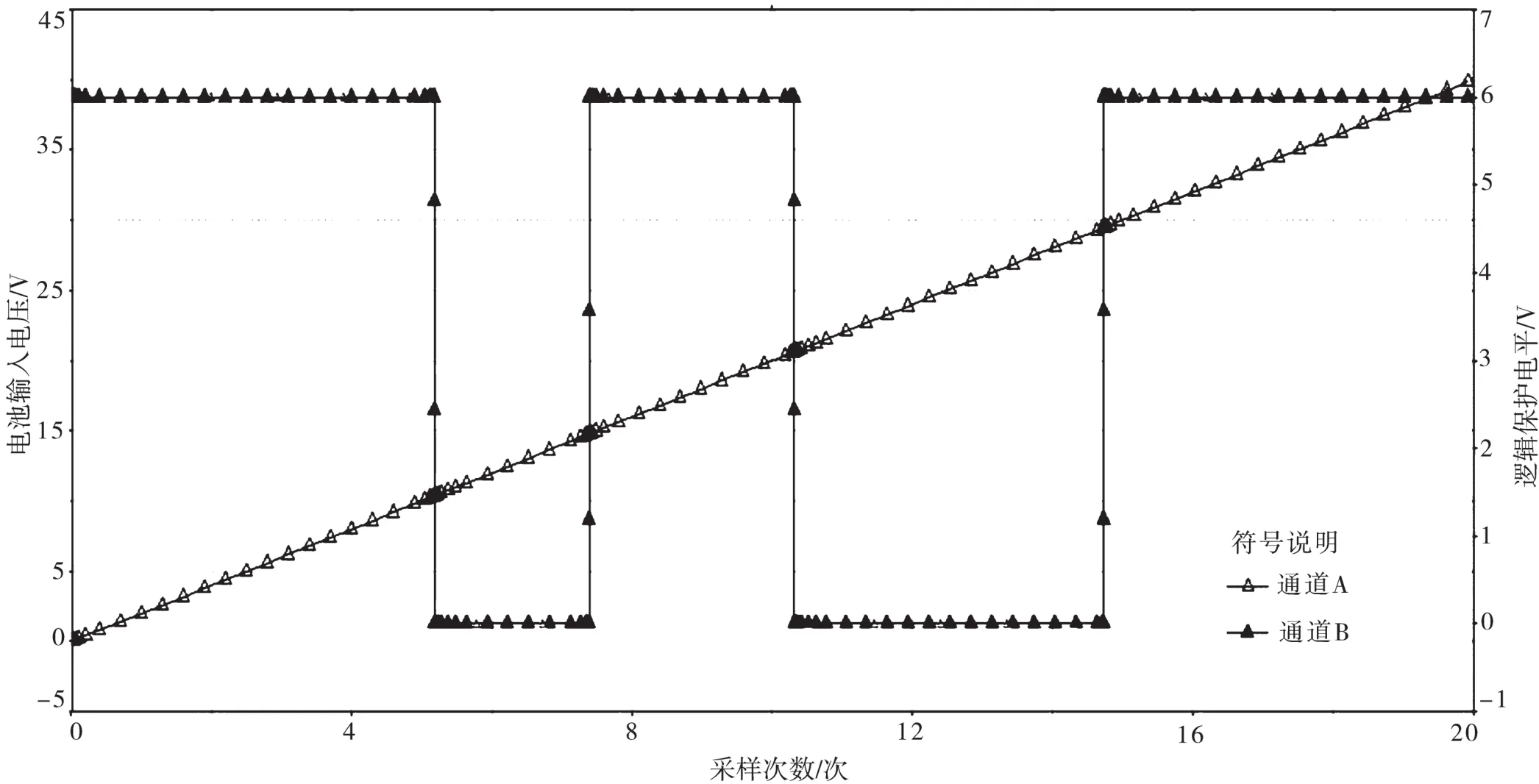

把多級復合型窗口比較器電路方案應用于12 V和24 V兩種不同輸入電壓級別的電子電路,得到如圖8所示的輸入雙電壓級別邏輯保護電路。

如圖8所示,將輸入電壓(V-BAT)的欠壓和過壓采樣分為兩條獨立的分壓式支路。欠壓采樣分壓式支路由圖8中的R1和R2組成,過壓采樣分壓式支路由圖8中的R3和R4組成。在12 V輸入等級下,欠壓及過壓值分別為10.5 V和15 V;在24 V輸入等級下,欠壓及過壓值分別為21 V和30 V。

通過式(2)計算,四個電阻R1、R2、R3、R4可分別取值(計算值應達到或接近標準電阻阻值表內的值)為24kΩ、11kΩ、39kΩ、11kΩ。

兩路分壓式采樣信號分別送入LM339芯片的四個比較器單元A、B、C、D。兩個穩壓二極管(齊納二極管,BZV55-B3V3)串聯組成四個比較器的共用比較基準電壓,其中每個穩壓二極管都并聯了一個容量為10 nF的瓷介電容作為高頻旁路電容,濾除比較基準電壓來自電路內外的干擾信號。因為LM339比較器屬于“開漏”輸出型,所以在每個比較器單元的輸出端加了一個阻值為2kΩ的“上拉”電阻,以確保能輸出正確的狀態[8]。

四個比較器的輸出接到后續的邏輯門電路。因為該CMOS邏輯芯片的工作特性,它工作在5 V模式下,所以在每個比較器的輸出端再加一級分壓電路,使輸入電壓達到該CMOS邏輯芯片的輸入標準。按圖8電路連接,當各個比較器輸出為高電平時,表示輸入電壓在欠壓或過壓狀態;當各個比較器輸出低電平時,表示輸入電壓在合理的工作范圍內。

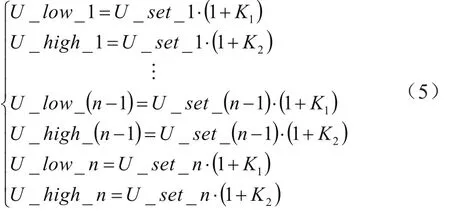

可見,比較器單元A、B的輸出端OA和OB輸出高電平時,分別對應于12 V蓄電池輸入時的過壓與欠壓保護輸出;而比較器單元C、D的輸出端OC和OD輸出高電平時,分別對應于24 V蓄電池輸入時的過壓與欠壓保護輸出。根據這個電路邏輯,畫出電位邏輯保護電路輸出電位的工作示意圖,如圖9所示。

圖9 電位邏輯保護電路的輸出工作示意圖

為了使得邏輯電路的設計更加具體化,使用邏輯運算“卡諾圖”分析法。令OA、OB、OC、OD分別為最高位邏輯、次高位邏輯、次低位邏輯、最低低位邏輯,令“工作狀態”(即電路中的“Control-OUT”)為輸出Y,且使“0 V(低電平)”和“工作”為邏輯電路中的“0”;“5 V(高電平)”和“不工作”為邏輯電路中的“1”。邏輯分析中,無關項用“×”表示。使用邏輯運算“卡諾圖”分析法,可得到電路組合邏輯的最簡式為Y=OA·OD+OB+OC,邏輯分析過程如圖10所示[9]。依邏輯運算式“Y=OA·OD+OB+OC”,設計邏輯運算電路,即圖8右側部分的邏輯電路模塊。

4 仿真和實驗結果

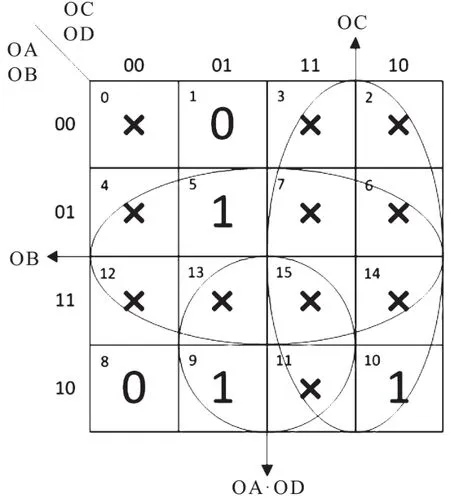

為了驗證電路的可行性,使用Multisim軟件進行仿真。使用軟件中的電壓信號源模擬蓄電池輸入情況,將其輸出調整為波形為等腰三角波、頻率25 MHz、振幅20 V、偏置20 V,即信號為一個在電壓零軸上方的等腰三角波信號,峰值達到40 V。這樣的設置完全可以模擬12 V和24 V蓄電池的過壓、欠壓及正常的工作情況。

示波器的設置:橫軸檔位設置為2 s/div;蓄電池輸入電壓作為A通道輸入,其電壓軸檔位設置為20 V/div;邏輯輸出電壓作為B通道輸入,其電壓檔位設置為5 V/div,作為調試觀察窗口。

仿真結果如圖11所示。示波器窗口中的斜線波形(空心三角線“△”)表示A通道輸入電壓信號(蓄電池輸入電壓);示波器窗口中的折線波形(實心三角線“▲”)表示B通道輸入電壓信號(邏輯輸出電壓)。可見,在仿真中體現出來的電路邏輯與理論上的電路邏輯基本一樣,達到了所謂的電位邏輯判斷功能。

圖10 邏輯分析過程示意圖

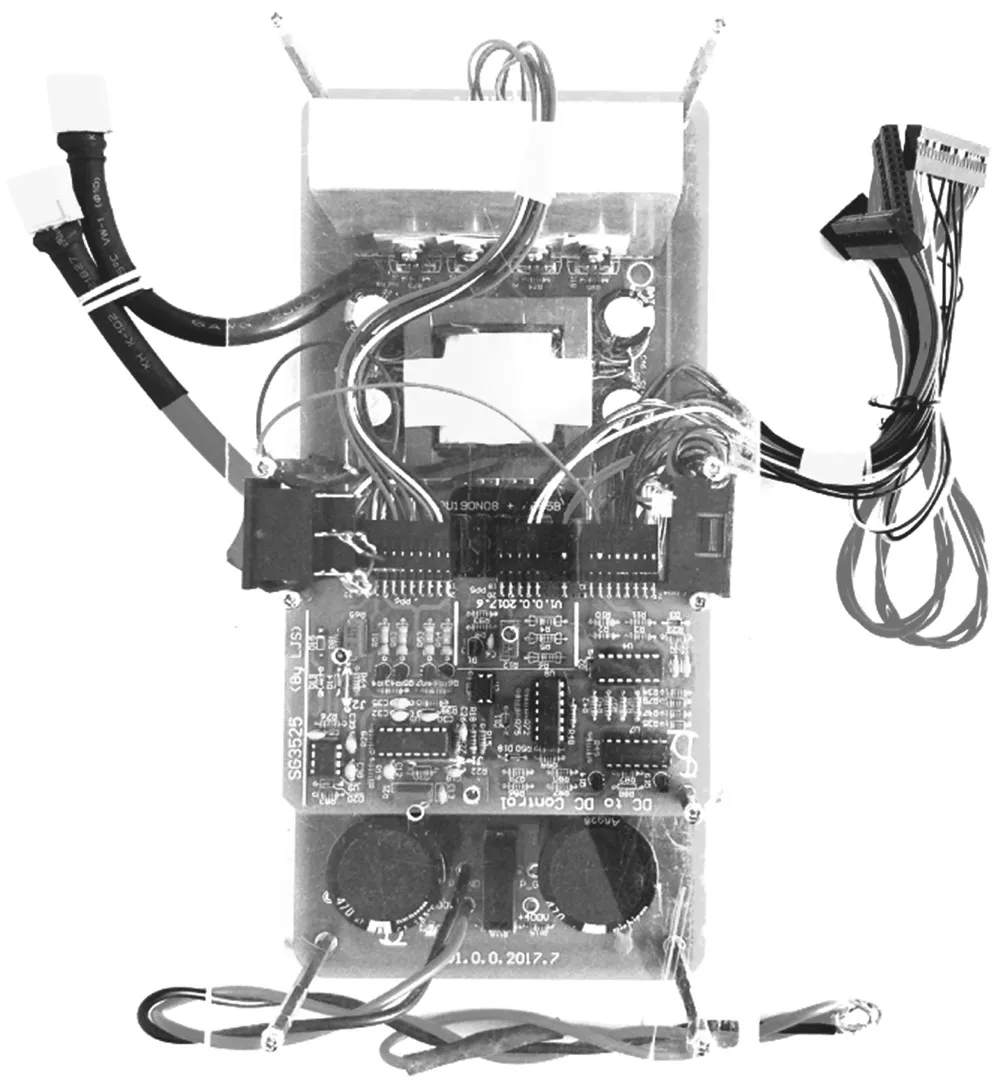

圖8的方案應用到一款5kW逆變器的升壓電路中,該逆變電源系統的輸入為12 V或24 V直流電壓,輸出220 V/50 Hz的正弦交流電,運行正常。電路板實物如圖12所示。

圖11 電位邏輯保護電路的仿真示意圖

5 結 論

基于最簡單的門限電壓窗口比較器電路,在雙級窗口電壓比較器的基礎上,設計了雙級和多級的復合型窗口電壓比較器,并應用到12 V和24 V兩級電壓輸入的狀態檢測與邏輯判斷電路上,通過仿真和實驗驗證了雙級和多級復合型電壓窗口比較器的合理性和實用性。本設計方案針對多級供電電路系統的輸入電壓狀態的檢測與邏輯判斷,是純硬件設計方案,響應快,可靠性高,在長期運行期間不存在軟件程序運行中的“死機”問題,可為實際的相關工程應用提供借鑒。

圖12 逆變器升壓電路板實物