適用于衛星通信的速率自適應型LDPC譯碼器設計

田瑞甫,劉 聚,鐘 鳴,張朝路,侯 俊

(上海航天電子技術研究所,上海 201109)

0 引言

衛星通信信號在傳輸過程中受衰減和噪聲干擾的影響會出現差錯,信道編碼技術作為保證信息可靠傳輸的有效手段被廣泛應用于衛星通信系統[1-2]。LDPC最早由Gallager提出[3],經Mackay等人進一步研究表明[4],LDPC碼的性能在置信傳播(Belief Propagation,BP)譯碼算法下可以接近香農極限,且具有較低的誤碼平臺[5]。準循環LDPC(QC-LDPC)碼,因其校驗矩陣具有準循環性,可以采用簡單的移位寄存器實現具有線性復雜度的編譯碼,硬件復雜度大大降低,是CCSDS推薦的衛星通信糾錯碼型之一[6]。

BP算法涉及較大動態范圍取值的非線性函數的計算,不易于硬件實現[7]。因此,實際應用中通常對BP譯碼算法進行簡化,MMSA被認為是在譯碼性能和實現復雜度間取得較好平衡的一種算法[8-9]。MMSA算法在譯碼處理過程中,所需主時鐘高于輸入數據伴隨時鐘,如果主時鐘由輸入數據伴隨時鐘倍頻后得到,需要通過硬件鎖相環實現,對于不同輸入數據速率的譯碼運算往往需要復雜硬件邏輯和時鐘切換邏輯[10-11]。

根據型號任務需求,設計的LDPC譯碼器采用MMSA譯碼算法實現LDPC譯碼功能,并在此基礎上通過對輸入數據加填充幀和輸出數據伴隨有效性標記位方式,實現了單一主時鐘處理多種速率數據的譯碼運算。

1 MMSA譯碼算法

MMSA譯碼過程是不斷迭代的消息傳遞過程,一般包含4個步驟[12-13]:

① 初始化。設定最大迭代次數,并對每個變量點賦予由信道得到的LLR,作為變量點的內信息。

(1)

式中,Pn為第n個變量節點的信道先驗信息。

② 第t次迭代,變量節點到校驗節點的傳遞信息。

(2)

③ 第t次迭代,校驗節點到變量節點的信息傳遞。

(3)

迭代若干次后,若滿足最大迭代次數,計算后驗概率并判決,否則重復步驟②和步驟③。

④ 計算變量節點的后驗概率并判決輸出。

每個變量節點輸出的后驗概率為:

(4)

根據以下規則對每一個比特進行判決:

(5)

式中,最大后驗概率L(post)(un)為變量節點n的外信息與節點n的初始似然比信息之和。

2 譯碼器結構選擇

QC-LDPC碼的譯碼器結構主要有3種[14-15]:

① 串行譯碼:通過重復使用一個CFU和VFU運算單元來完成所有行(列)運算,占用資源最少,但需要很多個時鐘周期才能完成一次完整的行(列)更新。

② 全并行結構:通過為每一行(列)配置一個運算單元,并使所有的運算單元并行工作來提高運算速度,最少只需要2個時鐘周期就可以完成一次迭代運算,但是需要消耗很多硬件資源,芯片難以支持。

③ 半并行結構:利用QC-LDPC校驗矩陣準循環的特點,可以使用半并行結構,將校驗矩陣劃分成若干個子塊,每個子塊的節點映射成一個硬件處理單元,每次迭代過程中通過重復一個子塊的校驗節點與變量節點運算單元來計算該子塊校驗節點與變量節點的外信息,所有節點的信息更新依次由這一個子塊節點處理單元來完成,這種結構能夠獲得串行和并行的折中。

本文設計基于CCSDS標準(8176,7154)的縮短LDPC碼譯碼器,采用部分并行譯碼結構,根據H矩陣特點,使用2個校驗節點運算單元,16個變量節點運算單元同時運算,即行、列更新運算的并行度分別是2,16,這樣的結構需要511×2或者1 022個時鐘周期才能完成一次迭代運算,數據吞吐量[13]為:

(6)

式中,dnum為信息比特數;fmax為譯碼器的工作時鐘頻率;nc為一次迭代所需周期數;Niter為譯碼器的迭代次數,如果時鐘工作頻率為100 MHz,則譯碼器的吞吐量等于70 Mbps。為簡化時鐘處理邏輯,采用數據吞吐率為0.5,即100 MHz主時鐘處理數據速率50 Mbps。

3 譯碼器設計

譯碼器結構如圖1所示。

輸入數據處理模塊對接收各速率數據做幀同步檢測、跨時鐘域處理和填充空幀。由伴隨時鐘將數據送入FIFO,同時對輸入數據做幀格式檢測,輸入數據格式錯誤則對FIFO做復位處理,格式正確數據送入后續處理模塊。本地時鐘讀取FIFO數據時根據FIFO的空滿狀態添加空幀,以連續數據形式送入后續譯碼模塊,并將數據是否有效狀態量Flag送入輸出數據處理模塊。

圖1 譯碼器結構

輸出數據處理模塊根據式(4)和式(5)對完成迭代譯碼后的數據硬判決后輸出,并根據接收接口處理模塊中FIFO讀取數據的有效性,對輸出數據有效性做標定。

3.1 填充幀處理單元設計

輸入數據處理模塊填充幀處理單元狀態轉移如圖2所示,用于FIFO數據讀取狀態控制。

圖2 填充幀處理單元狀態轉移示意

根據型號任務需求,為適應不同衛星通信工作模式,需要同一譯碼器完成多種速率LDPC譯碼任務。為解決不同速率時復雜時鐘切換邏輯問題,也為后續更多速率譯碼留有升級空間,采用了單一主時鐘加填充幀的處理模式。當輸入數據速率低于處理主時鐘時,添加空幀使核心譯碼模塊處于固定速率連續工作狀態,不需要時鐘切換。

輸入數據處理模塊FIFO的讀取時鐘固定為50 MHz,讀取端根據設置FIFO的滿/空標記讀取或添加填充幀,共3個狀態:初始狀態、讀FIFO數據和填充空數據,狀態標記由Sta表示(Sta=10表示FIFO的滿狀態標記為“1”,空狀態標記為“0”)。

FIFO的讀取標記經延時后送至輸出數據處理模塊,作為數據有效性標記位伴隨輸出(以高電平表示該幀數據有效,低電平表示該幀數據無效)。后續數據處理單機根據伴隨標記位狀態讀取數據。

3.2 變量節點單元設計

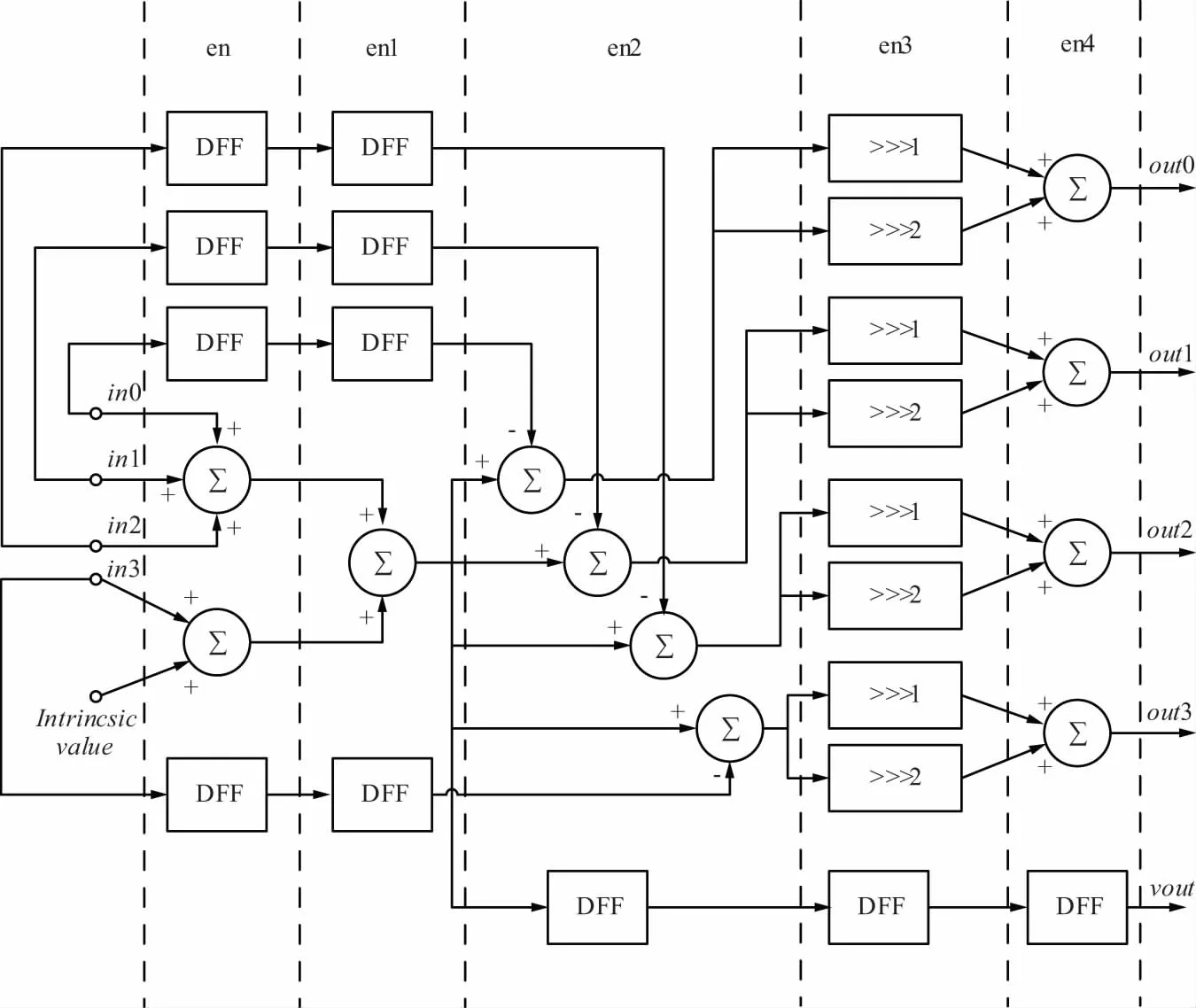

迭代譯碼模塊中變量節點單元結構如圖3所示[13],用于實現變量節點數據更新。

變量節點更新過程又稱為垂直運算,主要實現式(2)內容,作用包括2部分:一部分是更新變量節點消息,送至迭代信息存儲器用于給校驗節點進行下一次迭代;另一部分(vout)是更新后驗概率消息,該消息主要用于硬判決。

變量節點單元工作流程為:從每個信道初始信息存儲器中讀出一個信道似然比(LLR)信息。同時,根據地址從4個迭代信息存儲器中讀出4個校驗節點信息。變量節點單元通過對由迭代信息存儲器中讀出的校驗節點信息和LLR信息進行垂直運算,得到新的變量節點信息。最后,將新的變量節點信息按讀地址寫回到各迭代信息存儲器中,完成置信度信息更新。完成一次迭代的垂直運算需要對這個過程重復10次。

垂直運算過程采用5級流水線方式,完成算法中變量節點到校驗節點的計算,其中式(2)的factor取0.75[8],只要進行移位相加就能實現。

圖3 變量節點單元結構

圖3中的in0,in1,in2,in3是在Tanner圖中與一個變量節點相連的4個校驗節點更新后的信息。IntrinsicValue是變量節點的初始化信息。out0~out3是4個變量節點進行更新之后的信息。vout是內信息和4個輸入信息的和,通過檢查該信息的最高位來判決。

3.3 校驗節點單元設計

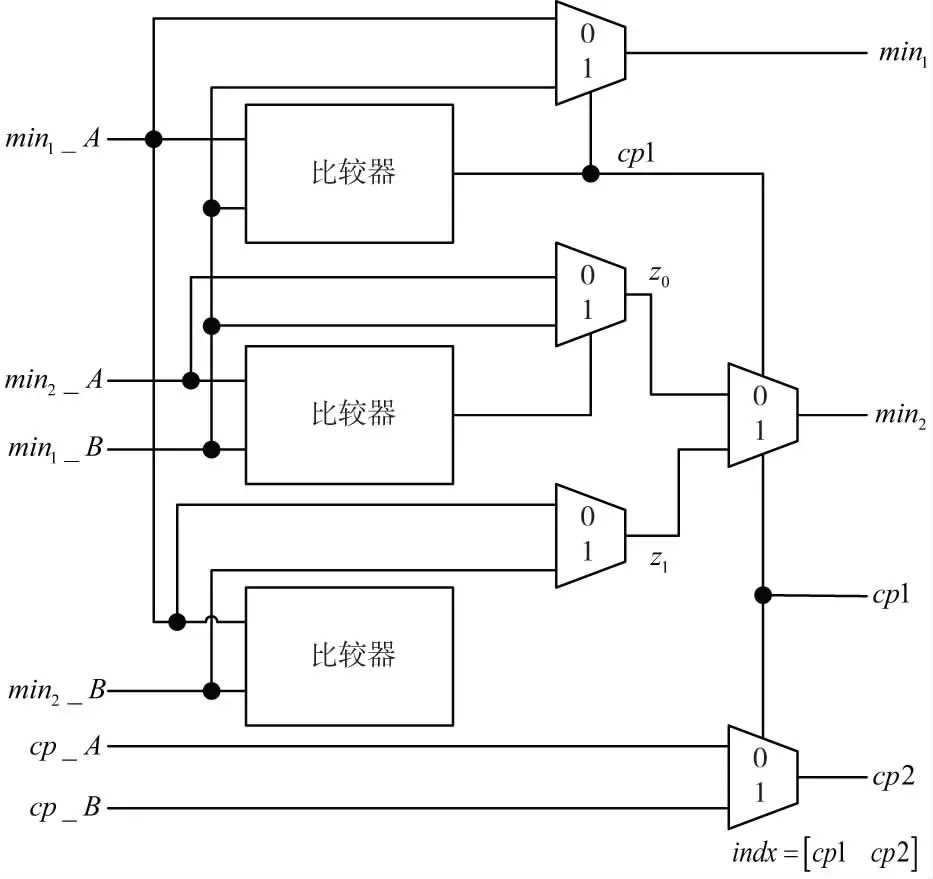

迭代譯碼模塊中校驗節點單元結構如圖4所示[12],用于實現校驗節點數據更新。

圖4 校驗節點單元結構

校驗節點處理單元主要實現式(3),用來完成校驗節點消息的更新,其更新過程稱為水平運算,是迭代過程的一部分,進行的操作主要是使譯碼器對每個行塊的第i行做行置信度信息更新運算。

其工作流程為:每個校驗節點從32個迭代信息存儲器中讀出32個變量節點消息。由于32個存儲器的讀地址均為i,因此這一步操作只需要計數器就能實現信息的讀取。然后,32個變量節點信息讀出后直接送給該校驗節點單元進行信息更新運算,得到新的校驗節點信息。最后,將新的校驗節點信息按讀地址寫回到各迭代信息存儲器中,完成校驗節點信息更新。完成一次迭代的水平運算,即校驗節點信息更新運算,需要對這個過程重復10次。

在修正最小和算法中,校驗節點處理模塊需要完成的工作是求出與一個校驗節點相連接各變量節點數據(除自身外)絕對值的最小值。如果當前節點的值為最小值,則輸出為其他所有值中的最小值,即次最小值。求各數據符號值的乘積,將所得最小值與符號值合并成新數據。

圖4所示結構圖主要實現功能:

(7)

各符號的乘積可以通過查找表的方式得到。

3.4 控制單元設計

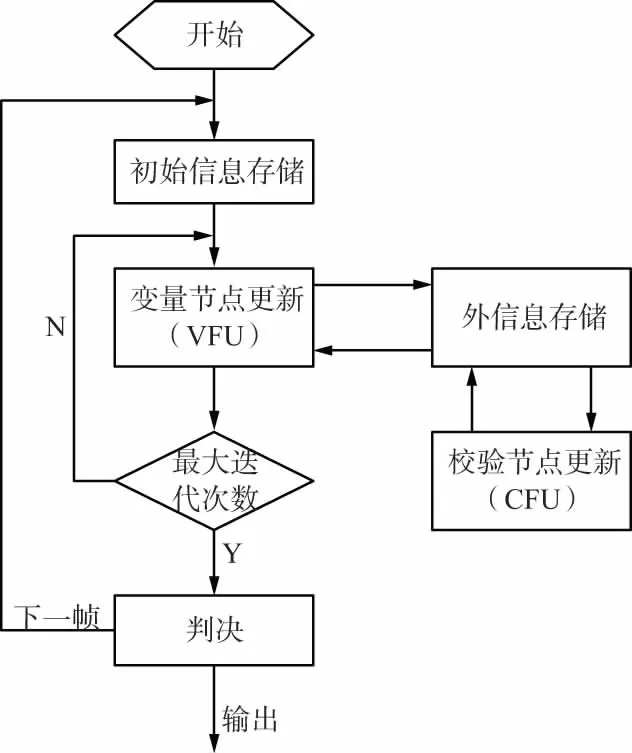

迭代譯碼模塊中控制單元流程如圖5所示,用于各單元工作協調控制。

圖5 控制單元流程

迭代譯碼模塊的工作流程[16]如下:

① 總狀態機控制初始信息存儲單元的一組RAM,該組RAM寫使能有效,接收來自信道的信息,當一幀數據全部存儲后,切換到另一組RAM存儲下一幀數據,同時返還給總控一個信號。

② 控制單元在一幀數據存儲結束后,使能VFU模塊,并使能初始化存儲單元讀取功能,進行變量節點更新運算,運算結果寫入外信息存儲模塊。

③ VFU運算完成后,VFU單元給總控發送結束信號,總控屏蔽VFU和初始化存儲單元,啟動CFU的運算。CFU從外信息存儲單元讀取信息,并將運算結果寫入、讀出地址相同位置中。

④ CFU運算結束后,CFU單元給總控發送結束信號,總控屏蔽CFU單元,啟動VFU單元和初始化存儲單元,VFU單元和CFU單元交替運算。

⑤ 經過10次迭代運算后,進行硬判決,對判決數據做有效性標記并輸出,開始下一幀數據迭代譯碼。

4 譯碼器實現

基于前文設計思想,采用VHDL語言編寫,ISE14.7編譯環境,在Xilinx公司Virtex-4系列FPGA芯片XC4VSX55上實現了CCSDS規定的縮短(8176,7154)準循環LDPC譯碼器。譯碼器的邏輯資源和存儲資源利用情況如表1所示。

表1 譯碼器資源利用率

資源類別數目占總資源百分比/%Slice Flip-Flops14 25429Slice LUT15 47031Bonded IOBs112Block RAM/FIFO13140

譯碼器設計實現后,需要對其進行測試,以驗證其糾錯性能[17]。譯碼器測試原理如圖6所示。

圖6 譯碼器測試原理

測試步驟如下:

① 碼源產生PN15偽隨機數據,按CCSDS標準組幀;

② 在數傳發射機內進行LDPC編碼和QPSK調制;

③ 射頻信號通過下變頻器到中頻信號,并在中頻加噪聲;

④ 在接收機內進行QPSK解調[18],并標定輸出Eb/N0值;

⑤ LDPC譯碼,分別比對譯碼前后對應誤碼率。

分別在50,30,20,10,2,1 Mbps速率下進行了測試,不同速率下譯碼性能測試結果一致,如表2所示。

表2 譯碼性能測試結果

解調后(Eb/N0)/dB譯碼前BER/bit譯碼后BER/bit12.40011.91.56?10-70102.12?10-505.85.82?10-305.48.14?10-31.26?10-7

測試結果顯示,設計的譯碼器在BER為1×10-7量級有6.5 dB增益。

5 結束語

以航天型號為基礎,采用MMSA譯碼算法對CCSDS標準推薦的縮短LDPC碼實現譯碼功能的基礎上,通過對輸入數據加填充幀和輸出數據伴隨有效性標記位的方式,實現單一主時鐘處理不同速率數據功能。通過對輸入數據格式判斷和復位處理相結合,使譯碼器具有接收錯誤數據后自恢復功能。實驗結果表明,譯碼器在BER為1×10-7量級有6.5 dB增益,且在不高于50 Mbps速率條件下可以速率自適應。