基于淘汰判決的跳頻同步捕獲方案設計

趙祥武,全厚德,崔佩璋

(陸軍工程大學石家莊校區 電子與光學工程系,河北 石家莊 050003)

0 引言

同步技術是跳頻系統的關鍵,傳統同步方案一般都利用跳頻同步引導碼完成跳頻同步的工作,隨著電子通信的不斷發展,敵方干擾越來越“聰明”,干擾方可以通過捕獲一些跳頻的通信參數來進行更為精確的干擾,比如跟蹤干擾,干擾方在干擾一段時間之后,可以通過分析得到信號時頻域的特征信息,從而精確干擾,使得跳頻通信無法正常進行。

高跳速下通信系統的同步技術是同步技術發展方向之一。文獻[1]提到,目前高跳速電臺應用較多的是時間信息(Time of Day,TOD)和同步頭聯合應用的一種策略,該方法是跳頻信號前端將時間信息填入,方便進行同步識別,接收機通過將接收到信息進行捕獲,從而調節偽隨機碼發生器,完成信息的正常通信。由于這種策略一旦被敵方發現,很難進行通信。文獻[2]提出了門限比較的同步策略,在高速的跳頻通信中具有性能的優勢。隨著跳頻通信發展,差分跳頻作為抗干擾較好的通信方式,是今后重要的發展方向。同步性能也直接影響差分跳頻的系統。文獻[3]中,同步技術主要使用的是信號的FFT檢測,該方法是對數字信號進行FFT的時頻分析,根據跳頻信號能量的遍布情況,從而得到跳頻同步信息,完成同步過程。文獻[4]提到跳擴混合系統的關鍵是跳頻同步和快速實現擴頻序列的捕獲。該方法是基于時間信息與同步頭的直接序列擴頻編碼方法,可以很好地增強同步方法應對干擾的能力。文獻[5]提到一種基于滑動相關的自適應同步捕獲策略,可以迅速完成正常通信。

跳頻同步主要包括3個方面:同步捕獲、同步跟蹤以及同步保持[6]。同步捕獲是一個粗略的同步過程,也是最需要首先解決的問題,主要解決的問題是收發兩端時間誤差控制在一個允許的范圍內,一般取1/2跳頻序列的相位;同步跟蹤是一個精確同步的過程,使接收端與發射端的時間誤差在原來捕獲的基礎上再盡可能縮小,更細小的相位差的修正需要同步跟蹤來完成。跳頻通信系統中同步跟蹤方法是通過鎖相環技術來實現的,常見的跟蹤過程方法有2種:基于抖動鎖相環和基于延遲鎖相環[7-9]。

本文主要對自同步方法中串行同步捕獲方案和并行同步捕獲方案進行具體的研究分析,針對2種同步捕獲方案的性能優缺點,提出了基于淘汰判決的同步捕獲方案,通過在一定范圍內的能量檢測,快速進行同步判決,節省了同步捕獲時間,增強了抗干擾能力。

1 跳頻同步捕獲方案

1.1 串行自同步捕獲方案

跳頻通信系統串行搜索捕獲方案的原理框圖如圖1所示[10]。工作原理是:基于發射端跳頻信號與接收端本地偽隨機發生器的頻率進行相關運算,而后對一個跳頻周期內的判決結果作能量比較,根據提前設置的門限電平,如果相關運算后的門限電平沒有超過輸出電平,這代表著收發兩端沒有同步,此時搜索控制器控制PN碼發生器相位移動,重新進行相關運算;反之,超過輸出電平,收發兩端已經同步捕獲,進而進行同步跟蹤,進一步縮小誤差。

圖1 跳頻系統串行捕獲原理框圖

1.2 并行自同步捕獲方案

跳頻通信系統并行搜索捕獲方案的原理框圖如圖2所示[11-12]。工作原理是:發射端的跳頻信號與接收端信號相關運算后,經過平方檢波器,而后進行能量相加求和。如果能量和大于規定的門限電平,就意味著收發兩端已經同步。其中,Th是跳頻周期,n代表跳頻同步的頻率數。圖2可以看出,S條支路的中心頻率按照f1,f2,f3,...,fn的順序排列,其順序應與同步引導碼的順序一致。跳頻圖案按照f1~fn的順序進行跳變,經過平方檢波后依次延遲一個跳頻周期;當輸入的跳頻頻率fn進入接收機時,對加法器累加的能量值輸出門限判決。如果輸出門限值超過規定的門限,即可實現跳頻的同步。

圖2 跳頻系統并行捕獲原理框圖

從理論上分析,并行自同步捕獲方案在捕獲時間上較串行自同步捕獲方案有很大的優勢,就系統復雜度來說,串行自同步捕獲方案較為簡單。

1.3 基于淘汰判決的自同步捕獲方案

圖3為淘汰判決自同步捕獲系統框圖。該方案的中心思想是同步過程中在Q個頻點內通過門限判決結果快速做出相應的處理,如果在Q個頻點內相關的能量檢測結果明顯小于規定門限值,意味著跳頻信號沒有同步,直接將接收機本地跳頻信號序列淘汰,經過跳頻序列相位移動后,再開始同步,經過混頻、濾波及門限判決等一系列操作,然后再進行出局判決,跟并行自同步捕獲方案一樣,一個跳頻周期內的相關判決直接決定著同步是否成功。

圖3 淘汰判決自同步捕獲系統框圖

2 性能分析

2.1 系統復雜度

就系統復雜度而言,根據3種捕獲方案的設計模型可以很清晰地看出:串行自同步捕獲方案只需一路由混頻、帶通濾波、包絡檢波以及門限判決模塊構成的支路,而并行自同步捕獲方案則需S路相關支路,所以相比于并行自同步捕獲方案,串行自同步捕獲方案系統設計簡單,得到很好的應用而淘汰判決的自同步捕獲方案,相較于串行自同步捕獲方案,只是快速淘汰判決模塊以及搜索控制模塊,系統復雜度不高[13]。

2.2 抗干擾性能

假定跳頻序列進行同步需要n個不同頻率,即跳頻序列長度是n,跳頻頻率間隔為T0,假設捕獲方案在第k頻點實現同步捕獲。

并行自同步捕獲方案捕獲成功的概率表示為:

(1)

串行自同步捕獲方案捕獲成功的概率表示為:

(2)

在無干擾存在時,基于淘汰判決捕獲方案捕獲成功的概率表示為:

(3)

就抗干擾性能而言,串行自同步捕獲方案和并行自同步捕獲方案都是對于一個周期內的相關檢測結果進行門限判決,對于使用相同長度的跳頻序列,判決門限相同時,2種方法抗干擾性能相同,都具有很好的抗干擾能力。

抗干擾性的主要指標是虛警概率和漏捕概率,淘汰判決自同步方案是根據淘汰判決模塊的控制,跟串行自同步捕獲方案比較,不會增加虛警概率。所以,重點研究該同步方案的漏捕概率。本節選擇的干擾模型為單頻干擾,假設存在F=αn個單頻干擾,定義每個頻點的出現干擾概率為α。假定在某頻率間隔內,檢測到幅度為A的有用跳頻信號,干擾幅度為Ai,A與Ai之間的夾角為θ,而且θ均勻分布在[0,2Π]上,則有用信號與干擾信號的幅度可以寫為:

(4)

在相關檢測后,判決門限電平為A1,此時如果A1>Av,就會造成頻率漏捕,即

(5)

此時可以得到頻點的漏檢概率:

(6)

如果存在R個以上的跳頻頻點出現漏檢時,同步方案漏檢的概率為:

(7)

經過以上分析可知,淘汰判決自同步捕獲方案和串行自同步捕獲方案相比,判決模塊會出現錯誤判決,從而使得漏檢概率增加,需要對Q取值大小進行約束。

當連續漏檢的頻點數目是Q時,總的漏檢個數小于R的概率為:

(8)

當連續漏檢的頻點數目是Q+1時,總的漏檢個數小于R的概率為:

(9)

當連續漏檢的頻點數目是Q時,系統漏捕獲概率為δQ=1/n;

當連續漏檢的頻點數目是Q+1時,系統漏捕獲概率為δQ+1=2/n。相較于串行自同步捕獲方案,淘汰判決自同步捕獲方案的漏捕概率增量為:

(10)

2.3 平均捕獲期望

串行捕獲方案捕獲時間的期望[14]:

(11)

并行捕獲方案捕獲時間的期望[15]:

(12)

基于淘汰判決的捕獲方案捕獲時間的期望:

(13)

根據式(11)~式(13)分析可知,基于淘汰判決的自同步方案捕獲時間期望遠遠不及串行自同步捕獲方案的捕獲時間期望,同時,僅當依據對一個頻點能否進行同步捕獲而進行相位判決時,即當Q=1時,淘汰判決自同步方案的捕獲時間與并行自同步捕獲方案相同,使得捕獲時間最小。

3 仿真結果分析

3.1 捕獲時間仿真分析

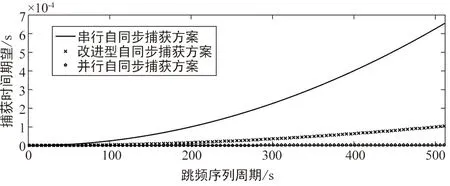

考慮在無干擾環境中,設定Q=0.3n,跳頻長度n取值范圍為0~512,通過Matlab仿真計算,得到串行自同步捕獲方案、并行自同步捕獲方案和淘汰判決自同步捕獲方案。3種方案捕獲時間期望的對比曲線如圖4所示。

從圖4的仿真結果可以看出,淘汰判決自同步捕獲方案的捕獲時間相比于串行自同步捕獲方案的捕獲時間有了較高的提升,在Q=0.3n時,捕獲時間約為串行自同步捕獲方案的1/5。

圖4 改進方法與經典方法的性能對比曲線

3.2 參數Q的大小對捕獲性能的影響分析

在n=256,α=0.2,P=0.15的取值狀態下,設定R=n·(α+P)/2,漏捕概率增量與Q的仿真結果如圖5所示,其中Q的取值大小設定(0.5R,R)。

從圖5中可以看出,淘汰判決自同步捕獲方案的漏捕概率增量僅僅是10~11數量級,當Q/R≥0.66時,漏捕概率增量達到最小,在實際的跳頻電臺中可以忽略,參數Q的大小主要是由捕獲時間以及抗干擾性進行綜合選擇。Q過大時捕獲時間增加,Q過小時抗干擾性能不達標。通過多次計算機仿真結果,當參數取Q=0.66R左右時,跳頻通信具有很高的抗干擾性能,同時也滿足捕獲時間的要求。

圖5 漏捕獲概率增加量與Q值的關系曲線

4 結束語

從系統復雜度、捕獲時間以及抗干擾性能這3個方面對串行自同步捕獲方案、并行自同步捕獲方案和基于淘汰判決自同步捕獲方案進行了詳細的分析與對比,串行自同步捕獲方案捕獲時間最長,并行自同步捕獲方案捕獲時間最短,串行與并行自同步捕獲方案的抗干擾性能相同,在一定條件下優于淘汰判決自同步方案。但是,當淘汰判決自同步捕獲方案取得適當的淘汰參數Q時,既可以保證抗干擾性能,也能保證捕獲時間的最佳。