無線體溫監測系統EMC問題分析及整改

黃二亮 卜祥磊 唐勇 葉鳳章 黃鑫

摘要:我們設計的無線體溫監測系統由于在開發設計時產品的設計、布局出現了問題,產生了電磁干擾(EMI),造成了電磁兼容性(EMC)問題。我們基于系統電路原理圖,從PCB布局布線設計等方面優化晶振和時鐘信號匹配電路,并介紹如何解決EMI干擾,避免EMC問題。

關鍵詞:體溫監測系統;無線;EMC;EMI;匹配電阻;去耦電容

中圖分類號:TNO 文獻標識碼:A 文章編號:1007-9416(2019)04-0173-03

0 引言

基于公共無線頻道通訊協議的無線體溫監測系統在產品設計時由于晶振、時鐘信號布線和設計問題而產生了電磁干擾(Electromagnetic Interference,EMI),在PCB線路中,晶振是一個輻射發射源,是產生和導致電磁兼容性(Electro Magnetic Compatibility,EMC)問題的關鍵因素之一,時鐘信號無匹配電路設計也是造成EMI干擾的主要原因[1]。為解決因在產品設計、布局時造成的EMI干擾問題,本文分析了無線體溫監測系統產生EMC問題的主要原因,提出了從電路原理圖設計方面來解決EMC的原理及方案。在其它產品設計、布局時,如有晶振、時鐘信號的線路設計布局時,此方案措施也能很好的幫助其解決因此類問題造成的EMC問題和EMI干擾。

1 現象描述

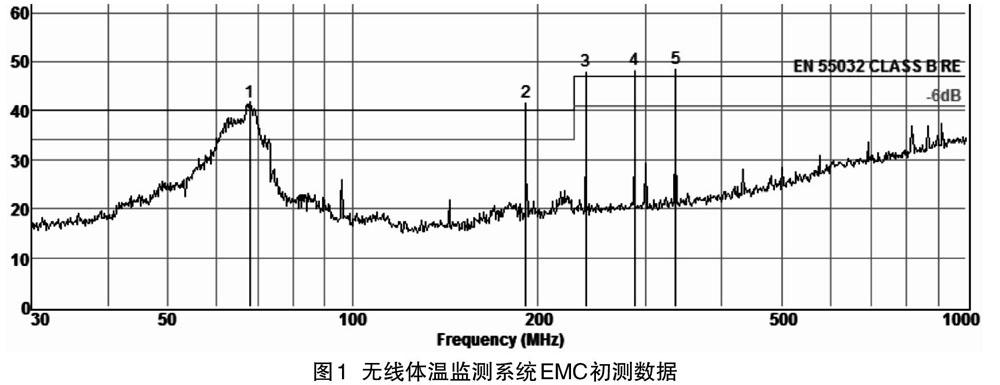

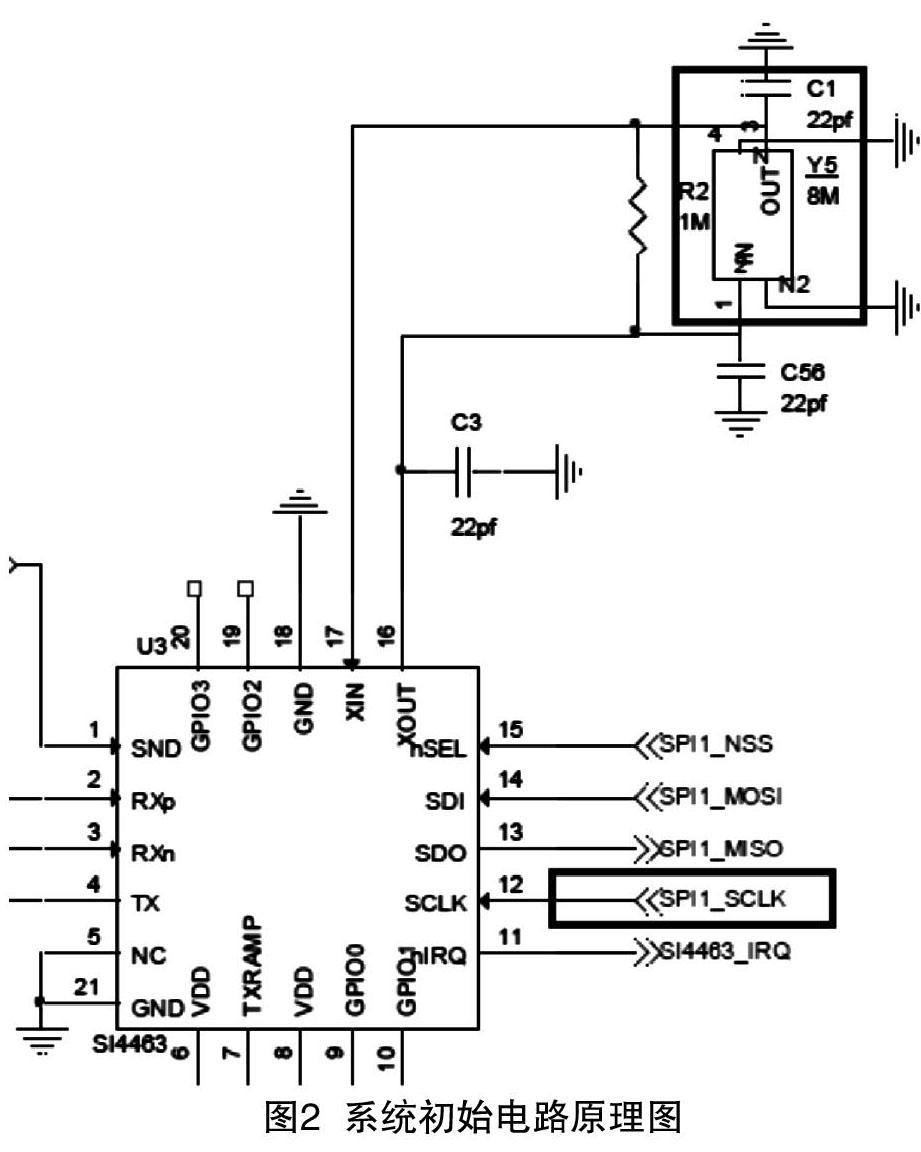

基于公共無線頻道通訊協議的無線體溫監測系統在進行EMC空間輻射測試時因產品本身設計原因產生了電磁干擾,如圖1所示是系統最初的空間輻射測試數據,根據測試數據可以看出電磁干擾頻率主要為USB數據轉換芯片8MHz振蕩晶振的諧波倍頻。從電路原理圖圖2分析,輻射干擾源可能會是由USB數據轉換芯片的Y5晶振振蕩器及SPI1_SCLK時鐘信號與主控芯片之間通信造成EMC問題,產生EMI電磁干擾。

2 原因分析

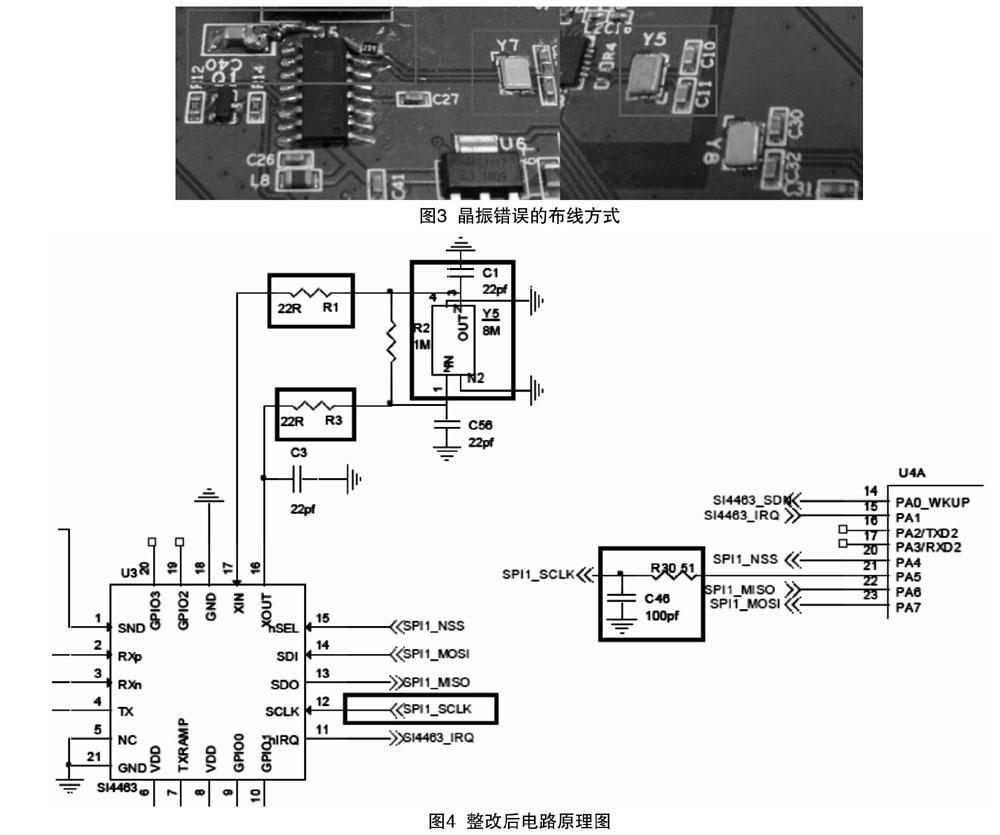

整改過程中檢查PCB線路布局發現時鐘信號電路與主控芯片IC之間通信沒有匹配電阻和去耦電容的線路,Y7、Y5兩個 8MHz振蕩晶振輸入、輸出線是從晶振下方通過,如圖3所示。在晶振振蕩系統開始工作后,從晶振下方經過的信號線會產生高頻諧振,從而導致EMC問題,產生EMI干擾,也是造成空間輻射測試不能通過的主要原因。

從電路原理圖中可以看出,USB 數據轉換芯片的晶振振蕩部分電路雖然有去耦電容,但沒有匹配電阻;時鐘信號電路與主控芯片IC之間通信沒有匹配電阻和去耦電容的電路設計。結合測試數據及結果分析,晶振部分電路及時鐘信號電路在電路設計上沒有完整的匹配措施;同時,晶振及其相應時鐘信號由于其周期特性,會因時鐘邊沿速率過快引起信號完整性和電磁兼容等問題,成為PCB的主要騷擾源,并產生較多諧波干擾,導致空間輻射測試超標。

通常情況下,當PCB電路設計中有晶振及時鐘信號電路時,晶振線路布線設計時是否增加匹配電阻和去耦電容,或只加了去耦電容未加匹配電阻,以及時鐘信號線上是否有增加匹配電阻及去耦電容對產生EMC問題,造成EMI干擾有非常大的影響。

匹配電阻在電路設計中主要有以下兩個作用:

(1)阻抗匹配:因PCB上的布線含有一定的阻抗,會因布線問題產生阻抗失配,引發信號的完整性產生電磁干擾,即一般會采用源端串聯一電阻的方式進行匹配來保證信號的質量[2]。

(2)減緩信號上升沿:匹配電阻R與電容C是一個RC低通濾波電路:

為反映信號響應速度的量t,其t值影響信號響應速度,從而影響高頻干擾。匹配電阻的取值最好在20~100歐之間,也可在確保信號質量的前提下其值越大越好。

去耦電容主要應用于信號電路設計中,完成去耦、振蕩/同步及時間常數的作用[3]:

(1)去耦:去耦電容是利用晶體管放大器的發射極通常含有自給偏壓電阻,使信號產生的壓降反饋到輸入端形成了輸入輸出信號去耦。如果在這個電阻兩端并聯一個適當容量的電容,該電容對交流信號較小的阻抗就可以減小了電阻產生的去耦效應。

(2)振蕩/同步:包括RC振蕩器、LC振蕩器及晶體的負載電容。

(3)時間常數(t):是指電阻R和電容C串聯構成積分電路,當輸入信號電壓V作用在輸入端時,電容C上的電壓逐漸上升。積分電路的充電電流I伴隨著電壓的上升而減小。電流I通過電阻和電容的特性通過下面的公式描述(其中e為自然常數):

在PCB布局設計時,若要保證時鐘電路有足夠的去耦電容,就必須保證去耦電容的選取要滿足預期的應用。自諧振頻率需要考慮抑制時鐘的諧波,通常我們都要考慮原始時鐘頻率的五次諧波。同時在高頻電路中會因回路電感的影響,需要在PCB上放置有效容性的去耦電容來達到良好的去耦效果。在實際應用中通常采用大電容濾低頻,小電容濾高頻的原則來選取去耦電容值。

3 改進措施

對無線體溫監測系統的EMC問題整改分析,我們在產品設計時應當注意以下幾點:

(1)將晶振布局位置盡量靠近芯片IC,匹配電路設計置于晶振和芯片IC之間。

(2)時鐘信號增加匹配電阻、去耦電容,晶振的輸入、輸出引腳串聯匹配電阻。

(3)晶振附近及晶振下不能有信號線、電源線等布線,以免發生干擾。

依據以上分析,線路設計中USB數據轉換芯片的振蕩晶振部分電路只有去耦電容,沒有匹配電阻。因此,我們首先在晶振的輸入、輸出引腳分別串聯22歐電阻。經測試系統有明顯改善,但仍不能通過測試。按上述思路分析,USB數據轉換芯片的SPI1_SCLK引腳與主控芯片之間沒有匹配電阻和去耦電容,可能會因此產生諧振,造成諧波干擾。在USB數據轉換芯片的SPI1_SCLK引腳與主控芯片之間串匹配R30位置51歐電阻,如圖4所示,同時增加C46位置100pF的去耦電容對地后,系統可以通過測試。

系統電路增加了整改措施,調整了PCB布局,重新進行PCB布線設計,得到整改后的無線體溫監測系統。再次進行EMC空間輻射測試,系統電路解決了EMI干擾問題,通過了EMC測試,測試數據如圖5所示。

4 結語

經過以上整改測試可以看出,在線路設計時,通常可以在晶振的輸入、輸出引腳增加去耦電容的同時預留匹配電阻調試位置,在時鐘信號電路預留匹配電阻和去耦電容的RC低通濾波電路位置。當EMC測試出現問題時,可以適當調節匹配電阻值和去耦電容值來改善系統電路電磁兼容性問題,降低輻射干擾。還可在不影響新產品功能、性能的前題下可將匹配電阻改為高頻磁珠來達到改善EMI干擾的目的。

綜上所述,本文從線路設計及晶振、時鐘信號造成EMI干擾的原理、匹配電阻與去耦電容的作用等方面闡述了無線體溫監測系統因晶振、時鐘信號引起的EMC問題及如何從線路布局、線路設計上去解決因此而造成EMI干擾的解決方案,也可運用此方案解決其它帶有晶振和時鐘信號產品的EMC問題。

參考文獻

[1] 張亮.電磁兼容(EMC)技術及應用實例詳解[M].電子工業出版社,2014.

[2] 孔今.EMC設計開發內參資料[M].電磁兼容工程師論壇,2017.

[3] 鄭軍奇.EMC電磁兼容設計與測試案例分析[M].電子工業出版社,2010.