基于FPGA的變M/T歸一化測速算法研究

李小闖 于 強

1(中國科學(xué)院國家空間科學(xué)中心 北京 100190)2(中國科學(xué)院大學(xué) 北京 100049)

0 引 言

在我國空間材料科學(xué)實驗的研究中,傳動結(jié)構(gòu)往往基于步進電機進行;步進電機雖然控制方式較為簡單,但往往難以獲得較大的轉(zhuǎn)矩,而隨著實驗樣品體積的增大,步進電機逐漸難以滿足實驗需求。而永磁同步電機雖然控制較為復(fù)雜,但因其良好的轉(zhuǎn)矩特性使其擁有更好的應(yīng)用前景。在空間材料科學(xué)實驗中,對樣品的移動速度及準確定位要求十分嚴格,這也對永磁同步電機的速度控制提出了較高的要求。傳統(tǒng)的M/T測速法雖然能夠有效地對電機轉(zhuǎn)速進行測量,但其在低速范圍的實時性較差。而在空間材料科學(xué)實驗中樣品的移動速度跨度范圍較大(5 mm/天~2 mm/min),因此對M/T測速算法的改進勢在必行。

本文針對永磁同步電機的測速問題,結(jié)合FPGA特性,提出一種基于FPGA的變M/T的歸一化測速算法,從而在保持傳統(tǒng)M/T測速精度的同時,改善測速的實時性。同時歸一化的設(shè)計思路能夠使得系統(tǒng)能夠適用于任何基于增量編碼器的永磁同步電機測速環(huán)境。針對設(shè)計中所需要的乘除運算,引入Booth算法以降低設(shè)計對DSP的需求。

1 增量編碼器工作原理

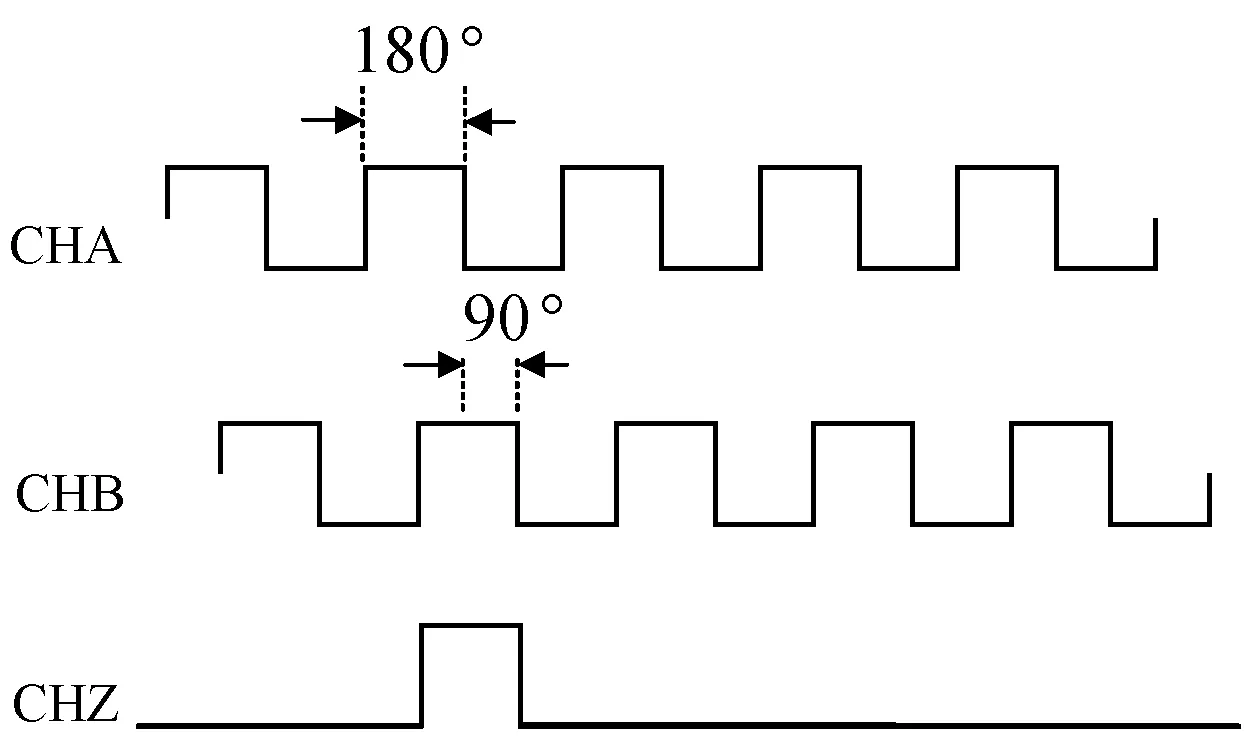

永磁同步電機轉(zhuǎn)速測量依靠在轉(zhuǎn)子上安裝的增量編碼器進行速度檢測。增量編碼器采用光電轉(zhuǎn)換原理,輸出兩相正交脈沖信號A、B與一路零相信號Z:A、B兩相相差90°,若A相超前B相,則電機處于正轉(zhuǎn),否則處于反轉(zhuǎn);電機旋轉(zhuǎn)一圈零相信號Z輸出一個脈沖。增量編碼器輸出時序如圖1所示[1]。

圖1 增量編碼器時序圖

2 測速算法原理

2.1 M/T測速算法原理

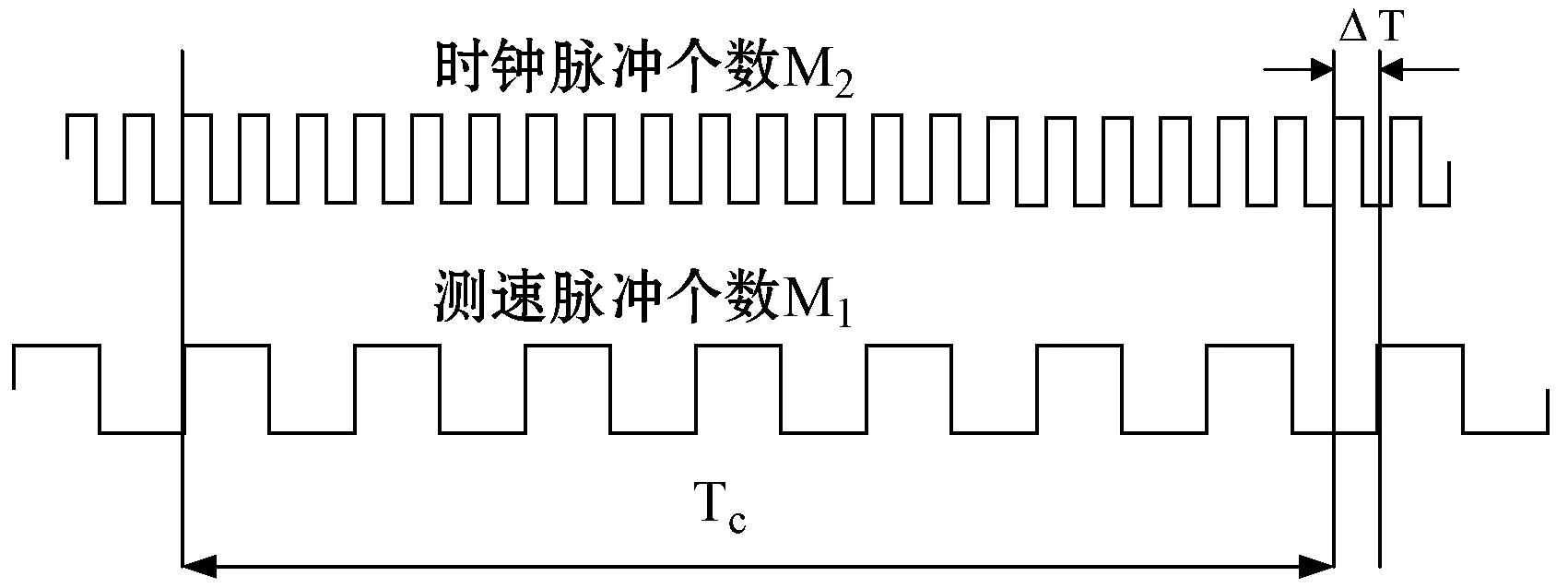

M/T法測速原理是M法(頻率法)和T法(周期法)的結(jié)合,其方式為在一定時間范圍內(nèi),同時對光電編碼器輸出脈沖個數(shù)M1和捕獲時鐘的個數(shù)M2進行計數(shù),用M2計算出的時間替代定時器的時間進行轉(zhuǎn)速的計算[1]。其測速原理如圖2所示。

圖2 M/T測速算法測速原理

假設(shè)時鐘脈沖頻率為fclk,編碼器分辨率為N,M1為時間Tc內(nèi)編碼器脈沖計數(shù),M2為時間Tc內(nèi)高頻時鐘周期計數(shù),則轉(zhuǎn)子的轉(zhuǎn)速v(單位:r/min)可表示為:

(1)

在進行計數(shù)過程中,由于檢測時鐘脈沖計數(shù)可能出現(xiàn)±1個脈沖誤差[2],因此M/T法測得電機轉(zhuǎn)速誤差Δv為:

(2)

相對誤差為:

(3)

2.2 歸一化

歸一化也稱標幺化。歸一值(標幺值)是電力系統(tǒng)分析和工程計算中常用的數(shù)值標記方法,表示各物理量及參數(shù)的相對值,單位為pu(也可以認為其為無量綱)[3]。歸一化是相對于某一基準值而言的。同一有名值,選取基準不同,其歸一值也不同,其關(guān)系如下:

(4)

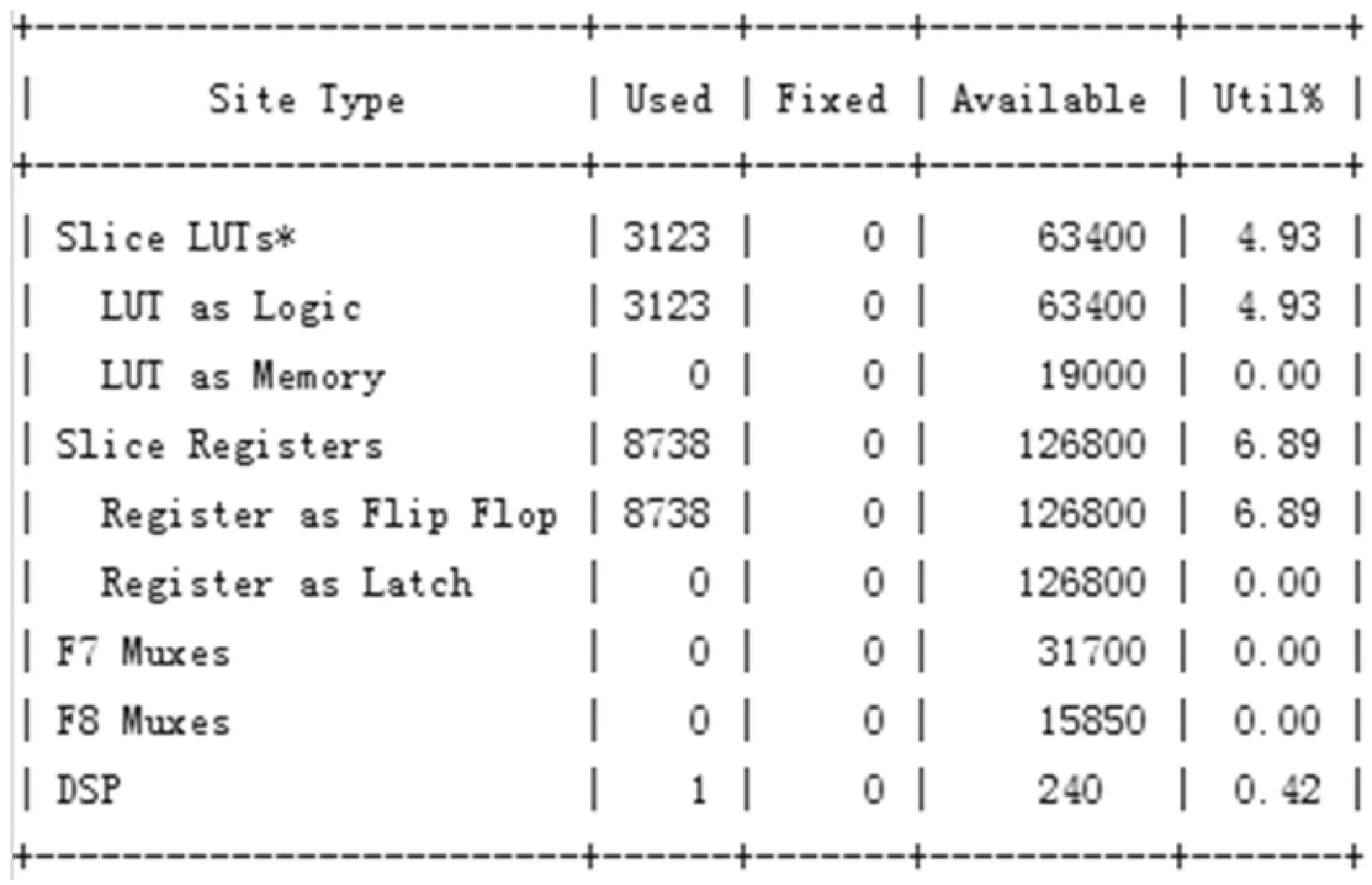

在伺服電機控制系統(tǒng)中,由于各種變量單位及范圍不同,在采用浮點類型數(shù)據(jù)進行表示時計算性能較差,同時耗時較長,也不便于算法的移植。在FPGA、DSP等設(shè)備中,往往采用定點數(shù)進行數(shù)據(jù)的計算,這也就意味著采用實際值參與算法運算的不可行性[4]。因而歸一化的引入有助于算法的定點化實現(xiàn),同時也便于算法移植,減少計算周期。以Q15格式(1位符號位,15位小數(shù)位)為例,變量定點化計算方式為:

(5)

基準值的選取往往采用變量的額定值。經(jīng)過歸一化處理,變量取值范圍被約束在[-1,+1]區(qū)間之間,各變量運算過程中不存在取值范圍不同的問題。

2.3 變M/T歸一化測速算法原理

M/T算法方法是統(tǒng)計一段時間內(nèi)編碼器脈沖計數(shù)與高頻時鐘計數(shù)來完成測速;為了兼顧算法在低速和高速時測量的可用性,其選取的統(tǒng)計時間往往較大,以確保無論在高速還是低速情況下測速時間窗口內(nèi)均有足夠的編碼器計數(shù)脈沖。正是由于這一點導(dǎo)致M/T算法在低速模式下實時性較差的不足。

結(jié)合M/T算法測速原理,當(dāng)伺服電機運轉(zhuǎn)在低速模式下,為提高速度測量實時性,可采用縮短采樣時間的方法。假設(shè)電機轉(zhuǎn)速為v,增量編碼器分辨率為N,則增量編碼器單個脈沖周期時長t(單位:s)為:

(6)

可見,增量編碼器單個脈沖周期與電機轉(zhuǎn)速成反比。在低速情況下,可通過減少統(tǒng)計的編碼器脈沖個數(shù)來減少算法響應(yīng)時間。由此在系統(tǒng)運行過程中可通過實時監(jiān)測編碼器脈沖時長來動態(tài)調(diào)節(jié)測速時間以加快系統(tǒng)響應(yīng)。

假定轉(zhuǎn)速測量周期為T,則在測量周期內(nèi)通過的增量編碼器脈沖數(shù)M1為:

(7)

可見,M1與轉(zhuǎn)速v成正比。通過針對不同轉(zhuǎn)速范圍設(shè)定不同的M1值可使得伺服電機無論高速運行還是低速運行均能有較高的測量精度以及較短的響應(yīng)時間。同時對伺服電機轉(zhuǎn)速測量歸一化[5],式(1)將變?yōu)椋?/p>

(8)

式中:vrated為伺服電機的額定轉(zhuǎn)速,該處采用Q15數(shù)據(jù)格式。

變M/T歸一化測速算法能夠在保證測量精度的同時,有效改善傳統(tǒng)M/T測量算法低速實時性較差問題,對速度的變化將更敏感,同時歸一化設(shè)計思路有利于定點化實現(xiàn)及算法移植。

2.4 Booth算法

在FPGA程序設(shè)計實現(xiàn)中,對于運算中的乘除法操作往往基于片內(nèi)DSP運算單元進行。對于衛(wèi)星上設(shè)備而言,其所選用芯片型號往往資源受限較多,Booth算法[6]能夠有效降低算法對片上DSP單元的依賴。

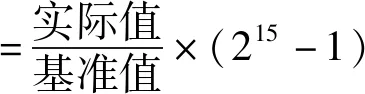

Booth算法采用相加減的操作計算補碼數(shù)據(jù)的乘積,其對乘數(shù)從最低位開始判斷,根據(jù)后兩個數(shù)據(jù)位的情況進行加法、減法或僅僅進行移位操作。判斷的兩個數(shù)據(jù)位為當(dāng)前位及其右邊的位(初始時需要增加一個輔助位0),移位操作是向右移動。假定被乘數(shù)A及乘數(shù)B位寬為N,算法實現(xiàn)思路為:

(1) 乘數(shù)B“負一位”補零,乘積項P(2N+1位寬)寄存器清零;

(2) 乘數(shù)B填入P低N+1位;

(3) 按照表1對乘積項P低兩位進行判定,根據(jù)判定結(jié)果對乘積項P高N位進行+A、-A或無操作,無視符號位溢出;

表1 Booth算法累加規(guī)則

(4) 判定乘積項P最高位,若為0則P右移高位補零,反之右移一位補1;

(5) 重復(fù)步驟(2)-步驟(4)N次;

(6) 乘積項P前2N位即為乘積項計算結(jié)果。

Booth算法能夠有效利用FPGA的移位特性、簡化乘法計算步驟、對于N位乘法計算其僅需N個時鐘周期。

同時針對式(8)中的常量乘數(shù)項借鑒Booth算法編碼規(guī)則可修改為:

(9)

通過將常量乘法轉(zhuǎn)換為移位操作能夠進一步降低對乘法器的依賴。

3 算法實現(xiàn)

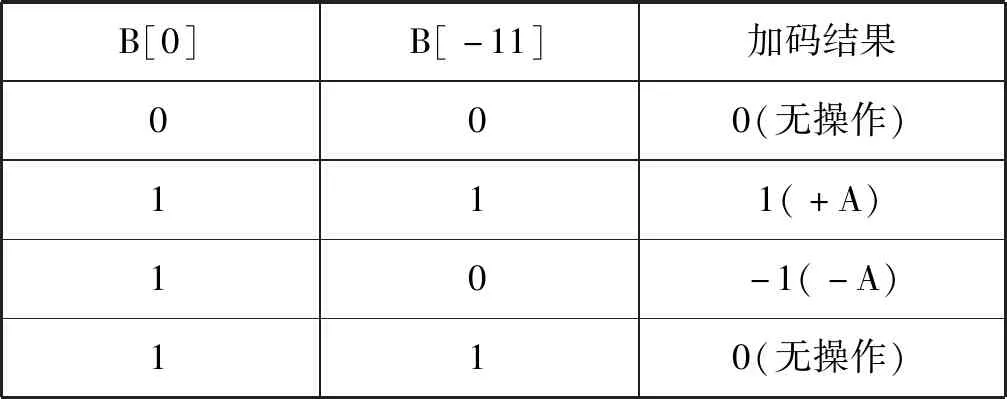

為加快系統(tǒng)響應(yīng),算法設(shè)計基于FPGA平臺進行實現(xiàn)。FPGA基于LUT+FF的結(jié)構(gòu)使得算法能夠高度并行化[7]。變M/T歸一化測速算法分為預(yù)處理模塊、速度區(qū)間預(yù)測模塊及速度測量模塊。其設(shè)計框圖如圖3所示。

圖3 變M/T歸一化測速算法設(shè)計框圖

3.1 預(yù)處理模塊

預(yù)處理模塊包括信號同步、正交編碼、方向預(yù)測三部分功能。

在FPGA設(shè)計中,對于外部多比特信號的采樣牽涉到多比特信號跨時鐘域處理從而避免亞穩(wěn)態(tài)情況。但正如圖1所示,增量編碼器A、B兩相信號相差90°,在同一時間只有一個比特位發(fā)生信號跳轉(zhuǎn),類似于格林編碼,故而信號同步邏輯可通過單比特信號跨時鐘域處理方式進行信號的同步。相比于多比特信號跨時鐘域處理,單比特信號跨時鐘域處理采用寄存器打拍形式即可,資源消耗較少[8]。

增量編碼器A、B兩相信號在一個脈沖周期內(nèi)分別有兩個狀態(tài)、通過正交編碼的處理,可形成四個狀態(tài)。在此處設(shè)計中采用“異或”邏輯對兩相信號處理,可獲得更高的分辨率。而方向預(yù)測單元通過A、B兩相相位關(guān)系獲得電機轉(zhuǎn)速方向。

3.2 速度區(qū)間預(yù)測模塊

速度區(qū)間預(yù)測模塊包括脈沖計時單元、超時保護單元及速度預(yù)測單元。

由式(6)可知,增量編碼器單個輸出脈沖周期與轉(zhuǎn)子轉(zhuǎn)速成反比,據(jù)此可由編碼器單個脈沖周期來預(yù)判電機轉(zhuǎn)速區(qū)間范圍。

脈沖計時單元基于系統(tǒng)時鐘對由正交編碼輸出信號單個脈沖信號進行計時,獲取單個脈沖時間,同時在超時保護單元中設(shè)置計數(shù)閾值以避免在超低速情況下脈沖計時單元長時間無有效輸出的情況。

速度預(yù)測單元根據(jù)編碼器單個脈沖時長決定M/T測速法脈沖計數(shù)M1值,為節(jié)省資源開銷及較少計算量,可根據(jù)脈沖時長區(qū)間指定不同的M1值,而不必按照式(7)的線性關(guān)系確定。

3.3 速度測量模塊

速度測量模塊包括脈沖計數(shù)單元、時鐘計時單元、轉(zhuǎn)速計算單元及歸一化單元。

速度測量模塊每完成一次速度測量則從速度區(qū)間預(yù)測模塊獲取脈沖計數(shù)值M1作為下次速度檢測時脈沖計數(shù)。脈沖計數(shù)單元則完成正交編碼單元脈沖計數(shù),并由時鐘計時單元基于系統(tǒng)時鐘統(tǒng)計M1個編碼脈沖所占用的時鐘節(jié)拍M2。

轉(zhuǎn)速計算單元與歸一化單元完成伺服電機轉(zhuǎn)速的計算及歸一化。系統(tǒng)運行之前首先獲取電機的額定轉(zhuǎn)速值,通過式(7)完成電機的轉(zhuǎn)速歸一化化測量。

4 仿真結(jié)果與分析

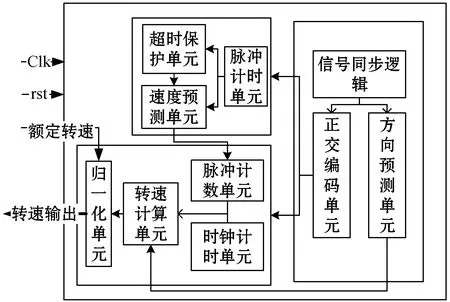

實驗設(shè)計采用Xilinx A7系列芯片作為系統(tǒng)主控芯片,基于VIVADO完成算法的實現(xiàn)及仿真[9]。算法設(shè)計資源占用情況及部分仿真圖如圖4、圖5所示。系統(tǒng)時鐘頻率50 MHz,編碼器分辨率為2 048線,電機額定轉(zhuǎn)速4 500 r/min。

圖4 資源利用報告

圖5 算法仿真波形

從資源利用報告上看,整體設(shè)計上僅消耗2 260 LUT、5 609 FF及一個DSP運算單元用于除法操作,相對于整體片上資源而言只占用了非常小的一部分,而Booth算法的引入也極大降低了算法對DSP的依賴性。圖5顯示了當(dāng)測量轉(zhuǎn)速為+5 r/min、-5 r/min時的標幺化輸出結(jié)果分別為0x24、0xffdc,與相應(yīng)轉(zhuǎn)速理論歸一值一致。

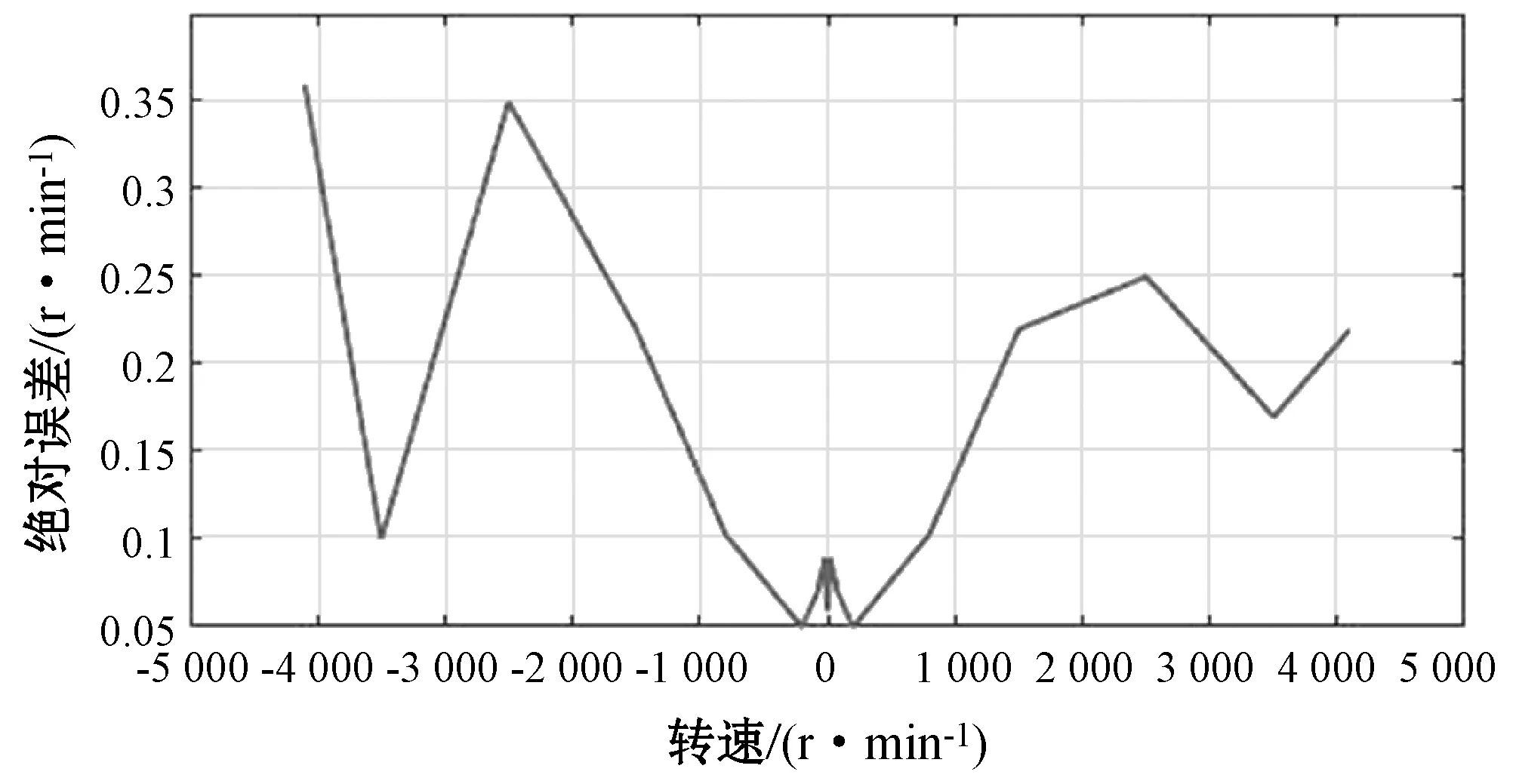

針對不同轉(zhuǎn)速輸入,實驗仿真結(jié)果及其絕對誤差分別如表2、圖6所示。

表2 實驗仿真結(jié)果

圖6 絕對誤差統(tǒng)計圖

從仿真結(jié)果來看,以歸一值表示時測量誤差在±2范圍之內(nèi),且在低速時有較高的準確度。轉(zhuǎn)速測量值誤差最大不超過±0.4 r/min,而在低速范圍-200~200 r/min內(nèi),絕對誤差不超過0.1 r/min。誤差的存在主要由于:

(1) 歸一化量化誤差。歸一化由于采用定點數(shù),故在進行轉(zhuǎn)換時會引入一定誤差,誤差范圍在:

(2) 由于定點化的實現(xiàn)方式,FPGA在運算過程中會存在位寬截取情況,引入一定誤差。

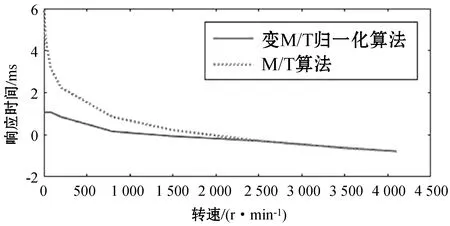

變M/T歸一化測速算法及普通M/T測速算法(取M1值為128)不同轉(zhuǎn)速下的響應(yīng)時間對比結(jié)果如圖7所示。

圖7 響應(yīng)時間對比對數(shù)圖

根據(jù)圖7對比,當(dāng)電機處于低速運行時,變M/T歸一化算法在響應(yīng)時間上相比于M/T算法有極大的縮減,當(dāng)轉(zhuǎn)速低于50 r/min時響應(yīng)時間能縮短25倍以上。這對于電機在低速運行時提高系統(tǒng)的靈敏度有極大的改善和幫助。

5 結(jié) 語

本文針對伺服電機的測速問題提出了一種基于FPGA的變M/T歸一化測速算法。通過實驗仿真表明,該算法無論在低速范圍內(nèi)還是高速范圍內(nèi)均有較高的測速精度,同時具有快速響應(yīng)的特點。歸一化的設(shè)計使得算法能夠針對不同參數(shù)型號編碼器及永磁同步電機均能有較高的測量精度,也廣泛適用于伺服電機控制系統(tǒng)中的速度控制應(yīng)用,避免因不同變量的單位數(shù)制問題引入的計算精度與計算誤差。同時Booth算法的引入也極大降低了算法對DSP的依賴性。本文算法為空間材料科學(xué)實驗裝置中永磁同步電機的速度檢測方式提供了一種參考設(shè)計思路。