鎖相環頻率合成器相位噪聲改善方法分析

李捷 張心澤

摘要:在眾多電子設備中,如:雷達探測、檢測儀器、通信等,鎖相環頻率合成器作為接收機的核心部件,其的性能直接影響著電子設備的整體性能,尤其是相位噪聲,直接關系著頻率穩定性,影響著電子設備的精確度。對此,積極改善相位噪聲,提高鎖相環頻率合成器的穩定性,滿足人們對電子技術的高質量需求,具有重要意義。文章對相位噪聲的改善方式展開探析。

關鍵詞:鎖相環;頻率合成器;相位噪聲;改善方式

1 鎖相環頻率合成器的簡單概述

當前,頻率合成器的常見實現方式主要包含三種:直接模擬(DAS)、鎖相環頻率合成(PLL)以及直接數字頻率合成(DDS)。頻率合成器主要以高精準的晶體振蕩器為基準,利用合成技術,產生一系列擁有一定的頻率間隔且高清度的頻率源,因此,頻率合成器又被分為直接合成器與鎖相環合成器[1]。

2 鎖相環頻率合成器的結構與相位噪聲

在三種頻率合成方式中,PLL相比于DAS、DDS,雜散抑制更高,頻譜更純凈。與DDS相比,PLL的頻段更加寬泛;相比于DAS,PLL的結構更加簡單。因為種種優勢,在我國通信、雷達、儀表等電子設備中,鎖相環頻率合成器的應用較為廣泛。在鎖相環合成器中,其主要采用PLL展開頻率合成,而單環鎖相環最為簡單,只需要在壓控振蕩器、鑒相器兩者間連接的鎖相環反饋電路之上添加整數分頻器,即可形成整數頻率合成器。分頻系數變動,則壓控振蕩器將產生的輸出信號頻率相應不同,因為,該種合成器的頻率為所參考信號的整數倍頻率,因此,其被叫做整數頻率合成器。

不過,PLL也存在一定缺陷,即相位噪聲更大。相位噪聲的存在,電子設備性能受到影響,如:在通信設備中,相位噪聲影響,話路信噪比因此下降,增大了誤碼率;在雷達設備中,相位噪聲的存在,雷達對掃描目標的分辨率下降;若相位噪聲進入接收機,將形成較強干擾信號,產生倒混頻,增大接收機的噪聲系數[2]。基于此,在電子技術不斷發展的時代,改善相位噪聲,成為鎖相環頻率合成器不斷不斷研發的重點。

3 鎖相環頻率合成器結構相位噪聲的完善措施

3.1 雙鎖相環的混頻結構

雙鎖相環的混頻結構主要是由2個鎖相環、1個混頻器構成,其中,主環與輔環之間的輸出頻率有如下關系:Fout=FPD1*N1+FPD2*N2,在式子中,FPD1為主環鑒相頻率,FPD2為輔環鑒相頻率,N1為主環分頻比,N2為輔環分頻比。

在雙鎖相環運行中,主鎖相環的輸出信號主要作為LO信號,與輔鎖相環的相環信號開展下變頻,而混頻器輸出低頻率IF信號,以此降低主鎖相環的N1。FPD1與頻率步進等同,如此,只需要改變N1,就可跳頻。輔相環所輸出頻率是定頻信號,因此,在選擇FPD2時,可隨意選擇。

計算雙鎖相環相位噪聲,公式如下:

N1=N2=Fout/(FPD1+FPD2)

最小相位噪聲為:PNtotel=PNSYNTH+10*log(Fout)+10log[Fout/(FPD1+FPD2)]

而單鎖相環合成器的相位噪聲為:PNtotel=PNSYNTH+10*log(Fout)+10log(Fout/FPD)

單鎖相環鑒定頻率FPD與主鎖相環鑒定頻率相同,將單鎖相環相位噪聲公式減去雙鎖相環的相位噪聲公式,得出的值為相位噪聲的改善值,為:

△PN=10log[(FPD+FPD2)/+FPD]=10log(1+FPD2/FPD)

據此繪出圖1,展示了相位噪聲完善值與鑒相頻率間的比值關系,比值越大,則相位噪聲的改善作用越大。不過,該種結構下,也擁有如下缺陷:其一,雙鎖相環下,輔環的輔助下,主環分頻比下降,但是,若頻率步進較小,主環相位噪聲相應提升。其二,與單鎖相環相比,雙鎖相環的器件較多,甚至是前者的一倍,與電子設備發展方向不符。其三,輔環信號在通過混頻器之后,極易為輸出信號引入雜散,影響電子設備的正常運行。

3.2 鎖相環加分頻器結構

鎖相環加分頻器結構,也是一種完善相位噪聲的方式,只需要在鎖相環結構后添加分頻器即可。輸出信號相位噪聲的公式如下:

PNtotel=PNSYNTH+10*log(FPD)+20*log(N/X)

Fout=FPD*N/X

根據上述公式可知,若FPD與X之間同比例增加,輸出頻率并不會變化,而輸出的相位噪聲卻呈現出下降狀態。并且,X擴大一倍,則FPD同樣擴大一倍,PNtotel降低3dB。

不過,該種結構也擁有不足之處。因為,此種方案的應用,鎖相環輸出頻率間接提升,依照原理可知,將導致鎖相環芯片選擇、研制難度增大。同時,與雙鎖相環結構相似,若頻率步進較小,輸出頻率較高,則相位噪聲仍然相對較高,為電子設備運行帶來影響。

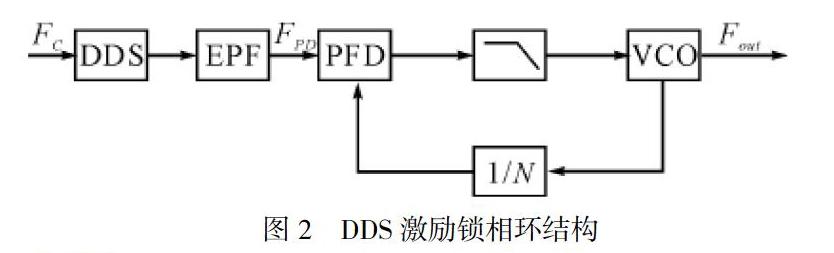

3.3 DDS激勵鎖相環結構

DDS激勵鎖相環結構具體如圖2所示,作為一種完善相位噪聲的方式,其主要利用DDS為鎖相環參考頻率。在該結構運行在電子設備中時。若鎖相環分頻比保持不變,僅需要改變DDS輸出頻率,就能夠實現跳頻。如此,在較低分頻比狀態下,頻率步進相應較低。并且,鎖相環能夠直接增大DDS輸出頻率,還能濾除DDS應用雜散,實現低噪聲、寬頻率、高雜散抑制的頻率合成。當然,該種結構并非完美無缺,若DDS的雜散進入環路低通帶,則鎖相環無法濾除,進而影響電子設備的健康運行[3]。

4 總結

總而言之,在鎖相環合成器應用中,相位噪聲難以避免,影響了電子設備的精準性,阻礙了電子設備的效用發揮。而在相位噪聲完善中,若采用雙鎖相環結構,則相位噪聲會降低10log(1+FPD2/FPD),且合成器的結構簡單,極易實現,不過,器件也增大一倍,較小步進難以實現,混頻器也易雜散。利用鎖相環結合分頻器結構,相位噪聲降低10log(X),且合成器結構簡單,不易引入雜散,不過,難以實現較小步進。而DDS激勵鎖相環應用中,DDS輸出頻率增大一倍,相位噪聲相應降低3dB,小步進也容易實現,不過,若雜散進入通帶,將難以去除。總之,結構不同,相位噪聲改善不同,優缺點相應不同。對此,在頻率合成器實際設計中,應嚴格依照系統要求,選擇最佳結構,完善相位噪聲,充分發揮合成器的效果。

參考文獻:

[1]基于級聯偏置鎖相環的寬帶頻率合成技術研究[D]. 電子科技大學.

[2]孫家星, 孫越強, 杜起飛. 鎖相環頻率合成器最優環路帶寬的選取[J]. 固體電子學研究與進展, 2016, 36(6):457-459.

[3]低噪聲鎖相環頻率合成器的研究與設計[D]. 南京郵電大學, 2018(7):34-34.