DSP中的浮點與定點比較

侯力秩

(翱捷科技(深圳)有限公司,深圳 福田 518000)

0 引 言

目前,在DSP業界存在兩類數據表示形式,同時伴隨產生了兩類DSP架構產品。關于兩類產品的不同特性,業界存在很多討論甚至爭議。本文大致描述兩類數據表示格式在DSP應用中的不同特性,并闡述其特點和使用場景。

1 浮點數據格式與定點數據格式

1.1 浮點數據格式

在計算機系統的發展過程中提出過多種方法表示實數,但是目前為止使用最廣泛的是浮點表示法。IEEE(Institute of Electrical and Electronics Engineers,電子電氣工程師協會)在I985年制定的IEEE 754(IEEE Standard for Binary Floating-Point Arithmetic,ANSI/IEEE Std 754-1985)二進制浮點運算規范,是浮點運算部件的工業標準[1]。

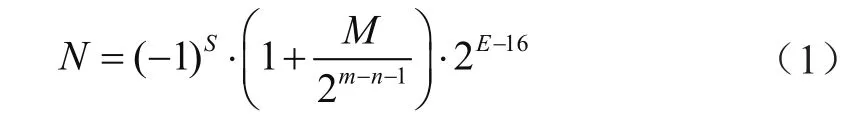

采用以下浮點表示格式表示16位浮點數,該格式為IEEE 745標準的子集,除了能夠完成要求的實數表示外,處理上也更為簡潔。總位寬m=16 bit,格式如圖1所示,用一個三元組{S,E,M}來表示一個數N。

圖1 三元組表示法舉例

(1)S(Sign)表示N的符號位,位寬為1 bit,對應值s滿足:N>0時,s=0;N<0時,s=1;N=0時,s=0或1均可。

(2)E(Exponent)表示N的指數位,位于S和M之間的n位,默認位寬n=5 bit。E采用移碼表示,固定偏置為16。E的數值范圍為0~31,但其表示數值的實際范圍為-16~15。

(3)M(Mantissa)表示N的尾數位,位于N末尾,默認位寬為10 bit。小數點在最左邊,且左邊還有一個隱含位,這個隱含位固定為1。假定M為“0101100111”,其對應的實際值在二進制數值上是“1.0101100111”。

N數值計算式如下[2]:

可見,它的最小正數為min=1.0×2-16≈1.525 9×10-5,最大正數為max=(1.1111111111)bin×215=65 504。

1.2 定點數據格式

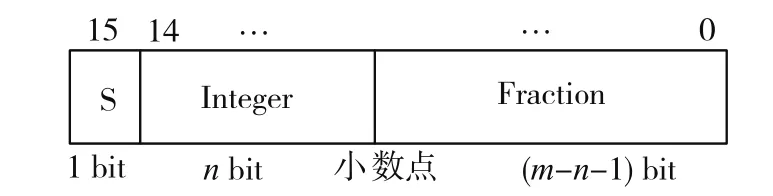

定點數據格式如圖2所示,16位定點數的首位為符號位,0表示正數,1表示負數。后面的數據部分為二進制整數部分和二進制小數部分。整個數值部分表示的數據大小為整數部分和小數部分之和。

圖2 16 bit定點數據格式

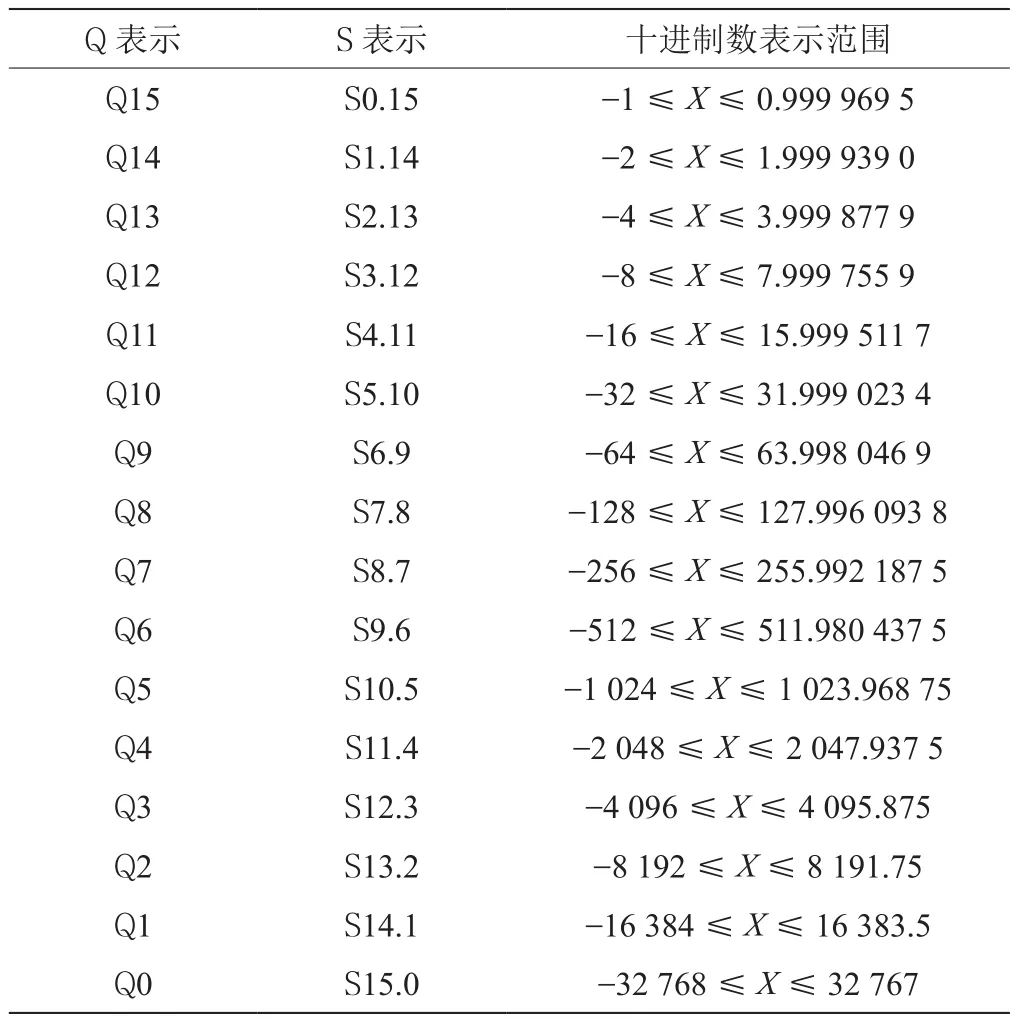

由于定點數表示的小數點位置可以發生變化,因此定點數根據小數點位置的不同可以定義成不同的數據格式。如表1所示,Q代表小數所占據的位寬,S則代表整數和小數所占據的位寬。

2 浮點定點DSP主要優劣對比

2.1 浮點DSP主要優點和缺點

傳統意義上,浮點數運算具有如下優點。

(1)動態范圍大。由于浮點數采用了類似科學計數法形式的數據表示方式,因此其數據分布為非均勻狀態,如圖3所示。在同樣數據寬度的情況下,浮點數據能夠表示更寬廣的動態范圍,因此浮點DSP進行數據處理時基本不會發生數據溢出現象。

表1 定點數據格式范圍

圖3 浮點數和定點數的數據分布對此

(2)浮點數據舍入誤差小,表示數據更精確。定點數相對于浮點數會引入更大的量化誤差。例如:對于32位浮點數,每個相鄰的數據之間的數據間隙約為該數據的千萬分之一。每引入一個新的浮點數,需要舍入這個間隙的一半。對于16位定點數,數據間的間隙是等間距的。對于整數表示的浮點數(-32 768~32 767),引入10 000左右的數據則會引入1/10 000左右的舍入誤差;表示1 000左右的數據,則會引入1/1 000的舍入誤差。標準的量化誤差一般為舍入誤差的1/3,這樣在表示數據時,浮點數引入的量化噪聲將遠遠小于定點數。特別是在累加操作中,定點數引入的量化噪聲可能得到進一步累加,導致結果精確度下降。

首先,尋找現場光源。即便在弱光環境下依然會有些許高光區域,利用畫面之中的最亮部分進行對焦。其次,尋找對比度高的邊界進行對焦。當下不少數碼相機依然使用對比檢測方式進行對焦,所以在對焦時尋找對比度高的邊界,可以發揮相機的優勢。最后,利用相機的中心對焦點進行對焦。一般相機的中心對焦點都是對焦能力最強的地方,關閉自動選擇對焦物體模式,而采用中心點的單點對焦模式,先對焦再構圖,可以加大對焦的成功率。

2.2 定點DSP的主要優點和缺點

傳統意義上,定點數運算具有如下優點。

(1)定點運算單元的設計相對于浮點運算單元較為簡單直接,一般定點運算單元所需的內部單元少,結構想對簡單,因此定點運算單元在設計成本上相對于浮點運算單元具有一定的設計優勢。

(2)定點運算單元由于設計面積較小等原因,具有較小的運行功耗,因此對于對功耗有需求的處理器具有一定的吸引力。

傳統意義上,定點數運算具有如下缺點。

(1)定點數的動態范圍較小,對動態范圍較大的DSP運算一般無法較好地表示,只能通過飽和截位等操作進行近似處理,喪失了一定的運算精度。

(2)定點數相對于浮點數會引入更大的量化誤差。

3 定點DSP為保持數據精度的設計

定點DSP由于在動態范圍、表示精度和開發復雜度上的不足,往往會通過多種方式進行彌補[3]。

(1)提供相應的庫函數和開發工具,輔助軟件設計人員加速完成浮點算法到定點程序的轉化;

(2)內部設置較高精度范圍的累加器,防止誤差在累加時被累積;

(3)設置相應的溢出等狀態位,通知程序人員當前的運算狀態;

(4)設計專門的飽和歸一化指令,完成對數據結果的處理;

(5)指令集分為整數操作指令和定點數操作指令,并對結果進行不同方式的舍入等處理;

(6)乘法器一般帶有對結果的移位功能,直接控制結果的輸出定點格式。

4 結 論

綜上所述,在進行高復雜度、高精度要求的數據處理如3G、4G等通信算法時,浮點DSP具有很強的設計優勢。因此,各大DSP處理器設計公司都在其高端DSP領域采用了浮點設計或浮點/定點混合技術。