抗單粒子功能中斷的加固技術研究

劉 淼,牛英山

(中國電子科技集團公司第四十七研究所,沈陽110032)

1 引 言

隨著我國航天領域的飛速發展,各類人造衛星、空間探測器等航天器相繼進入太空,為國家的發展和社會的進步提供支持和保障。在太空中,工作環境復雜且惡劣, 嚴重影響航天器中的集成電路的正常工作,單粒子功能中斷就是空間輻射對集成電路的嚴重影響之一[1]。單粒子功能中斷通常由單粒子瞬態和單粒子翻轉共同作用產生。由于單粒子瞬態 SET(Single-Event Transient)和單粒子翻轉效應SEU(Single-Event Upset)具有任意時間和任意地點的隨機性特點以及SET 在一定條件下可轉化為SEU 的特點,從而使之成為抗輻射加固集成電路的重點研究內容之一[2]。

2 單粒子功能中斷機理分析

單粒子功能中斷主要出現在大規模集成電路中,是由一個高能量的粒子入射到半導體材料的反偏PN 結或者體硅區導致的,沿著高能粒子的運動軌跡會產生大量的電子空穴對,當在入射路徑沉積的能量足夠大時, 會引起集成電路性能下降甚至控制部件出錯,引起正常的功能中斷或出錯。發生單粒子功能中斷的器件功能暫時喪失,需電源重啟恢復。

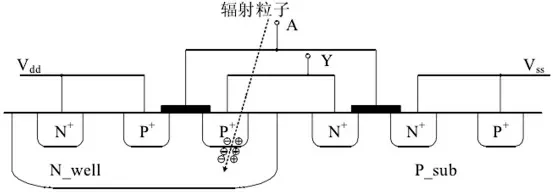

圖1 是一個CMOS 結構的反相器受到單粒子干擾的示意圖,這個干擾產生的脈沖出現在組合邏輯中,稱為單粒子瞬態脈沖[3]。

圖1 反相器版圖橫截面圖

當單粒子瞬態(SET)所引起的錯誤被觸發器或存儲器采樣并輸出到產生SET 的組合邏輯上并形成環路,從而導致錯誤狀態持續保持,就會產生單粒子功能中斷。同樣當這種現象發生在觸發器或存儲器中, 即產生單粒子翻轉效應SEU, 當SEU 輸出到組合邏輯并形成環路,也會產生單粒子功能中斷。隨著工藝尺寸不斷變小,臨界電荷隨工藝約成平方關系減小。在超深亞微米工藝下,數字組合電路中的SET 脈沖很容易像正常的信號一樣沿著組合邏輯傳播并被末端的觸發器或存儲器捕獲形成一個持久的錯誤,從而導致單粒子功能中斷。

3 抗單粒子功能中斷加固電路設計

3.1 設計原理

由以上原理可以看出, 組合邏輯上的單粒子干擾是可以通過多級邏輯逐漸吸收的, 只有干擾信號被觸發器或存儲器鎖存,并反饋形成環路,才會產生功能中斷, 所以觸發器或存儲器的信號鎖存功能是產生單粒子功能中斷的必備條件[4-6],因此對觸發器進行抗單粒子加固設計,屏蔽掉干擾信號,就可以解決觸發器信號路徑上的單粒子功能中斷的問題[7-8].

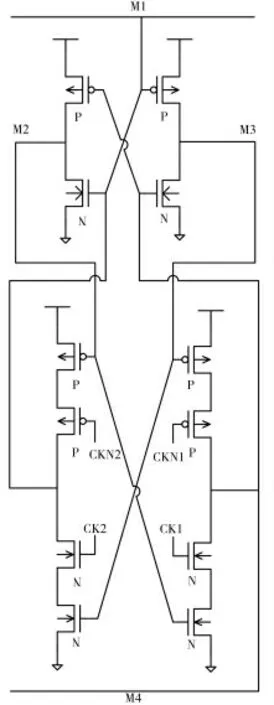

觸發器抗單粒子加固設計主要使用加固DICE觸發器設計(Dual Interlocked Cell)。加固 DICE 觸發器設計主要包含時鐘冗余電路、主DICE 鎖存器、從DICE 鎖存器、延時濾波電路、相位轉換電路。圖2 是DICE 鎖存器主要結構。可見,DICE 鎖存器內部有M1、M2、M3、M4 電荷存儲節點,其中 M1、M4 存儲的電平相同, M2、M3 存儲的電平相同, 當干擾粒子進入芯片,使4 個節點中的某一個節點發生翻轉, 結構中的雙互鎖存結構DICE 可以將其余3 個節點的電平值恢復。只有M1、M4 存儲節點同時受到高能粒子的影響時,或者M2、M3 存儲節點同時受到高能粒子的影響時,才能引發整個電路的翻轉。因此DICE 對干擾離子引起的電離翻轉,有很強的抵抗能力。本設計將采用加固DICE 觸發器進行設計實現。

圖2 DICE 鎖存器

3.2 設計實現

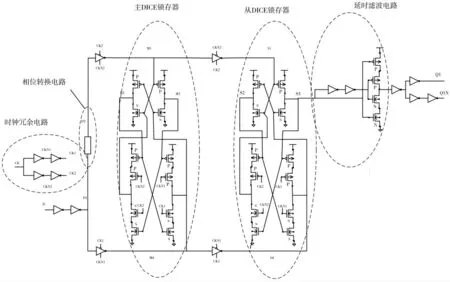

圖3 加固DICE 觸發器

設計采用加固DICE 觸發器實現抗單粒子功能。設計圖如圖3。可見,左側有時鐘冗余電路,由4 個反相器組成,將 CK 時鐘分為 CK1、CK2、CKN1、CKN2。CK1 和 CKN1 主要控制經過 D1、M4、S4 和兩個三態門的傳輸信號,CK2 和CKN2 主要控制經過D2、M1、S1 和兩個三態門的傳輸信號。同時CK1、CK2、CKN1、CKN2 用在主 DICE 鎖存器和從 DICE鎖存器,在主DICE 鎖存器中,CK1 和CKN1 控制M4 上的信號的鎖存,CK2 和 CKN2 控制 M1 上的信號的鎖存。在從DICE 鎖存器中,CK1 和CKN1 控制S4 上的信號的鎖存,CK2 和 CKN2 控制 S1 上的信號的鎖存。延遲濾波電路由延遲單元和濾波電路兩部分組成,主要功能是利用延遲單元,在前后2~3 個時刻分別對輸入數據進行取樣。若數據不同,說明受到SET 干擾,此時濾波電路會維持之前的狀態。如果電路要屏蔽SET, 延遲電路的延遲時間要大于干擾脈沖的寬度。該設計中將延遲濾波電路放到輸出端,即能夠對輸入端的普通SET 干擾能夠進行屏蔽,也能對發生在觸發器內部單粒子瞬態干擾進行屏蔽。當單粒子干擾發生在時鐘上升沿時,形成信號鎖存,該電路無效,需要相位轉換電路進行屏蔽。主從兩個DICE 鎖存器主要用于對內部產生的單粒子干擾進行屏蔽,在主DICE 鎖存器中,M1 信號與M4信號相同,當M1=1 時,M4=1,如果M1 上出現單粒子干擾脈沖,將信號拉低,M1=0,輸入與M1 相連的MOS 管 P3 導通,M3 上出現干擾脈沖,M3=1,輸入與M3 相連的MOS 管N9 導通,與N9 串聯的MOS管N8 的輸入端連接時鐘,處于截止狀態,所以該干擾脈沖被截止在N8。同樣如果M4 上出現單粒子干擾脈沖,將信號拉低,M4=0,輸入與M4 相連的MOS管P2 導通,M2 上出現干擾脈沖,M2=1,輸入與M2相連的MOS 管N5 導通,與N5 串聯的MOS 管N4的輸入端連接時鐘,處于截至狀態,所以該干擾脈沖被截止在N4。在從DICE 鎖存器中,S1 信號與S4 信號相同,當S1=1 時,S4=1,如果S1 上出現單粒子干擾脈沖,將信號拉低,S1=0,輸入與S1 相連的MOS管 P9 導通,S3 上出現干擾脈沖,S3=1,輸入與 S3 相連的 MOS 管 N14 導通,與 N14 串聯的 MOS 管 N15的輸入端連接時鐘,處于截至狀態,所以該干擾脈沖被截止在N15。同樣如果S4 上出現單粒子干擾脈沖,將信號拉低,S4=0,輸入與S4 相連的MOS 管P10 導通,S2 上出現干擾脈沖,S2=1,輸入與 S2 相連的 MOS 管 N12 導通,與 N12 串聯的 MOS 管 N13的輸入端連接時鐘,處于截至狀態,所以該干擾脈沖被截止在N13。但是因為S3 通過組合邏輯與輸出相連,所以這種干擾會輸出到下一級,變為單粒子瞬態干擾。單粒子瞬態會通過組合邏輯傳輸到下一級觸發器,并且被DICE 結構屏蔽。相位轉換電路是buffer 鏈組成的delay 單元,位置是在第一級的trinv的輸入端,其功能是將輸入信號D 分解為信號相同,相位不同的兩個輸入信號D1 和D2,如果單粒子干擾信號在時鐘沿產生,在其后面的傳輸路徑上的 M1 和 M4 信號相同,相位不同,同樣,S1 和 S4 信號相同,相位不同。與S3 相連的PMOS 的輸入端連接S1,與S3 相連的NMOS 的輸入端連接S4,如果有單粒子干擾導致PMOS 和NMOS 同時導通,因為相位不同,也不會出現短路和翻轉現象。

4 抗單粒子功能中斷加固技術仿真分析

4.1 仿真原理

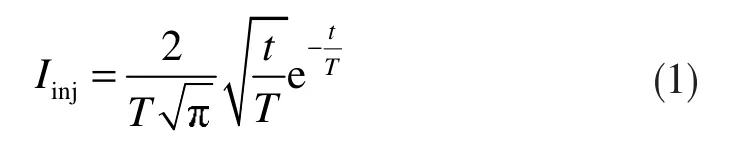

為檢查抗輻射加固電路在輻射環境下的抗加能力,本設計使用電流源作為單粒子對電路的影響的模型,使用Cadence 仿真軟件來模擬單粒子輻射對電路的影響。其電流源表達式為:

其中T 是和晶體管模型及離子能量吸收(LET)有關的常量,P 管和N 管的值不同,t 是時間變量。

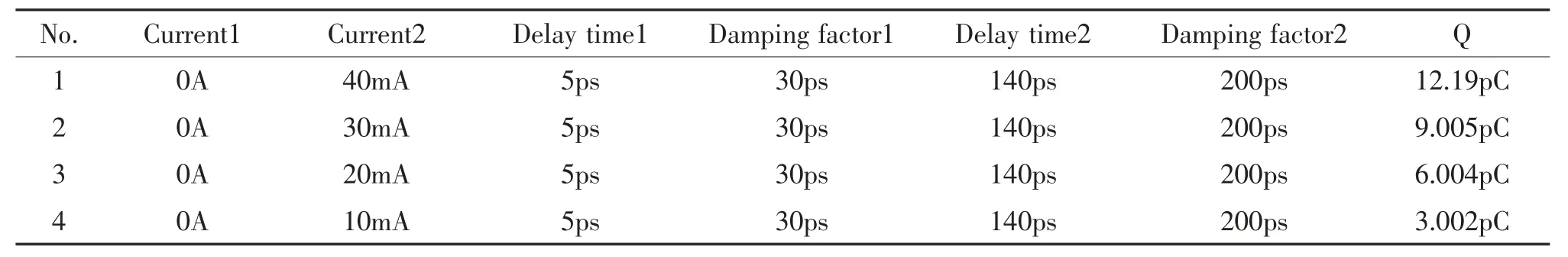

仿真使用的干擾電流源能量表如表1 所示:

表1 電流源能量

仿真使用的是I=10mA,上升沿延遲=25ps,保持時間=135ps,下降沿延遲=60ps,電荷數=3.002pC。

電路采用上華0.5μm 工藝庫,模型為tt_5v,仿真時,供電電壓為5V,溫度為室溫25℃。為了便于進行 SEU/SET 故障注入,采用時鐘頻率=20MHz,采樣周期為3μs。

4.2 仿真結果

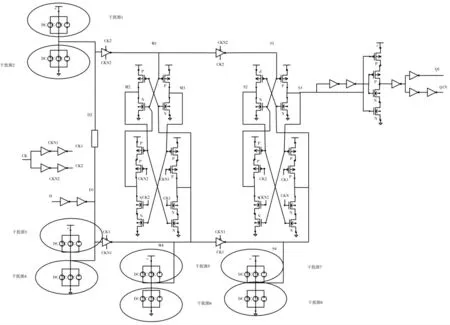

觸發器仿真所采用的電路圖如圖4 所示。

圖4 仿真電路圖

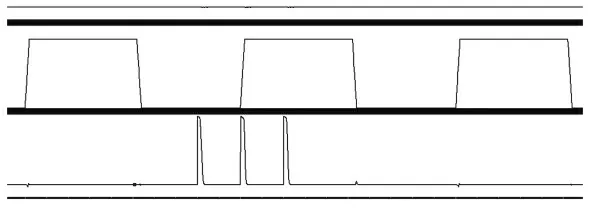

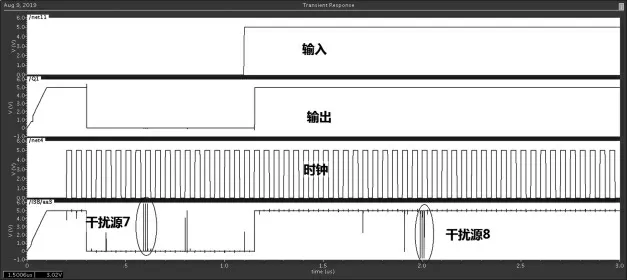

從圖4 可以看出,干擾源1 和2 設置在D2 端,干擾源3 和4 設置在D1 端,干擾源5 和6 設置在M4 端,干擾源7 和8 設置在S4 端。每個干擾源設置三個干擾信號,分別設置在一個時鐘周期的高電平階段,低電平階段和上升沿階段,如圖5 所示。

圖5 局部波形圖

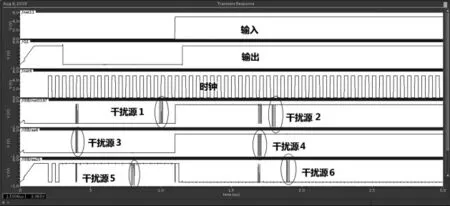

仿真波形如圖6 和圖7 所示。由圖6 和圖7 可見,在D2 端,當D2=0 時,輸入干擾源1,模擬輻照時單粒子效應產生的瞬間的高電平,當D2=1 時,輸入干擾源2,模擬輻照時單粒子效應產生的瞬間的低電平。其他干擾源也是用相同方法設置。由輸出波形可以看到,雖然干擾源在觸發器內部產生信號波動,輸出波形未受影響。

圖6 仿真波形圖A

圖7 仿真波形圖B

5 結束語

集成電路在輻照條件下,產生單粒子功能中斷,能中斷的電路為例,進行原理分析和加固設計,并通過仿真對加固設計進行驗證,所獲得的數據和結論具有一定代表意義。文中設計的抗單粒子功能中斷加固觸發器能夠應用到電路設計中,具有一定的實用價值。