基于FPGA的三相SPWM變頻變壓電源的研究

徐彬 王傳禮 喻曹豐 解甜

摘 ?要: 針對傳統的變頻變壓電源采用的模擬控制技術的不足,設計一種基于FPGA的三相SPWM變頻變壓電源。對主要的硬件電路和基于FPGA的數字控制電路進行研究;分析SPWM波的調頻調壓原理;通過改變頻率控制字來控制開關管生成頻率可調的電壓,調節調制度和PWM波的占空比來調節輸出電壓幅值。研究結果表明,系統實現了輸出頻率和幅值可調的三相正弦交流電,相位彼此相差為120°,輸出電壓幅值在0~25 V內可調,輸出頻率在0~100 Hz范圍內以0.1 Hz的精度調節。仿真與實驗結果證實了該設計方案的準確性和可行性。

關鍵詞: 變頻變壓電源; 三相SPWM; FPGA; 逆變電路; 頻率控制字; 調制度; 占空比

中圖分類號: TN773?34; TM921 ? ? ? ? ? ? ? ? ?文獻標識碼: A ? ? ? ? ? ? ? ? ? ? ?文章編號: 1004?373X(2020)02?0009?05

Study of three?phase SPWM VVVF power supply based on FPGA

XU Bin, WANG Chuanli, YU Caofeng, XIE Tian

Abstract:A three?phase SPWM VVVF power supply based on FPGA is designed to improve the shortcomings of the analog control technology used in the traditional VVVF power supply. The main hardware circuit and the digital control circuit based on FPGA are studied, and the principle of frequency modulation and voltage regulation of SPWM wave is analyzed. The switching tube is controlled by changing the frequency control word to generate the frequency adjustable voltage, the modulation degree and duty cycle of PWM wave are adjusted to regulate the output voltage amplitude. The research results show that the system can realize three?phase sinusoidal AC with adjustable output frequency and amplitude. The phase difference is 120°, the output voltage amplitude is adjustable within 0~25 V, and the output frequency is adjustable within 0.1 Hz in the range of 0~100 Hz. The simulation and experimental results verify the accuracy and feasibility of this design scheme.

Keywords:VVVF power supply; three?phase SPWM; FPGA; inverter circuit; frequency control word; modulation degree; duty cycle

0 ?引 ?言

隨著電力電子技術和數字化控制技術的快速發展,傳統模擬變頻電源存在諸多缺陷[1?2],如線路復雜,難以避免硬件電路的溫漂問題,導致系統參數漂移。另外考慮到控制系統須滿足安全穩定性高、脈沖控制信號的輸出精度高、實時性強、易修改、可現場編程以及集成度高等要求[3?4],基于FPGA的變頻變壓電源數字控制電路的設計便應運而生。FPGA用硬件連線實現算法,提高了運算速度,采用高速并行計算的工作方式,提高了系統的抗干擾性能[5?7]。

本文介紹了基于FPGA的三相SPWM變頻變壓電源的設計方案,電源的硬件電路輸入端接入220 V/50 Hz工頻交流電,通過FPGA EP4CE10F17C8芯片產生的控制信號來控制逆變主電路和母線調壓電路,最終輸出頻率和幅值可調的三相正弦交流電。輸出電壓幅值在0~25 V內可調,輸出頻率在0~100 Hz內調節,頻率分辨率為0.1 Hz。經仿真與實驗驗證了該設計的正確性。

1 ?系統設計的基本方案

本文所設計的變頻變壓電源是通過FPGA來控制單相交流電向三相交流電的轉換,其變頻變壓功能可以改變三相交流電的輸出頻率和幅值。系統設計的基本原理圖如圖1所示,主要包括以下4個功能模塊:FPGA數字控制電路、開關電源電路、直流母線調壓電路和逆變主電路等。其中直流母線調壓電路和逆變電路是該電源的關鍵,本文主要研究了這兩部分。FPGA用來控制整個變頻變壓電源,其中包括產生用于控制逆變電路的三相SPWM波和用于調節直流母線電壓的PWM波。

2 ?調頻調壓原理

調節變頻變壓電源的幅值一般主要是通過改變調制度和調節母線電壓來實現的,本設計綜合兩種調壓方式,使變頻變壓電源適應更加復雜的環境。

假設變頻變壓電源輸出電壓幅值為Um和輸出電壓頻率為f。由此可知,Um的大小取決于母線電壓U母線、調制度M,另外母線電壓的調節范圍與PWM波的占空比D有關,則其關系式可近似表達為:

[Um=MDU母線] ?(1)

式中,調制度M被定義為正弦調制波幅值與三角載波幅值的比。

根據開關電源得到的直流母線電壓為50 V,則由式(1)可得:

[Um=50MD] ? ? ? ? ? ? ? ?(2)

輸出電壓的頻率f與載波頻率、調制波頻率、載波比等有關,其中調制波頻率又與頻率控制模塊輸出的頻率控制字fcw相關。因此本文通過改變頻率控制字fcw的大小來改變輸出電壓的頻率f的大小,其關系表達式近似表示為:

[f=fcw·fclk2N] ? ? ? ? ? ? ? ? (3)

式中: [fclk]為系統時鐘;N為相位累加器的位數。

3 ?系統硬件電路設計

3.1 ?母線調壓電路的設計

由上文知,改變母線電壓可以調節輸出電壓幅值,而母線電壓的大小與PWM波的占空比有關。因此,本文是通過改變PWM波的占空比來間接地調節輸出電壓幅值。直流母線調壓電路如圖2所示。

圖2中MAX627是MOS管的驅動芯片,FPGA產生的PWM波經過驅動芯片后則可以驅動MOS管。從MAX627輸出的PWM波依次經過電容濾波和脈沖變壓器傳輸到MOS管的柵極,以此來控制MOS管的導通與截止,從而控制母線電壓的大小。

3.2 ?逆變電路的設計

本設計中逆變電路的功能是把直流母線電壓轉化為正弦交流電壓,電路原理圖如圖3所示。

FPGA輸出U,V,W三相相位彼此相差120° SPWM波信號,分別控制著三個逆變半橋,每一相分為兩路共六路,每兩路SPWM波(如DH_U和DL_U)互補且嚴格控制它們的死區時間。由于FPGA輸出的三相SPWM波不能直接驅動MOS管,因此須經過驅動電路后才能控制MOS管的導通與截止,從每個半橋輸出的電壓經過LC濾波就可以得到三相交流電。其中MOS管的驅動芯片為IR2101,MOS管的型號為IRFZ44N。

4 ?基于FPGA數字控制電路的設計

4.1 ?正弦調制波模塊

直接數字式頻率合成器(Direct Digital Synthesizer,DDS)是一項關鍵的數字化技術。與傳統的頻率合成器相比,其主要特點是低功耗、高分辨率、快速轉換時間、相位干擾小等而得到廣泛應用[8?9]。圖4為DDS設計原理框圖。

基于DDS的正弦波設計,是將正弦信號經過取樣、量化,存于ROM中。正弦波幅值獲取的方法有很多,本設計借助Matlab軟件編寫正弦波程序直接生成ROM的初始化文件(.mif)格式;然后使用Altera的QuartusⅡ軟件調用LPM_ROM模塊實現ROM存儲器;最終將會得到數字正弦波。圖5為該模塊的設計原理圖。

本文將一個周期的正弦波等分2N個點,并將各點對應的幅值存儲在ROM中,輸出波形的頻率公示如式(3)所示。

本設計的頻率分辨率為0.1 Hz,頻率的調節范圍為0.1~100 Hz。另外所選用的芯片晶振的頻率為50 MHz,經過倍頻后得到的系統時鐘為100 MHz。根據設計要求取N=30,則輸出頻率分辨率(單位:Hz)為:

[Δf=fclk2N=100×106230=0.093≈0.1] ? ? ? (4)

可知,要實現頻率0.1~100 Hz的調節,則fcw的取值為1~210。由于使用的FPGA內部ROM容量有限,因此這里選用累加器的高10位對ROM進行尋址,即存儲1 024個正弦波幅值。

4.2 ?三角載波模塊

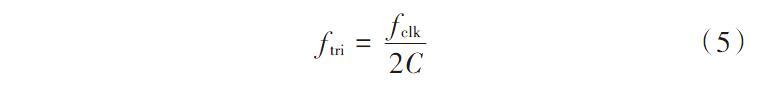

三角波是常用的載波信號,基于FPGA實現三角載波的方法有很多,為了節省存儲空間及設計的載波的待定輸出,直接用Verilog HDL語言編程實現。所設計的三角載波是根據加減循環計數器原理生成,輸出三角波的頻率ftri為:

[ftri=fclk2C] ? ? ? ? ? ? ? ? ? (5)

式中:C為三角波的峰值;fclk為系統參考時鐘。

輸出三角波的頻率與所控制的MOS管的開關頻率大小相同,根據式(5)可以求出C的值。

4.3 ?帶死區的比較模塊

由于MOS管的導通與關斷都需要時間,為了防止橋臂上的兩個MOS管同時導通而發生短路的情況,需要使同相上下橋臂驅動信號錯開一個死區時間[10?11]。因此,在設計時必須設置死區時間,死區的大小由具體的功率器件決定。本文將采用狀態機的設計方法把死區模塊與比較模塊綜合在一起,節省了存儲空間,部分代碼如下:

always@(current_state)

begin

case(current_state)

s0:begin DH_r<=0;DL_r<=0;end

s1:begin DH_r<=0;DL_r<=1;end

s2:begin DH_r<=0;DL_r<=0;end

s3:begin DH_r<=1;DL_r<=0;end

endcase

end

基于正弦調制波的生成原理,可以生成0°,120°和240°三相正弦波,將三相正弦波與相同的三角載波送入帶死區的比較模塊進行比較,當正弦波的輸出值大于等于三角波的輸出值時,比較器輸出高電平,反之則反。圖6為三相SPWM波設計原理圖。

4.4 ?PWM模塊

為了調節直流母線電壓設計了PWM模塊,該模塊的功能是生成一個占空比可調的PWM波,其主要由可逆計數器(輸出變化范圍50~450)、三角波計數器(最大計數值為500)和比較器三部分組成。圖7為PWM模塊的設計原理圖。

5 ?基于QuartusⅡ的仿真與實驗

5.1 ?SPWM模塊仿真

本文采用Modelsim軟件對程序進行仿真,圖8為正弦調制波仿真波形。其中頻率控制字fcw分別設置為300,600,900,而且設置時間長度相同,從圖中可以發現,輸出波形的頻率與頻率控制字成正比。

圖9為三角載波仿真波形,在時鐘上升沿實現計數器加減,所生成的三角波是對稱波。

圖10為三相SPWM仿真波形,從圖中可以看出三相SPWM波相位互差120°,每一相兩路波形為互補關系,且存在死區時間。

5.2 ?PWM模塊仿真

PWM模塊仿真波形如圖11所示。通過數字板上的按鈕來控制可逆計數器的增減,從而來控制PWM波的占空比。從圖中可以看出,當計數器為450和50時,PWM波的占空比差別比較明顯。

5.3 ?實驗結果

圖12為數字示波器輸出的U相SPWM波形,從圖中可以看出,U相兩路波形互補且之間存在死區時間。圖13為PWM波形,通過改變計數器的數值來改變其占空比,輸出信號電平是3.3 V。

根據本文所設計的變頻變壓電源的基本結構制作了樣機。由上面理論分析知,當直流母線電壓為50 V,改變頻率控制字、調制度M以及PWM波的占空比D,就可以實現變頻電源的調頻調壓,實驗結果如下:

1) 頻率控制字fcw=200,調制度M=0.8,占空比D=0.8時,輸出的電壓波形如圖14所示。

2) 頻率控制字fcw=250,調制度M=0.7,占空比D=0.7時,輸出的電壓波形如圖15所示。

3) 頻率控制字fcw=300,調制度M=0.7,占空比D=0.7時,輸出的電壓波形如圖16所示。

6 ?結 ?語

根據變頻電源高頻化、數字化的發展方向,本文研究了基于FPGA的三相SPWM變頻變壓電源,分別設計了變頻變壓電源的數字控制電路和硬件模擬電路。基于FPGA產生的三相SPWM波和PWM波分別控制著逆變主電路和直流母線調壓電路,通過改變頻率控制字、調制度以及占空比來實現電源的調頻調壓。各模塊的仿真結果滿足了系統的設計要求,實驗驗證了本設計方案的可行性。結果表明,該變頻變壓電源輸出波形質量較好、性能穩定、運行可靠、實時性強、可在線調節,是較為理想的變頻變壓電源。這對于變頻變壓電源進一步推廣應用有重要的實際意義。

參考文獻

[1] 張鵬超.基于DSP的三相逆變電源研制[J].電源技術,2011,35(9):1154?1156.

[2] 王文蓉.基于SVPWM技術的三相變頻變幅逆變電源[J].儀表技術與傳感器,2017(1):169?172.

[3] 劉健,張號,曾華,等.基于FPGA技術的三電平自然采樣SPWM全數字化理論研究與實現[J].中國電機工程學報,2017,37(5):1498?1506.

[4] 向毅.基于FPGA的電阻焊電源的研究與設計[D].保定:河北大學,2017.

[5] 李能菲,謝苗苗.基于FPGA的逆變控制系統的研究[J].現代電子技術,2012,35(14):189?191.

[6] 鄒祎,馬曉軍,魏曙光.基于FPGA的大功率電力電子器件仿真[J].電力電子技術,2017,51(5):115?117.

[7] 劉必旺,王寶忠.基于FPGA控制的開關電源的仿真與設計[J].科學技術與工程,2012,31(12):8281?8286.

[8] 項春萍.基于DDS的高速定時同步方法[J].現代電子技術,2012,35(9):68?69.

[9] 張興紅,蔡偉,邱磊,等.基于FPGA與DDS 技術的可調超聲波驅動電源設計[J].儀表技術與傳感器,2015(6):84?87.

[10] ABRONZINI U, ATTAIANESE C, DARPINO M, et al. Steady?state dead?time compensation in VSI [J]. IEEE transactions on industrial electronics, 2016, 63(9): 5858?5866.

[11] 賴梓揚,張希,張智敏,等.計及系統性能提升的諧振式無線充電開關器件死區優化[J].電力系統自動化,2017,41(14):176?181.

作者簡介:徐 ?彬(1992—),男,安徽阜陽人,碩士研究生,主要研究方向為精密驅動與控制技術。

王傳禮(1964—),男,博士,教授,博士生導師,主要研究方向為流體傳動與控制技術。