基于quartus 制作微處理器

黃峻杰

(重慶郵電大學(xué) 電子信息工程(中美),重慶 400065)

0 引 言

21 世紀(jì),各式各樣的技術(shù)和設(shè)備不停更新?lián)Q代,微處理器也不例外。對(duì)于微處理器的設(shè)計(jì),源于其內(nèi)部的功能選擇。對(duì)于不同功能的微處理器,其內(nèi)部的邏輯結(jié)構(gòu)也會(huì)產(chǎn)生多種變化。本文將完全集成、測試和演示微處理器的所有部分,完成控制單元的設(shè)計(jì),以獲取和執(zhí)行所有指令。測試將在ModelSim 上進(jìn)行仿真,并通過電路板進(jìn)行演示。

1 微處理器的構(gòu)造

利用quartus 軟件進(jìn)行制作微處理器,需要掌握微處理器的構(gòu)造。微處理器由IR、AC、PC、ALU、寄存器以及集成的中央處理器組成,其中IR、AC、PC、ALU、寄存器比較簡單,但是中央處理器的運(yùn)用比較困難[1]。筆者采用狀態(tài)轉(zhuǎn)移寄存器,分階段對(duì)中央處理器進(jìn)行編輯。對(duì)中央處理器的內(nèi)部組成理解,采用opcode 操作數(shù)進(jìn)行仿真操作。opcode 代表ALU 執(zhí)行的操作,如加減乘除,是計(jì)算機(jī)最基本的部分。

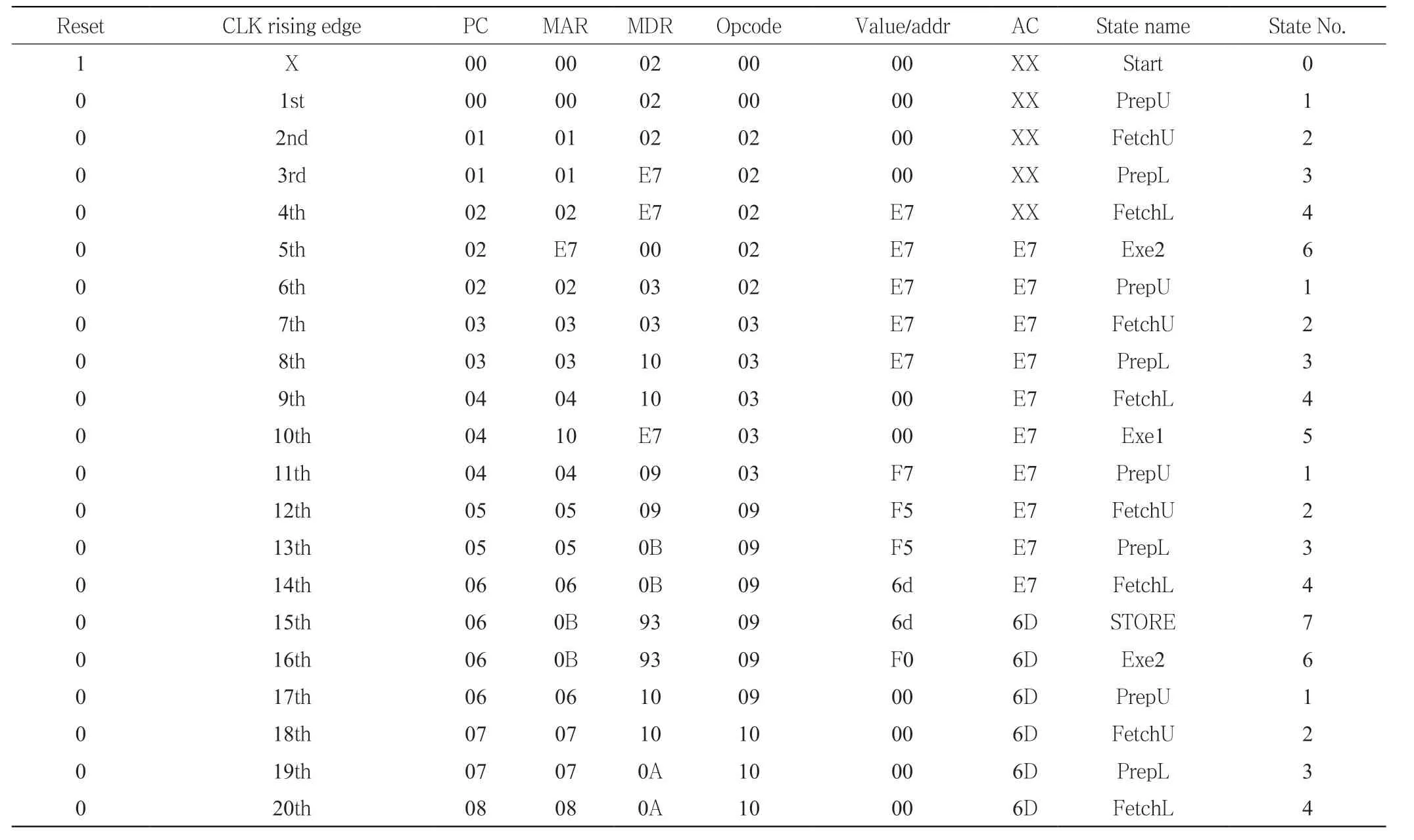

通過定義和命名其他狀態(tài)完成表1 內(nèi)容,以控制指令集中每個(gè)指令的執(zhí)行。

IR 內(nèi)部包括低位處理器和高位處理器[2]。低位主要負(fù)責(zé)向隨機(jī)接入寄存器RAM 輸入數(shù)據(jù)(類似于計(jì)算機(jī)構(gòu)造中的鍵盤輸入)與讀取;高位主要向ALU 計(jì)算器中輸入內(nèi)容和操作數(shù),而操作數(shù)決定微處理器的功能。PC 內(nèi)部構(gòu)造主要是地址的尋址和棧中數(shù)據(jù)的存儲(chǔ);AC 類寄存器主要負(fù)責(zé)數(shù)據(jù)的處理。

下面使用給定的存儲(chǔ)器數(shù)據(jù),在執(zhí)行每條指令時(shí)找出存儲(chǔ)在每個(gè)寄存器中的數(shù)據(jù),結(jié)果如表2 所示。

2 控制單元修改后的系統(tǒng)Verilog 代碼

控制單元修改后的系統(tǒng)Verilog 代碼如下。

//Huang junjie 2017215089

module control_unit2(input logic [7:0] opcode,

input logic NFLG, ZFLG, RESET, CLK, output logic[3:0] STATE,

output logic LOAD_AC, output logic LOAD_IRU,output logic LOAD_IRL, output logic LOAD_PC, output logic INCR_PC, output logic FETCH,

output logic STORE_MEM);

typedef enum logic [0:3] {START, PREPU, FETCHU,PREPL, FETCHL, STORE,

表1 相關(guān)狀態(tài)的定義和命名

表2 存儲(chǔ)在每個(gè)寄存器中的數(shù)據(jù)情況

executive1, executive2, JUMP} statetype;

statetype state, nextstate;

always_ff@(negedge CLK, posedge RESET) if(RESET)state <= START;

else state <=nextstate;

always_comb case(state)

START: nextstate=PREPU; //first run the prepu to producethe

opcode

IRL)

PREPU: nextstate = FETCHU;

FETCHU:case(opcode) //opcode default 8’h00:nextstate =PREPU;

8’h04: nextstate = executive1; default: nextstate =PREPL;

endcase

PREPL: nextstate=FETCHL; //enter the alu operation FETCHL:case(opcode)

8’h02: nextstate = executive1; //the alu who uses value

8’h06: nextstate =executive1; 8’h08: nextstate=executive1; 8’h0E: nextstate = executive1; 8’h0F:nextstate =executive1;

8’h01: nextstate = executive2; //the alu who uses MDR(from 8’h05: nextstate =executive2;

8’h07: nextstate =executive2;

8’h09: nextstate = executive2; 8’h0A: nextstate= executive2; 8’h0B: nextstate = executive2; 8’h0C:nextstate = executive2; 8’h0D: nextstate =executive2;

8’h03: nextstate = STORE; //Store the address

8’h10: nextstate= JUMP; // choose which jump circle 8’h11: nextstate = (NFLG)?JUMP:PREPU; //if NFLG=1,jump,or

get into prepu

8’h12: nextstate = (~NFLG)?JUMP:PREPU;

8’h13: nextstate = (ZFLG)?JUMP:PREPU;

8’h14: nextstate = (~ZFLG)?JUMP:PREPU; default:nextstate = PREPU;

endcase

executive1: nextstate = PREPU;

executive2: nextstate = executive1; STORE: nextstate =PREPU;

JUMP: nextstate = PREPU; endcase

assign FETCH = (state ==PREPU || state ==PREPL ||state == FETCHU || state == FETCHL);

assign LOAD_IRU = (state == FETCHU); assign LOAD_IRL = (state == FETCHL);

assign INCR_PC = (state == FETCHU || state ==FETCHL); assign LOAD_AC = (state == executive1); //relate to value assign STORE_MEM = (state == STORE);

assign LOAD_PC = (state == JUMP); assign STATE =state;

endmodule

3 模式選擇單元的系統(tǒng)Verilog 代碼

模式選擇單元的系統(tǒng)Verilog 代碼如下。

//Huangjunjie this is used for the PC,MAR,MDR module Muxright(input logic A, B,

input logic Mode, output logic Z);

always_comb if(Mode) Z = B; else Z = A;

Endmodule

//Huangjunjie this is used for the LOAD_AC,LOAD_PC,etc module Muxleft(input logic [7:0]A, B,

input logic Mode, output logic [7:0]Z);

always_comb if(Mode) Z = B; else Z = A;

endmodule

4 電路圖的仿真框圖

電路圖的仿真框圖,如圖1 所示,涉及微處理器的內(nèi)部完整構(gòu)造。

圖1 電路圖的仿真框圖

5 仿真波形圖

仿真波形可用于檢驗(yàn)微處理器的功能是否正確,如圖2 所示。

圖2 仿真波形圖

可以發(fā)現(xiàn),波形與計(jì)算的波形相同。就像以clk 的第一個(gè)邊緣為例,MDR 加載到02,并且復(fù)位在狀態(tài)1下為低電平有效。操作碼變?yōu)?2,PC 添加到2,并進(jìn)入ALU。

6 結(jié) 論

微處理器的主要作用是執(zhí)行各種操作運(yùn)算,對(duì)于數(shù)的操作難易程度主要看微處理器的功能是否強(qiáng)大。微處理器的操作主要看中央處理器的運(yùn)算操作能力。本文利用軟件仿真的微處理器的代碼邏輯是否清晰,主要是循環(huán)利用PC 和ALU 交替進(jìn)行操作,而中央處理器主要負(fù)責(zé)循環(huán)遞歸的進(jìn)行操作者的命令。quartus軟件對(duì)于這類微處理器的操作比較方便,擁有最基礎(chǔ)的合成軟件邏輯門和高階寄存器。本文提及的system verilog 代碼目前只能在quartus 上執(zhí)行。這類sv 代碼邏輯清晰,電路結(jié)構(gòu)十分嚴(yán)謹(jǐn),對(duì)于最后集成電路的焊接、光刻、對(duì)照也十分清晰。