基于可編程SOC的圖像邊緣檢測系統(tǒng)

胡龍寶 李丕丁

摘 要:隨著人工智能的不斷發(fā)展,云計算面臨數(shù)據(jù)量大、實時性低等問題。為了解決該問題,一種新的計算方式——邊緣計算進入了人們的視野。邊緣計算推動人工智能走向嵌入式系統(tǒng),與傳統(tǒng)嵌入系統(tǒng)相比,邊緣人工智能要復雜得多,傳統(tǒng)嵌入式設(shè)備計算能力弱、效率低的問題更為突出。基于Xilinx公司Zynq-7000系列的全可編程SOC完成系統(tǒng)設(shè)計,實現(xiàn)對視頻的邊緣檢測。測試結(jié)果顯示,硬件邊緣檢測速度比純軟件邊緣檢測速度快10倍,為邊緣人工智能在嵌入式應用方面提供了可行方向。

關(guān)鍵詞:邊緣人工智能;邊緣計算;可編程SOC;軟硬件協(xié)同;邊緣檢測;嵌入式應用

DOI:10. 11907/rjdk. 191606

中圖分類號:TP317.4?? 文獻標識碼:A??????????????? 文章編號:1672-7800(2020)003-0244-04

Image Edge Detection System Based on Programmable SOC

HU Long-bao, LI Pi-ding

(School of Medical Devices and Food Engineering, University of Shanghai for Science and Technology, Shanghai 200093, China)

Abstract: With the continuous development of artificial intelligence, cloud computing is facing the problems of large amount of data and low real-time. To solve this problem, a new computing method, edge computing, has come into peoples vision. Edge computing drives AI to embedded systems. Compared with traditional embedded systems, edge AI is much more complex. Traditional embedded devices have weak computing power and low efficiency. In this paper, based on Xilinx Zynq-7000 series of fully programmable SOC to complete the system design, to achieve video edge detection. The test results show that the speed of hardware edge detection is 10 times faster than that of software edge detection, which provides a feasible direction for the application of edge artificial intelligence in embedded system.

Key Words: edge artificial intelligence; edge computing; programmable SOC; software and hardware cooperation; edge detection; embedded applications

0 引言

云計算技術(shù)能夠?qū)⒋罅坑嬎阗Y源、存儲資源與軟件資源鏈接在一起, 形成巨大規(guī)模的共享虛擬IT資源池, 為遠程計算機用戶提供強大的計算能力和大量存儲空間[1-2],但隨著網(wǎng)絡(luò)邊緣檢測設(shè)備的迅速增加,云計算很難實現(xiàn)如此龐大規(guī)模數(shù)量的即時計算,無法保證應用的實時性[3]。如一輛自動駕駛的汽車每秒會產(chǎn)生1GB以上的數(shù)據(jù)[4],并且還要求對這些數(shù)據(jù)進行實時處理。大量自動駕駛的汽車同時向云服務器請求計算會占用大量內(nèi)存、計算資源和帶寬[5],而且在數(shù)據(jù)傳輸過程中任何延時都可能導致車禍發(fā)生。

因此,邊緣計算的重要性尤為突出。邊緣計算是指將計算任務在接近本地數(shù)據(jù)源的計算資源上運行, 實現(xiàn)數(shù)據(jù)就近處理[6-7]。邊緣計算有以下3個優(yōu)點:①減輕了網(wǎng)絡(luò)帶寬和數(shù)據(jù)中心功耗的壓力;②更快的傳輸和響應速度;③擺脫了網(wǎng)絡(luò)環(huán)境制約,也更加安全[8-9]。

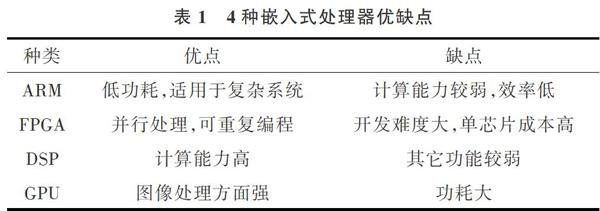

邊緣計算使用的嵌入式處理器大致分為ARM、FPGA、DSP和GPU。4種嵌入式處理器優(yōu)缺點如表1所示。

面向視頻監(jiān)控、汽車駕駛輔助、航空與國防等市場領(lǐng)域的新型應用,ARM具有比較強的事務管理功能,可以用于運行界面及應用程序等,其優(yōu)勢主要體現(xiàn)在控制方面,但在計算方面比較吃力;DSP主要是用來計算,比如進行加密解密、調(diào)制解調(diào)等,優(yōu)勢是強大的數(shù)據(jù)處理能力和較高的運行速度;FPGA適合于控制功能算法簡單且含有大量重復計算的工程使用,面對復雜控制實現(xiàn)難度大;GPU主要用于圖像處理,不適用于控制。單一種類處理器的嵌入式方案已無法滿足邊緣人工智能計算量大、低延時的要求。

針對以上問題,本文采用Zynq-7000系列的全可編程SOC芯片完成軟硬件協(xié)同設(shè)計[10],以雙核ARM為核心 ,高性能FPGA為外設(shè),將復雜算法通過Vivado高層次綜合(High-level Synthesis,HLS)工具優(yōu)化,將優(yōu)化后的算法生成硬件模塊在ARM上加載,通過AXI4總線實現(xiàn)兩者數(shù)據(jù)交互[11-12]。

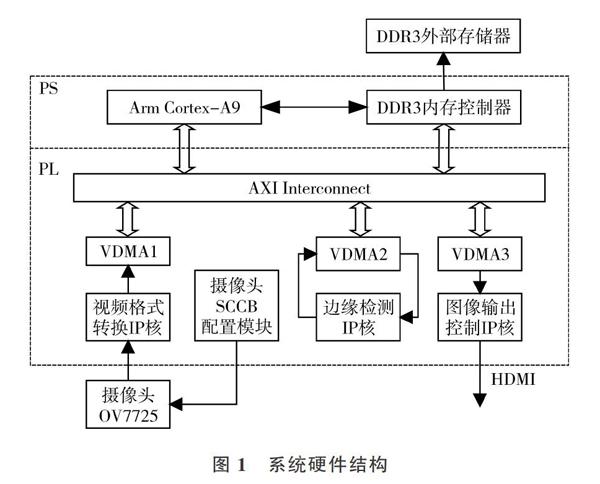

1 系統(tǒng)硬件結(jié)構(gòu)設(shè)計

本系統(tǒng)在ARM處理器上搭建Linux系統(tǒng),使用AXI4總線實現(xiàn)Zynq的可編程邏輯(Progarmmable Logic,PL)和處理器系統(tǒng)(Processing System,PS)之間的大量數(shù)據(jù)傳輸[13]。使用Xilinx公司的FPGA開發(fā)工具Vivado2017.4設(shè)計硬件模塊并搭建系統(tǒng)。系統(tǒng)硬件結(jié)構(gòu)如圖1所示。

其中,PL部分負責圖像采集、邊緣檢測、圖像顯示,PS部分負責內(nèi)存單元DDR3的數(shù)據(jù)存取和人機交互界面。

硬件系統(tǒng)包括3個模塊:圖像采集模塊、邊緣檢測模塊、圖像顯示模塊。

1.1 圖像采集模塊

圖像采集模塊包括OV7725攝像頭及其周圍電路。OV7725攝像頭通過CEP(Cmos Expand Port)與ZYNQ-7000系列的開發(fā)板連接,可輸出640×480分辨率、16位色彩深度的圖像信息[14];OV7725攝像頭一個時鐘周期只能寫入8位數(shù)據(jù),因此在視頻格式轉(zhuǎn)換IP中將前后兩個8位數(shù)據(jù)合并成16位數(shù)據(jù),得到RGB565類型數(shù)據(jù),再將數(shù)據(jù)擴充為RGB888格式方便轉(zhuǎn)成AXI4-Stream協(xié)議,最后通過VDMA1模塊通過AXI_HP接口將數(shù)據(jù)存入PS端的DDR3緩存。

1.2 基于HLS的邊緣檢測模塊

Vivado HLS工具是Xilinx推出的高層次綜合工具,能夠?qū)、C++、System C代碼綜合成硬件電路,支持浮點運算,并封裝多種圖像處理函數(shù)核數(shù)學運算函數(shù),相對于Verilog實現(xiàn)硬件邊緣檢測模塊,開發(fā)過程更簡單[15-16]。HLS工具還提供了OpenCV的函數(shù)庫,可以直接調(diào)用其中的圖像處理函數(shù)[17]。

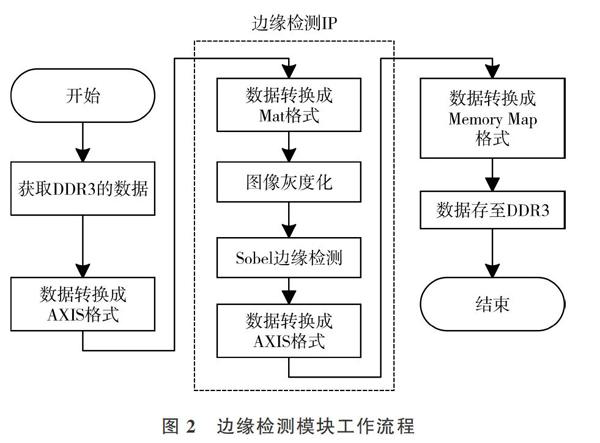

邊緣檢測模塊的工作流程如圖2所示。

在邊緣檢測IP 中,將數(shù)據(jù)轉(zhuǎn)換成Mat格式,將圖像灰度化后調(diào)用hls::Duplicate函數(shù)將灰度圖復制成兩路圖像,對兩路圖像分別進行橫向和縱向Sobel邊緣檢測,將兩路圖像結(jié)果相加,得到更加明顯的邊緣檢測圖像。

Sobel算子根據(jù)像素點上、下、左、右鄰點灰度加權(quán)差,在邊緣處達到極值這一現(xiàn)象時檢測邊緣。它對噪聲具有平滑作用,能提供較為精確的邊緣方向信息,但邊緣定位精度不夠高。當對精度要求不是很高時,是一種較為常用的邊緣檢測方法。

1.3 圖像顯示模塊

該部分包括HDMI輸出模塊和相應輸出時序控制模塊。輸出時序控制模塊由Vivado自帶的IP核VTC(Video Timing Controller)實現(xiàn),通過配置VTC的輸出視頻分辨率和時鐘,可以輸出行同步信號和場同步信號,輸出模塊按照同步信號將視頻傳輸?shù)紿DMI顯示器上。

2 軟件系統(tǒng)設(shè)計

2.1 嵌入式Linux系統(tǒng)搭建

為了在ARM處理器上進行人機交互界面程序開發(fā)以及其它邏輯控制,需要在ARM上移植嵌入式Linux系統(tǒng)和QT函數(shù)庫[18]。

系統(tǒng)移植包含以下7個步驟:①搭建編譯環(huán)境;②編譯u-boot啟動引導文件;③配置設(shè)備樹文件;④編譯內(nèi)核;⑤制作文件系統(tǒng);⑥生成BOOT.bin文件;⑦編譯Qt庫,生成Qt鏡像文件;⑧將BOOT.bin、uImage、devicetree.dtb、uramdisk.image.gz、Qt.img文件拷貝至啟動SD卡。

設(shè)置開發(fā)板為SD卡啟動模式,啟動開發(fā)板可以看到Linux啟動界面,完成嵌入式系統(tǒng)移植。

2.2 圖像采集驅(qū)動

圖像采集驅(qū)動主要功能是通過SCCB協(xié)議初始化OV7725攝像頭,通過GPIO接口對圖像采集模塊寄存器進行配置。系統(tǒng)中采用Platform驅(qū)動模型,Platform總線是虛擬平臺總線,是Linux設(shè)備驅(qū)動模型為了保持設(shè)備驅(qū)動的統(tǒng)一性而虛擬出來的總線。

總線將設(shè)備和驅(qū)動綁定,系統(tǒng)每注冊一個設(shè)備時,會尋找與之匹配的驅(qū)動;相應地,系統(tǒng)每注冊一個驅(qū)動時,會尋找與之匹配的設(shè)備,而匹配由總線完成。驅(qū)動包含以下幾個主要函數(shù):①probe函數(shù):也被稱為探針函數(shù),用于檢測總線上該驅(qū)動對應的設(shè)備;②remove函數(shù):用于移除總線上驅(qū)動;③read函數(shù):從模塊寄存器讀取數(shù)據(jù);④write函數(shù):向模塊寄存器寫入數(shù)據(jù)。

2.3 邊緣檢測模塊驅(qū)動

用戶空間I/O框架(Userspace I/O Framework)可直接映射物理地址,文中圖像預處理模塊驅(qū)動將模塊的AXI Lite寄存器基地址映射出來,對寄存器進行操作;通過Vivado HLS綜合的IP,會自動生成Linux下UIO用戶端的驅(qū)動代碼,可以直接使用。

邊緣檢測模塊驅(qū)動主要包括幾個函數(shù):①XEdge_detection_Initialize:初始化模塊,從/dev下找到邊緣檢測模塊對應設(shè)備,并獲得句柄,將模塊的寄存器地址映射到內(nèi)存;②XEdge_detection_Release:釋放句柄和取消內(nèi)存映射;③XEdge_detection_IsReady:檢測模塊是否準備好處理下一張圖片;④XEdge_detection_SetRows:設(shè)置圖像高度;⑤XEdge_detection_SetCols:設(shè)置圖像寬度;⑥XEdge_detection_Start:開始運行邊緣檢測模塊。

2.4 VDMA Framebuffer驅(qū)動

AXI VDMA是Xilinx提供的IP,用于將AXI Stream格式數(shù)據(jù)流轉(zhuǎn)換為Memory Map格式,或?qū)emory Map格式的數(shù)據(jù)轉(zhuǎn)換為AXI Stream數(shù)據(jù)流,從而實現(xiàn)與DDR3通信[19]。AXI VDMA結(jié)構(gòu)框架如圖3所示。

可以看出,VDMA的主要接口有3個,分別為AXI4 Memory Map、AXI4-Lite、AXI4-Stream。

AXI4-Lite:用于讀寫VDMA內(nèi)部寄存器,從而實現(xiàn)對VDMA的控制和狀態(tài)獲取。

AXI4-Stream:寫通道(s2mm):VDMA獲取來自axis接口的數(shù)據(jù)并將之寫入幀存;讀通道(mm2s):VDMA從幀存讀取數(shù)據(jù),然后送至axis接口輸出。

AXI4 Memory Map:用于操作DDR,通過互聯(lián)模塊連接至Zynq的HP接口[20]。

本系統(tǒng)通過VDMA3實現(xiàn)Framebuffer的顯示功能,因此需要VDMA3從DDR3中讀取數(shù)據(jù),輸出到HDMI顯示器上。

3 系統(tǒng)測試及結(jié)果分析

為了對搭建的視頻處理系統(tǒng)進行功能及性能測試,對采集到的視頻圖像分別用純軟件和軟硬件結(jié)合的方式進行邊緣檢測處理。邊緣檢測是圖像處理和計算機視覺中,尤其是特征提取中的一個研究領(lǐng)域[21]。Soble邊緣檢測算法比較簡單,雖然Soble邊緣檢測準確度低于Canny邊緣檢測,但是實際應用中,Sobel邊緣效率比Canny邊緣檢測效率要高。在要求效率、忽視細節(jié)紋理時,Sobel邊緣檢測成為首選。

系統(tǒng)實現(xiàn)Sobel邊緣檢測算法,效果對比如圖4所示。

圖4(a)為純軟件使用OpenCV庫實現(xiàn)邊緣檢測算法效果,圖4(b)為使用HLS工具實現(xiàn)邊緣檢測算法效果。

軟硬件兩種邊緣檢測方式處理所需時間如表2所示。

從圖4和表2可以看出,軟硬件結(jié)合方法實現(xiàn)邊緣檢測算法,與純ARM實現(xiàn)圖像處理算法效果基本相同,但處理速度方面有很大提升。本次邊緣檢測實驗中軟硬件協(xié)同處理比純軟件處理速度提高10.89倍。

4 結(jié)語

本文設(shè)計并實現(xiàn)了基于可編程SOC的邊緣檢測系統(tǒng),在系統(tǒng)中使用HLS工具生成一個基于ZYNQ PL部分的硬件Sobel邊緣檢測IP核,并與軟件邊緣檢測進行了比較。結(jié)果表明,硬件邊緣檢測與軟件邊緣檢測效果基本相同,但在耗時上,前者只需要后者的1/10。這使得基于嵌入式系統(tǒng)的圖像處理實時性大幅度提升,為邊緣人工智能中邊緣設(shè)備處理數(shù)據(jù)量大、時間長的問題提供新的方向。該設(shè)計方案可應用于自動駕駛、機器人以及智能監(jiān)控等場景,減少嵌入式系統(tǒng)計算耗時、增強系統(tǒng)運行可靠性、提高數(shù)據(jù)隱私性,同時可以通過網(wǎng)絡(luò)將結(jié)果傳輸至云服務器進行大數(shù)據(jù)分析。

參考文獻:

[1]張玉. 虛擬化技術(shù)在智慧城市建設(shè)中的應用[J]. 中國高新技術(shù)企業(yè), 2014, (34): 43-44.

[2]馮登國, 張敏, 張妍,等. 云計算安全研究[J]. 軟件學報,2011,22(1): 71-83.

[3]CHANDRA S R,YAFENG W. Cloud things construction - the integration of Internet of things and cloud computing[J]. Future Generation Computer Systems,2016,56(C):684-700.

[4]STAUDENMAIER M, HERRMANN S. 基于視覺的駕駛員輔助嵌入式系統(tǒng)[J]. 中國電子商情:基礎(chǔ)電子,2014(9): 38-43.

[5]施巍松,孫輝,陳彥明. 基于邊緣計算的新型視頻監(jiān)控系統(tǒng)展望[J]. 自動化博覽,2018,35(12):60-63.

[6]徐恩慶,董恩然. 云計算與邊緣計算協(xié)同發(fā)展的探索與實踐[J].? 通信世界,2019(9): 46-47.

[7]SHARMAN R,BIOOKAGHAZADEH S,LI BAOXIN, et al. Are existing knowledge transfer techniques effective for deep learning with edge devices?[C]. IEEE International Conference on Edge Computing,2018:42-49.

[8]施巍松,張星洲,王一帆,等. 邊緣計算:現(xiàn)狀與展望[J]. 計算機研究與發(fā)展, 2019,56(1): 69-89.

[9]周知,于帥,陳旭. 邊緣智能:邊緣計算與人工智能融合的新范式[J]. 大數(shù)據(jù),2019,5(2): 53-63.

[10]李朗,張索非,楊浩. 基于Zynq-7000的視頻處理系統(tǒng)框架設(shè)計[J]. 計算機技術(shù)與發(fā)展, 2017,27(5):192-195.

[11]XILINX. Vivado design suite tutorial high-level synthesis[EB/OL]. https://www.xilinx.com/support/doc-umentation/sw_manuals/xilinx 2017_1/ug871-vivado-high-level-synthesis-tutorial.pdf.

[12]XILINX. Vivado design suite user guide high-level synthesis[EB/OL]. https://www.xilinx.com/support/doc-umentation/sw_manuals/xilinx 2017_1/ug902-vivado-high-level-synthesis.pdf.

[13]鄧健峰,謝云. 基于FPGA+ARM的視頻采集平臺設(shè)計與實現(xiàn)[J]. 工業(yè)控制計算機,2017,30(12): 97-98.

[14]曾永西,黃梅紅,陳偉豪. 基于FPGA+OV7725的視頻監(jiān)控系統(tǒng)[J]. 福建電腦, 2015, 31(09): 8-9,39.

[15]黨宏社,王黎,王曉倩. 基于Vivado HLS的FPGA開發(fā)與應用研究[J]. 陜西科技大學學報:自然科學版,2015,33(1):155-159.

[16]郭豐收. Xilinx FPGA/Zynq設(shè)計中使用HLS實現(xiàn)OpenCV的開發(fā)流程[J]. 電子產(chǎn)品世界,2014,21(Z1):50-52.

[17]趙睿. 基于Xilinx的HLS實現(xiàn)OpenCV的研究與設(shè)計[J]. 科技創(chuàng)新與應用, 2016(21): 56-57.

[18]賀丹丹,張帆,劉峰. 嵌入式Linux系統(tǒng)開發(fā)教程[M]. 北京: 清華大學出版社,2010.

[19]Xilinx. Zynq-7000 SoC Technical reference manual[EB/OL]. https://www.xilinx.com/support/doc-umentation/user_guides/ug585-Zynq- 7000-TRM.pdf.

[20]陸佳華,潘祖龍,彭競宇. 嵌入式系統(tǒng)軟硬件協(xié)同設(shè)計實戰(zhàn)指南[M]. 北京:機械工業(yè)出版社, 2014.

[21]溫建飛,岳鳳英,李永紅. 基于FPGA硬件架構(gòu)的實時高速圖像特征檢測系統(tǒng)[J]. 電子世界,2015(21):124-125.

(責任編輯:孫 娟)

收稿日期:2019-05-09

作者簡介:胡龍寶(1996-),男,上海理工大學醫(yī)療器械與食品學院碩士研究生,研究方向為醫(yī)療電子儀器;李丕丁(1973-),男,博士,上海理工大學醫(yī)療器械與食品學院講師、碩士生導師,研究方向為生物醫(yī)學信號處理、醫(yī)療電子儀器。