基于FPGA的慣導姿態數據采集實驗系統設計

楊建華,馬 超,齊 華

(西安工業大學,電子信息工程學院,西安710021)

慣性導航產品INS(inertial navigation system)在制造中會產生標度因數誤差、安裝誤差、零偏誤差等,因此,需要特定的標定方法對產品參數進行補償以改善導航精度,標定平臺為一個帶高低溫箱的高精度三軸轉臺與標定系統[1-2]。為盡可能一次性標定較多產品,一般設計多個數據采集通道。慣導產品標定時,將其固定于三軸轉臺內框,在預置的溫度下,通過改變轉臺三軸位置以及旋轉速率,分別采集慣導產品的各種姿態數據[3-4]。姿態數據代入誤差模型方程中,可以解算出需要補償的誤差參數。數據通常以脈沖信號、電壓模擬量信號、串口數據等形式輸出。

為了幫助學生理解電子系統設計在工程實踐中的應用,提高學生從單元模塊設計到系統設計的能力以及數模混合設計的能力,在此設計了基于FPGA 的慣導姿態數據采集實驗系統[5-6]。針對數據采集系統在工程中的應用,完成了基于FPGA 的慣導姿態數據采集實驗系統的硬件系統搭建和數字邏輯電路設計,實現同時對48 路姿態數據以及4路溫度模擬量數據的信號調理、數字濾波及高精度數據采集。

1 數據采集系統功能結構

所設計的采集系統,能夠實現對慣性導航產品姿態數據的高速高精度采集,其控制核心采用Altera 的Cyclone V 系列5CEBA4F23C7N 型號FPGA芯片; 可以同時完成4 個慣導產品的自動標定,同時采集48 路脈沖信號,脈沖信號表示陀螺儀輸出的角速率和加速度計的線加速度,4 路表示產品溫度的電壓模擬量信號。采集數據通過USB 接口上傳到上位機進行進一步分析與處理。系統的功能結構如圖1 所示。

圖中,48 路脈沖信號通過光耦合器HCPL2630和施密特觸發器74LVT14,實現脈沖信號的隔離和整形;4 路電壓模擬量信號通過高速模數轉換器AD9627 實現模數轉換。在FPGA 芯片內部設計系統采集狀態機,根據數據地址狀態機按序每5 ms 讀取一次各個采集單元的數值,存入FPGA 內部設計的FIFO 中,然后通過USB 芯片發送到上位機,進行保存、處理和顯示。

2 試驗系統外圍電路設計

2.1 隔離及整形電路設計

圖1 數據采集系統功能結構Fig.1 Functional structure of data acquisition system

為保證實驗系統板能夠良好運行,需要對其輸入信號進行完全電氣隔離,防止轉臺運行過程中其它來源的電信號對測試系統產生干擾[7-8]。在此采用光電耦合器對輸入脈沖信號進行隔離,選用Fairchild 半導體公司生產的HCPL2630 芯片作為隔離芯片。

HCPL2630 為雙通道數字隔離,轉換速度可達10 MBit/s,輸出TTL 電平信號,輸出信號與輸入信號電平相反,其內部是以“電—光—電”信號的轉化方式來隔離輸入端和輸出端。

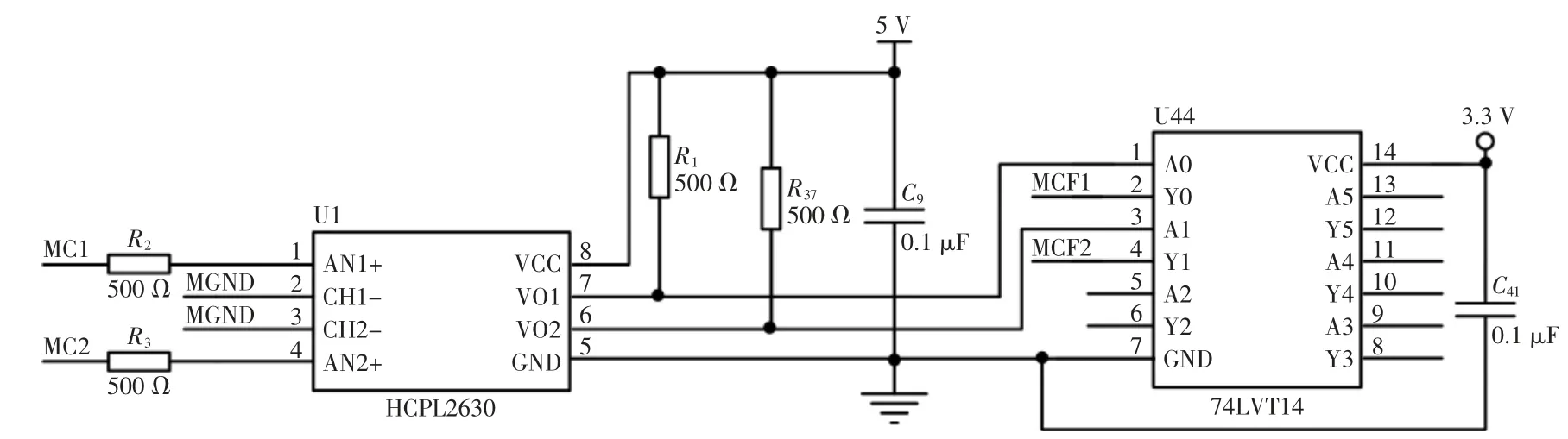

脈沖信號在經過雙通道數字隔離器HCPL2630后,變為TTL 電平信號,但是電平發生了反相,脈沖的上升沿和下降沿也不夠理想。選用Philips 公司的74LVT14 反相芯片,可使脈沖電平恢復到原來的邏輯,同時由于其施密特觸發方式,使得脈沖信號在下降沿和上升沿變得更加陡峭,利于后端計數電路進行準確計數。

實驗系統共48 路脈沖信號,其中一路脈沖信號的隔離與整形電路如圖2 所示。

圖2 脈沖信號隔離整形電路Fig.2 Circuit of pulse signal isolation and shaping

2.2 溫度采集電路設計

4 路溫度信號AD 采集采集電路如圖3 所示。先通過運放AD8055 和分壓電阻把-5~5 V 輸入的電壓縮小為-1~1 V。該范圍輸入電壓通過AD8138芯片,轉換為差分信號輸入到雙通道高速模數轉換器AD9627,FPGA 控制模數轉換器完成數據采集。

圖3 溫度信號采集電路Fig.3 Temperature signal acquisition circuit

3 基于FPGA 的系統數字邏輯電路設計

FPGA 內部數字邏輯電路主要設計脈沖信號數字濾波單元、高精度無縫計數單元、溫度數據采集單元和數據傳輸協調控制單元等邏輯電路。

3.1 脈沖信號數字濾波

慣導組件輸出的脈沖信號在采集前要經過轉臺滑環和長電纜線,在此過程中脈沖信號可能會發生畸變和疊加,產生一些干擾脈沖[9-10]。數字光耦(HCPL2630)可以隔離噪聲和濾除干擾,但對高頻干擾脈沖則無法消除。針對每一路計數電路,設計了數字邏輯濾波單元用以消除干擾脈沖,確保系統對脈沖信號采集和測量的準確性。

因慣導組件原始輸出固定脈寬的脈沖隊列,故采用閾值比較法進行濾波。將需要濾除干擾脈沖的最小脈沖寬度設為閾值,與輸入脈沖信號的脈寬比較,大于閾值的判定為有效信號,小于閾值的則判定為干擾信號。數字濾波電路邏輯結構如圖4 所示。

圖4 濾波原理Fig.4 Filter schematic

閾值為濾除干擾的最小脈寬設定值,可以通過上位機來進行閾值寬度設定。當輸入脈沖信號fin上升沿到來時,啟動計數器1,對基準時鐘f0計數,并將計數結果送入比較器與閾值作比較:當計數結果大于閾值時,比較器輸出低電平,控制觸發器將fout置高;當計數結果小于閾值時,比較器輸出高電平,觸發器輸出fout不變。

當fin的下降沿到來時,計數器1 停止計數,計數器2 啟動,該計數器設計為一個減法計數器,預設值為閾值,其借位輸出信號可產生高電平,取反后用作觸發器的清零端將fout置為低電平。計數器2 的實際作用是脈寬信號保持,在fin上升沿到來時,觸發器輸出fout信號將會有閾值乘以f0周期的延遲。為了保持脈沖信號的寬度和波形,計數器2將會延遲后再輸出清零信號,以保證fout輸出信號與輸入脈沖的脈寬基本一致。數字濾波單元仿真結果圖5 所示,d 為通過上位機設定的8 位最小脈寬閾值;f0為計數基準時鐘;頻率為50 MHz; fin為脈沖信號輸入;enable 為鎖存信號,fout為濾波后輸出信號。

由仿真結果可見該邏輯單元有效濾除了干擾脈沖信號。

3.2 高精度無縫計數

對慣導產品的性能測試中,需要對慣導產品輸出脈沖進行實時計數。該計數過程不僅要對每1 s的輸出脈沖進行計數,而且要對每5 ms 的輸出脈沖進行計數,同時在讀取5 ms 計數值時不中斷計數器工作。在此設計了無縫計數電路對慣導產品的輸出進行計數。單路脈沖信號無縫計數電路如圖6所示。

使用74161 計數器和74374 鎖存器實現帶鎖存功能的16 位計數器。該計數器可以一直處于不間斷工作狀態,每5 ms 的計數值最高可達65536,頻率最高可達13 MHz。對計數值的讀取是每5 ms的即時讀取,讀取過程中計數器正常計數,因此實現對輸入脈沖的無縫計數。

該電路不會產生累積誤差,由于計數器工作期間始終無需清零,5 ms 間隔內的計數值由微處理器將本次中斷讀取數值與上一次中斷讀取數值求差得到,而1 s 的計數值是將200 個5 ms 計數值疊加求得的,這樣就消除了每次清零可能帶來的±1 個計數誤差。

圖6 無縫計數電路Fig.6 Seamless counting circuit

3.3 數據采集協調控制數字邏輯單元

用Verilog 語言,在FPGA 內部設計數據傳輸協調控制狀態機模塊如圖7 所示,直接操作CY7C68013的FIFO 來完成讀寫控制。

圖7 狀態機模塊邏輯電路Fig.7 Logic circuit of state machine module

模塊中各引腳的功能如下:SLOE 為使能端;SLRD 為讀操作端;SLWR 為寫操作端;INPKTEND為主動發送操作端(當FIFO 上的數據小于規定大小,而又要強制上傳給PC 時使用);DATA_IN 為16位數據輸入總線;DATA_OUT 為16 位數據輸出總線;FLAGA 為FIFO空標志;FLAGB為FIFO滿標志;FIFO_ADR 實現對CY7C68013 中4 個大端點FIFO 的使能。IFCLK 可以引入外部時鐘(僅用于同步Slave FIFOs 模式)。FPGA 的引腳控制這些端口,達到對USB 端的存儲FIFO 進行操作的目的。

圖5 數字濾波電路仿真結果Fig.5 Simulation results of digital filter circuit

由于異步Slave FIFOs 模式的讀寫狀態簡單,穩定性好,系統采用異步方式讀取FIFO。狀態機中實現異步Slave FIFO 寫操作的狀態轉移如圖8 所示。

圖8 異步Slave FIFOs 的狀態機轉換Fig.8 State machine transition of asynchronous Slave FIFOs

各狀態的功能如下:

IDLE 為空閑狀態,什么都不做;

狀態1使FIFOADR[1:0]指向IN FIFO(即選擇CY68013 的4 個大數據量FIFO 中的1 個,固件程序已將此FIFO 配置為寫模式);

狀態2如果FIFO 滿標志為假(即FLAGC 引腳為高電平時),則進狀態3,否則在本狀態等待;

狀態3驅動數據到數據線上,使SLWR 有效(低電平),一個CLK_STATE 后再無效(高電平),以使FIFO 寫指針遞增,進狀態4;

狀態4如需傳輸更多的數,返回狀態2,否則進狀態IDLE。

4 系統測試與結果分析

在現有實驗條件下,對系統的性能指標進行了測試。系統測試硬件搭建如圖9 所示。使用Keysight 33210A 任意波形發生器(精度為±20×10-6/a)對實驗系統精度測試,為方便計算誤差,設置為0.1 kHz~6 MHz 內整數頻率點,信號發生器輸出頻率與系統測量所得頻率值對比結果見表1。

圖9 系統測試硬件Fig.9 System test hardware

表1 系統測量結果Tab.1 System measurement results

由表1 測量數據可知,系統可以獲得精度較高的頻率測量結果,相對誤差隨著頻率增大而減小,數據采集誤差符合系統設計標準。

5 結語

復雜數模混合系統設計是電子系統設計的重要內容之一,模擬電路與數字電路、單元電路與系統電路的有機結合,可以培養學生分析問題、解決實際工程實踐問題的能力,它一直是電子系統設計教學中的短板。基于FPGA 的慣導姿態數據采集實驗系統在課程設計的成功實施,既可使學生將所學的理論知識與工程實踐相結合,系統地理解模擬與數字系統的理論知識,又可使學生掌握復雜數模混合系統工程實踐知識,培養學生的工程實踐能力,達到工程教育認證對學生培養的要求。