基于FPGA的RS-232通信協議接口設計

燕伯峰 董永樂 余 佳 劉宇鵬 黃 欣 石浩淵

(1.內蒙古電力(集團)有限責任公司,內蒙古 呼和浩特 010020;2.內蒙古電力科學研究院,內蒙古 呼和浩特 010020)

0 引言

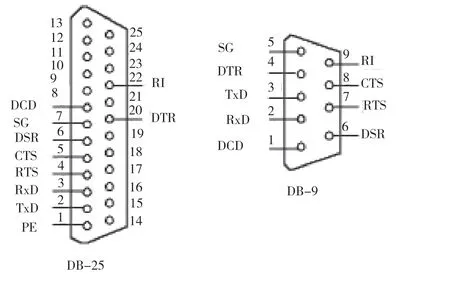

RS-232 接口是1970 年由美國電子工業協會(EIA)聯合貝爾系統、調制解調器廠家及計算機終端生產廠家共同制定的用于串行通信的標準[1]。常見的RS-232 串口有DB25 和DB9 2種,接口定義如圖1 所示。RS-232 通信協議因其低成本和高可靠性而被廣泛應用,加上其占用的I/O 口數量少,許多以嵌入式微處理器為核心的控制系統中常常采用該技術[2]。工業控制的RS-232 口一般只使用RXD、TXD、GND 3 條線,使用簡單方便。FPGA 即現場可編程門陣列,是在PAL、GAL、CPLD等可編程器件的基礎上發展而來,作為專用集成電路領域中的一種半定制電路,它既解決了定制電路生成周期長且內部電路不能更改的不足,又克服了原有的可編程器件門電路有限的缺點[3]。該文的邏輯設計是基于Altera 公司的Cyclone V 系列FPGA,型號為DE10-Nano,開發板上同時集成了Cortex-A9 ARM 處理器,提高了設計的靈活性。

1 RS-232協議介紹

RS-232 電平是負邏輯,即邏輯‘1’是-15V~ -5V,邏輯‘0’是+5 V~+15 V,與TTL 電平相反,使用時需要注意。RS-232 為串行異步通信,每一數據幀由起始位、數據位、奇偶校驗位(可省略)、停止位和線路空閑位組成[4],如圖2 所示。一般情況下,起始位為1 位,數據位為5、6、7或8 位,奇偶校驗位為1 位,停止位為1、1.5 或2 位。在無數據傳送時,傳送線為邏輯‘1’,處于空閑狀態,當檢測到低電平后,為數據傳輸的“起始位”,之后開始傳送數據位,低位在前,高位在后,發完數據位后,根據所發數據發送奇校驗位或偶校驗位,最后以一位高電平作為停止位結束該次數據傳送[5]。傳送的速率一般為9 600 bps 或115 200 bps 等。該文在RS-232 串口通信協議的基礎上,利用FPGA 對該協議進行模擬仿真,進行數據的接收與發送,并利用串口調試助手進行在線測試。之后,再利用FPGA 模擬一款電表計量芯片的數據存儲與交換的過程。

圖1 25 針及9 針串口引腳圖

2 FPGA模擬RS-232串口數據收發設計

串口發送的程序寫在uart_x 模塊中。在主程序模塊中首先調用gen_divd 模塊,在50M 主時鐘的基礎上分頻出115 200 bps 的時鐘作為串口數據發送的波特率。接著,調用uart_x 模塊以BCLK,Xmit cmdp,TxdBuf 為輸入,其中BCLK 為115 200 bps 的時鐘信號,作為發送數據的時鐘,Xmit cmdp 為wire 類型數據,作為一個數據傳輸的標志,在Xmit cmdp 由高變低的下一個上升沿開始發送數據,在TxdBuf 中為要發送的數據,從主模塊中傳遞過來。

在uart_x模塊中定義了6位狀態機,其中TXIDLE為空閑狀態,當無數據發送時處于該狀態,此時無操作。TXLode為裝載數據狀態,當接收到主模塊發來的Xmit cmdp 信號由0 轉到1 時,進入數據裝載狀態,將主模塊發過來的需要發送的數據裝載到TxdBufTmp 寄存器中,之后轉入TXStartBit 狀態中,發送0 到數據線中,作為起始信號。接著轉入TXDataBit 狀態,將TxdBufTmp 中的數據發送到數據線中,一位一位發送,低位在前,高位在后,發送完8位數據后,進入TXStopBit 狀態,發送1 到數據線,作為數據幀的停止位。最后進入TXDone 狀態,給TxDone 寄存器置1,表示發送完成,再進入TXIDLE 狀態,等待數據幀的到來。

串口接收程序主要在uart_r 模塊中實現。在主模塊中首先調用gen_divd 模塊,將主頻50M 時鐘分頻得到115 200×16 bps 的時鐘信號。該信號為串口通信波特率的16倍,方便將數據線上發送過來的數據在合適的位置接收進來,避免錯亂或出現毛刺影響數據接收。

在uart_r 模塊中,以CLKIN 作為接收的主時鐘,該時鐘為主模塊中的115 200×16 bps 的時鐘信號,RXD 為接收數據線,串口發送過來的數據通過該輸入口進行接收。在該模塊中定義了5 位狀態機,首先IDLE 狀態是空閑狀態,等待數據的到來,此時數據線為高電平,當數據線上傳來0 信號后,進入RevStartBit 狀態,在該狀態中,一直判斷信號線中的數據,如果在16 個脈沖內均為低電平,則認可該信號為數據幀起始信號,如果在此段時間中數據線出現高電平,則轉到IDLE 狀態,視為數據線上的毛刺。16個脈沖后,判定為起始信號后,進入RevDataBit 狀態,對數據線上的數據進行接收。數據位定為8 bit 的數據,每一bit 數據用16 個脈沖來接收,在第7 個脈沖讀取數據線上的數值,防止數據線上出現毛刺或抖動,接收到的數據存在RxDataBuf 寄存器中。接收完8 bit 數據后進入RevStopBit狀態,將RxReady 置為1,表示接收完成,傳遞到主程序,進行相應動作。16 個脈沖后進入RevDone 狀態,將接收到的數據從RxDataBuf 寄存器傳遞給RxData 寄存器,輸出到主模塊中。

圖2 RS-232 數據幀結構

3 HT7017通信接口模擬設計

HT7017 芯片是經典的單相電能計量芯片,該芯片通信接口為UART 即RS-232 接口,可以將電表通過的功率信號等信息存儲在芯片的內部寄存器中,用作電表的計量數據。該文利用FPGA 模擬該芯片的通信接口,以及芯片內部的寄存器。以此可以模擬和監控寫入該芯片的數據,防止出現篡改計量芯片數據的行為。

HT7017 芯片UART 通信有一確定的命令幀規范,首先發送0x6A 作為字節幀頭,然后發送 CMD 字節, CMD 字節最高位為0 則表示要進行讀操作,如果為1 則表示要進行寫操作,后面7 位數據表示要操作的數的寄存器地址。如果為讀操作,則將指定寄存器中的數據讀取出來,發送到數據線上,高位在前。發送數據一般為3 個字節的寄存器數據,如果數據不足3 字節,則將寄存器數據與數據幀的低位對齊,并將前面5 個字節的數據相加,拋棄進位,最后再按位取反,得到CHKSUM 字節,發送出去,用來校驗前面發送的數據的正確性。如果為寫操作,則將接收到的數據進行校驗和運算,與接收到的CHKSUM 字節對比驗證,如果相同則將數據存入寄存器中并返回一個ACK,數據為0x54,否則將數據丟棄,也返回ACK,數據為0x63。HT7017 芯片UART 通信的數據幀規范流程圖如圖3 所示。

在uart_r 模塊中,主要實現HT7017 接收數據的時序模擬仿真。首先利用FPGA 中配置的PLL 鎖相環IP 核,將板載主時鐘50M 分頻成1.8432 MHz 的時鐘信號,該頻率為通信波特率115 200 bps 的16 倍,用來接收數據線上的信息。之后定義6 位狀態機,以此來完成數據接收的時序設計。

IDLE 狀態為空閑狀態,此時數據線上一直為高電平,當檢測到數據線上有低電平時跳轉到start bit 狀態中,檢測該低電平,如果在16 個脈沖內均為低電平,則判定為起始信號,否則認定為數據線上的毛刺。之后轉入data bit 狀態,在該狀態接收8 bit 數據,第一個數據如果為0x6A,則繼續接收,否則放棄本次數據通信。接收第2 個字節后,判斷第一個bit,如果為1,則進行寫操作,如果為0 則進行讀操作。寫操作就繼續接收2 個字節的寄存器數據和1 個字節的校驗和數據,將校驗和數據前的數據相加,拋棄進位,再按位取反,與接收到的校驗和數據對比,如果相同則將數據存儲到在SDRAM中開辟的寄存器中,并返回0x54 表示接收完成。如果與校驗和數據不同,則放棄存儲數據,且返回0x63。如果要進行讀操作,則需要調用uart_x 模塊,且需要先利用gen_divd 模塊,分頻得到115 200 bps 的波特率,根據CMD 中給出的寄存器地址,取出其中的數據信息,如果不足3 個字節,則高位補0,并計算出校驗和字節,發送出去,作為發送數據的驗證。

圖3 HT7017 數據幀流程圖

4 仿真及結果驗證

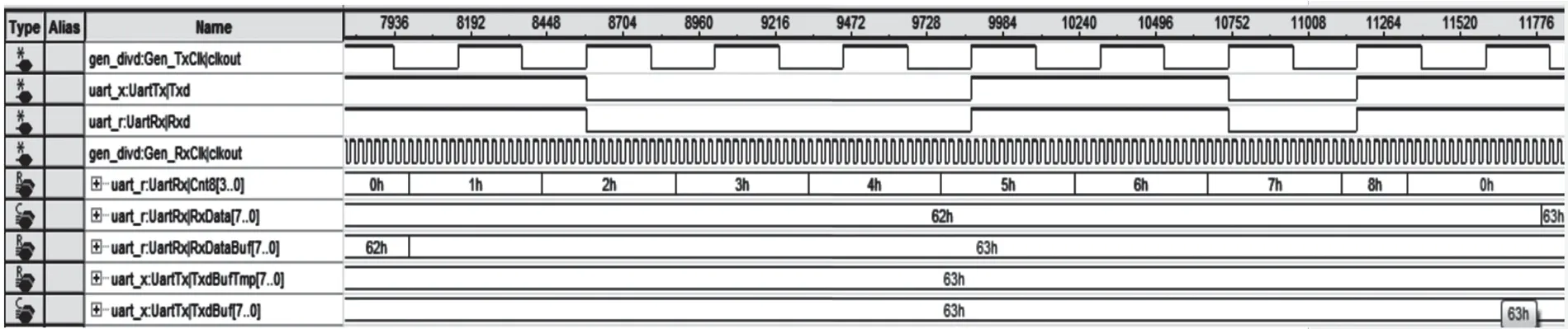

設計完串口的時序邏輯后,在QUARTUS中的SignalTab II 邏輯分析軟件中,進行了仿真驗證,結果如圖4 所示。該圖是通過使用串口調試助手軟件以115 200 bps 波特率發送十六進制數62 到FPGA 中,FPGA 上接收數據的波形,可以看出數據傳輸穩定且準確。

圖4 串口接收時序圖

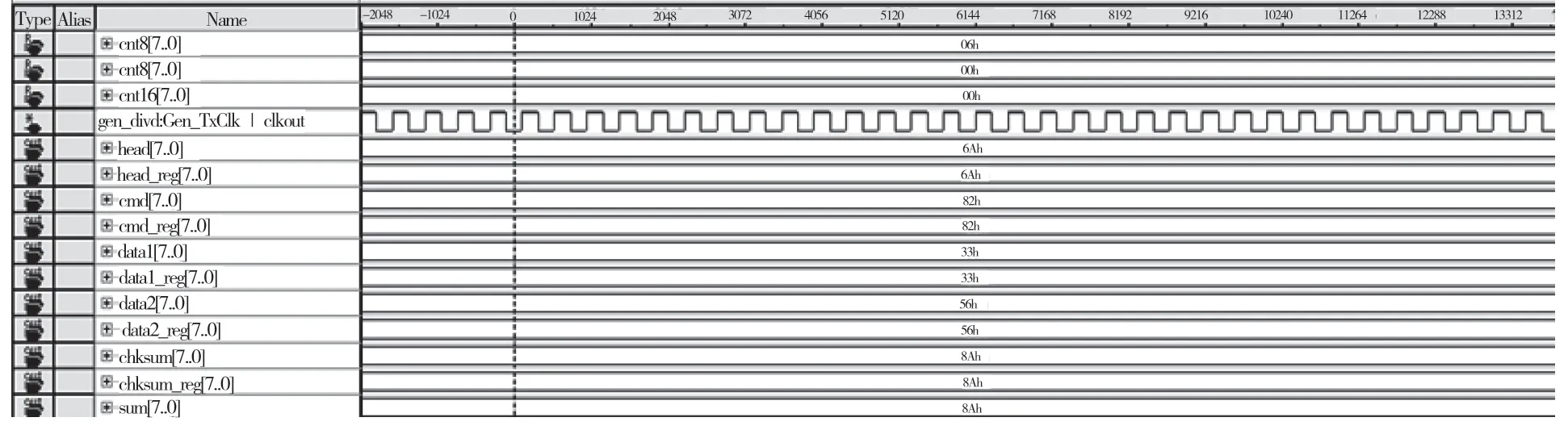

圖5 HT7017 寫入數據時序圖

HT7017 通信接口有其專門的數據幀規范,該文利用FPGA 模擬了其通信接口的設計,實現了數據的存取,滿足了項目的需要。圖5 為HT7017 芯片寫入數據的時序圖,首先接收到頭字節為0x6A,之后接收到CWD 字節為0x82,首位為1,表示有數據需要寫入,寫入的寄存器地址為0x02,之后接收到的數據為0x33 和0x56,計算其校驗和為0x8A,與接收的CHKSUM 一致,表明數據接收正確,可以存入相應寄存器中。數據接收過程明確,滿足要求。

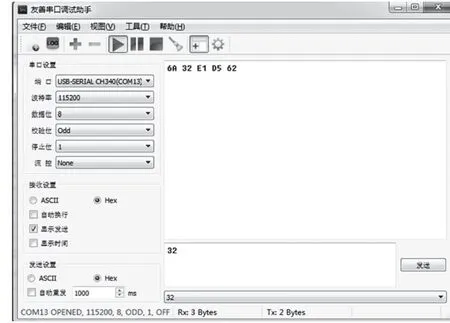

圖6 為模擬讀取HT7017 芯片中寄存器數據的時序圖,圖7 為串口調試助手中接收的數據截圖。首先利用串口調試助手發送頭字節0x6A,然后發送CWD 字節0x32,首位為0,表明要讀取數據,要讀取的寄存器地址為0x02,讀出的數據為0xE1,0xD5,0x62,仿真表明數據讀取準確。

圖6 讀取HT7017 數據時序圖

圖7 串口調試助手讀取數據圖

5 結語

該文提出的利用FPGA模擬RS-232串口通信的設計,運行穩定且配置簡單,可以廣泛應用于支持RS-232 接口的各類芯片的通信仿真,也可以解決某些開發板串口數量不足的問題。該文基于智能電表測試系統進行設計,利用FPGA 模擬支持RS-232 串口通信協議的存儲芯片,例如Flash 芯片、EEPROM 芯片等,可以用來監督通過該芯片收發的數據,并可以通過板載的ARM9 處理器將所得數據以Modbus 協議傳遞到上位機,進行顯示。也可以通過上位機直接修改該芯片內的數據,實現對智能電表的測試,防止出現篡改數據或偽造數據等行為,有較高的應用價值。