基于Multisim的RC積分型多諧振蕩器設計與仿真

王曉芳

(大連職業技術學院,遼寧大連 116037)

0 引言

隨著電子電路復雜程度的提高,在電子產品的設計過程當中,電子設計自動化技術(EDA)越來越得到廣泛的應用。該技術的應用可以有效的提高電子產品的設計效率,縮短設計周期,使得產品在市場競爭浪潮中快速占有一席之地。而Multisim 軟件是最常用的EDA 軟件之一,也是高職院校中數字電子技術教學中優秀的教學系統,適用于板級的模擬/數字電路板的設計工作,它包含了電路原理圖的圖形輸入、電路硬件描述語言輸入方式,具有豐富的仿真分析能力。

多諧振蕩器是一種自激振蕩電路,它沒有穩定狀態,只有兩個暫穩態,電路工作時不需要外加觸發信號,只要接通電源,在其相應的輸出端就會輸出矩形脈沖。數字電路設計中,一些要求不高的場合下的時鐘信號源大多會采用由門電路所構成的多諧振蕩器,其利用邏輯門電路的傳輸延遲時間,將奇數個與非門首尾相接,構成基本環形振蕩器。這種電路結構簡單,但由于門電路的傳輸延遲時間很短,這種振蕩器的振蕩頻率極高且不可調,所以實際用處不大。在基本環形振蕩器的基礎上增加RC 選頻網絡,構成RC 積分型多諧振蕩器,可以穩定的輸出1 Hz~1 MHz 的信號,而且具有頻率可調的優點。

1 RC 積分型多諧振蕩器電路結構

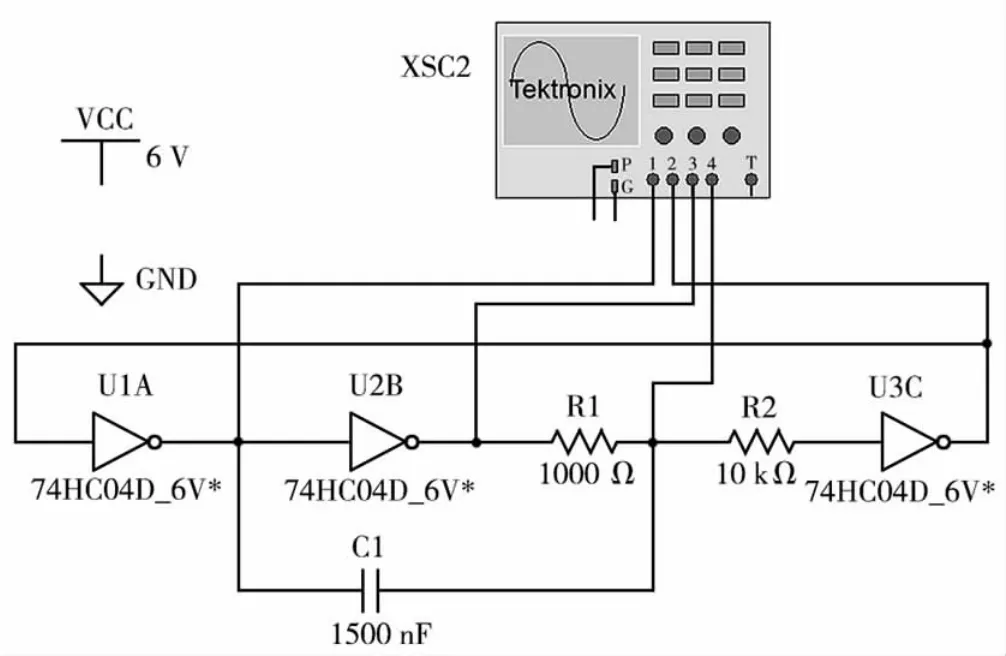

RC 積分型多諧振蕩器電路結構如圖1 所示。電路整體由3個非門和2 個電阻組成。其中R、C 為定時元件,決定多諧振蕩器的振蕩周期和頻率。在基本環形振蕩器的基礎上增加RC 環路,它不但增加環路的延遲時間,降低振蕩頻率,而且通過改變RC 的數值可以調節振蕩頻率。其中Rs 為限流電阻,約100 Ω。RC 積分型多諧振蕩器具有如下特點:①產生高、低電平的開關器件;②具有反饋網絡,將輸出電壓恰當的反饋給開關器件使之改變輸出狀態;③具有延遲環節,利用RC 電路的充、放電特性可以實現延時,以獲得所需要的振蕩頻率。

2 RC 積分型多諧振蕩器工作原理

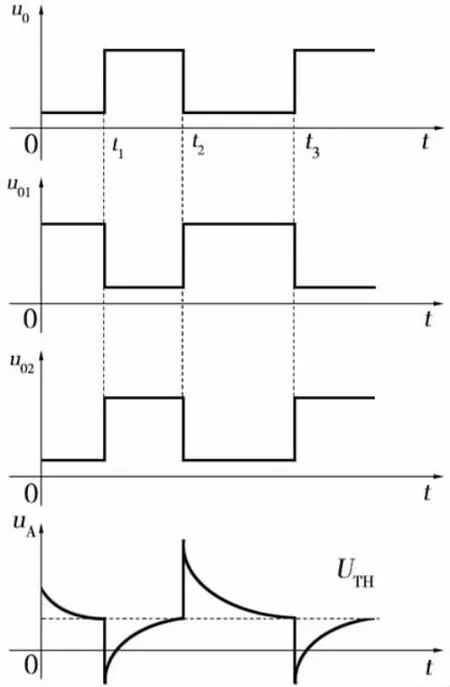

由于加入RC 環路,電路的振蕩周期大大增加,邏輯門電路的傳輸延遲時間同其相比可以忽略,于是各點波形如圖2 所示。

(1)第一暫態。設t1時刻A 點電位下降到門電路閾值電壓UTH,使輸出變為高電平uo=1,uo1=0,uo2=1,同時因為電容兩端壓降不能突變,使A 點電位產生負躍變,保證輸出uo為高電平,電路進入第一暫態。

圖1 RC 積分型多諧振蕩器電路

在此期間,uo2的高電平通過R 對C 充電,A 點電位不斷升高,在t2時刻A 點電位上升到閾值電壓UTH,電路的狀態又將發生變化。

(2)第二暫態。在t2時刻A 點電位上升到閾值電壓UTH,使輸出躍變為低電平uo=0,uo1=1,uo2=0,同時使A 點電位產生正躍變,保證輸出uo為低電平,電路進入第二暫態。

在此期間,電容通過電阻R 反方向充電,隨著反充電的進行,A 點電位逐漸降低,在t3時刻A 點電位下降到UTH,引起電路狀態變化,又翻回到第二暫態。

由于電容C 的充、放電在自動的進行,故在輸出端uo得到連續的方波,其頻率由電容的充、放電的時間常數決定。由于電容充、放電回路不完全相同,故充電時間常數與放點時間常數有所區別。如采用的是TTL 門電路,經過估算,振蕩周期約為式(1)。

圖2 RC 積分型多諧振蕩器工作原理

3 RC 積分型多諧振蕩器仿真分析

用Multisim12 軟件搭建如圖3 所示的RC 積分型多諧振蕩器電路。仿真時采用泰克型示波器觀測電路各點的輸出波形,按下仿真開關,示波器顯示各點的電平狀態,仿真結果如圖4 所示。由上至下依次是uo、uo1、uo2及uA的波形,仿真結果反映了RC積分型多諧振蕩器從第一暫態到第二暫態的工作過程,仿真結果與工作原理一致,證明該電路可以正常工作。

圖3 RC 積分型多諧振蕩器仿真電路

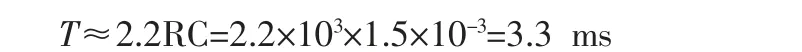

通過理論計算可得:

將游標指針1 位于方波信號一個周期的起始位置、游標指針2 位于方波信號一個周期的結束位置,可讀出tw=T2-T1=3.3 ms,與輸出脈沖周期的理論計算一致,驗證了該電路的有效性和可行性(圖4)。

4 結束語

通過對多諧振蕩器電路的深入研究,分析RC 積分型多諧振蕩器的電路結構及其工作原理,采用Multisim12 軟件建立仿真電路,并成功實施仿真分析。結果表明仿真得到的時序圖與理論基本一致,而且仿真得出的輸出波形周期與理論計算的信號周期一致,驗證了該電路設計方案的可行性和有效性。

圖4 RC 積分型多諧振蕩器仿真結果