基于FPGA的高清HD-SDI視頻采集系統設計與實現

錢宏文,劉會,付強,王毅

(中國電子科技集團公司第五十八研究所,江蘇 無錫 214072)

數字串行接口(Serial Digital Interface,SDI)是由美國電影與電視工程學會(the Society of Motion Picture and Television Engineers,SMPTE)制定的一系列由同軸電纜傳輸的非壓縮數字視頻接口標準[1]。目前,按照分辨率和傳輸速率的不同可分為標清SDSDI、高清HD-SDI以及3G-SDI 3種[2]。其中,HD-SDI接口遵循 SMPTE292標準制定,傳送YCrCb(4∶2∶2)串行數字分量,采用720 P或1 080 P的格式,因其具有分辨率高,動態范圍廣以及在白平衡、亮度、對比度等方面的優異性,是當前廣播電視行業高清成像及顯示設備的主要接口形式,應用范圍越來越廣。

與此同時,高分辨率意味著高的數據帶寬。因此,在采集HD-SDI高清視頻信號,要求采用具有更高傳輸速率的通信方式。傳統的USB2.0在實際應用中的最大傳輸速率僅為30~40 Mb/s,無法滿足HD-SDI 1.485 Gb/s的傳輸需求。常用的CameraLink[3]圖像采集接口雖然具有傳輸速度快和易于編程實現等優勢,但因其需要額外的PCIe等采集設備才能在臺式計算機上使用,因此存在通用性差,應用不便等缺陷。

USB3.0引入全雙工數據傳輸[4],5根線中有2根用來發送數據,有2根用來接收數據,也就是說USB3.0可以全速進行數據讀寫,因此較USB2.0性能上具有很大的提升,其理論最大傳輸帶寬在5.0 Gb/s(即640MB/s)[5],實際應用中可達1.7Gb/s(即220MB/s),完全滿足HD-SDI 1.485 Gbps的傳輸需求。除此之外,采用USB3.0,在通用筆記本上即可完成視頻數據的高速采集[6]。因此,基于USB3.0實現HD-SDI高清視頻信號采集,可集合USB2.0和CameraLink兩種接口的優點,具有應用方便、適用性廣等優勢。

1 系統總體設計

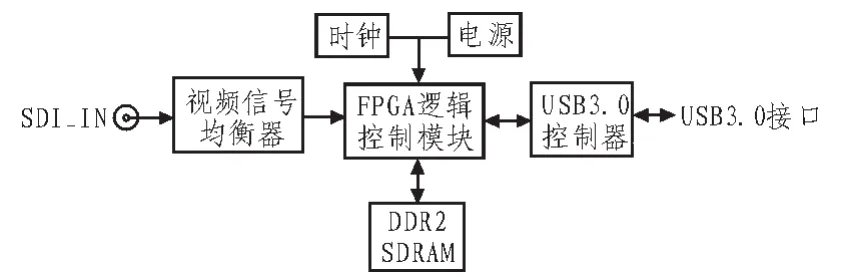

高清視頻采集系統(如圖1所示)主要由視頻信號均衡器、FPGA控制器、內部緩存DDR2 SDRAM、USB3.0接口以及時鐘和電源組成。

HD-SDI高清視頻信號由于速率比較高,經過同軸線纜長距離的傳輸會導致其高頻成分衰減過大[7],因此,需要增加均衡器來減少高頻信號的衰減,改善接收視頻信號的傳輸質量。采用TI公司的SDI均衡器,不但能夠自適應地調整高頻增益,而且還能實現由LVPECL電平轉化為LVDS標準電平,實現電平和阻抗匹配,從而能夠使FPGA獲得質量較高的SDI差分輸入信號。

圖1 采集系統設計框圖

FPGA選用Xilinx的Virtex-5器件,其配置的Rocket I/O GTP收發器,可編程實現100 Mb/s到3.75 Gb/s的傳輸速率,能夠滿足HD-SDI 1.485 Gb/s的接收要求。

DDR2 SDRAM選用鎂光(Micron)的128 M×16 bit器件,核心頻率和工作時鐘均為267 MHz,雙邊沿采樣,數據時鐘為534 MHz。因此,計算數據速率為:534 MHz(數據時鐘)×16(數據位寬)×2(DDR2數量)×80%(讀寫效率)=13 Gb/s;系統DDR2的速寫數據吞吐量為3.4 Gb/s,因此,該文采用的DDR2幀緩存方案可滿足HD-SDI系統傳輸帶寬需求。

USB3.0控制器選用CYPRESS的EZ-USB FX3,內部集成了512K的SRAM、ARM9內核以及豐富的IO接口(如GPIF、UART等),滿足文中方案的設計需求。

時鐘模塊主要為FPGA提供所需的參考時鐘,主要包括以下內容:

1)系統時鐘(時鐘頻率為100 MHz);

2)Rocket I/O GTP收發器的參考時鐘(時鐘頻率為148.5 MHz);

3)DDR2控制器IP核的輸入參考時鐘(時鐘頻率為 267 MHz)。

電源模塊為系統上所有子模塊供電。

2 FPGA程序設計

2.1 基于GTP的SDI接收模塊

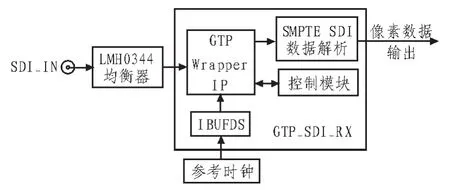

當前,利用FPGA接收SDI信號主流有兩種處理方案:一是利用解串芯片將從同軸電纜傳輸并均衡后的串行視頻信號轉為并行信號,然后將并行信號發送給FPGA進行處理;另一種是利用FPGA的高速收發器即將同軸電纜傳輸并均衡后的HD-SDI信號直接輸出到高速BANK的差分端,利用高速收發器進行解串。與前者相比,后者設計簡單、成本低、配置靈活且有成熟的高速IP(GTP_DUAL)支持,因此,采集系統選用第二種方案,模塊框圖如圖2所示。

圖2 GTP SDI接收模塊框圖

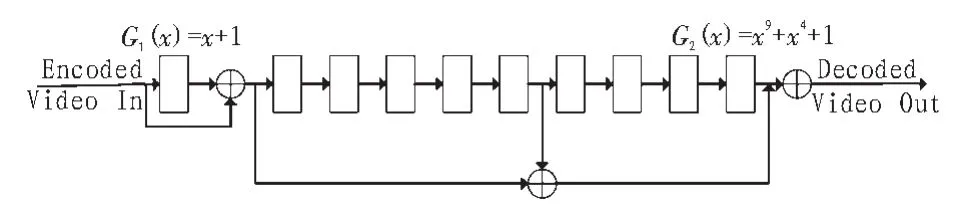

具體實現流程:首先GTP利用時鐘恢復電路(CDR)將輸入的HD-SDI信號的時鐘和數據恢復出來;然后對接收到的HD-SDI數據解碼,解碼流程如圖3所示包括將不歸零倒置碼(NRZI)轉為歸零倒置碼以及對NRZ解擾[8]。

圖3 HD-SDI信號解碼流程

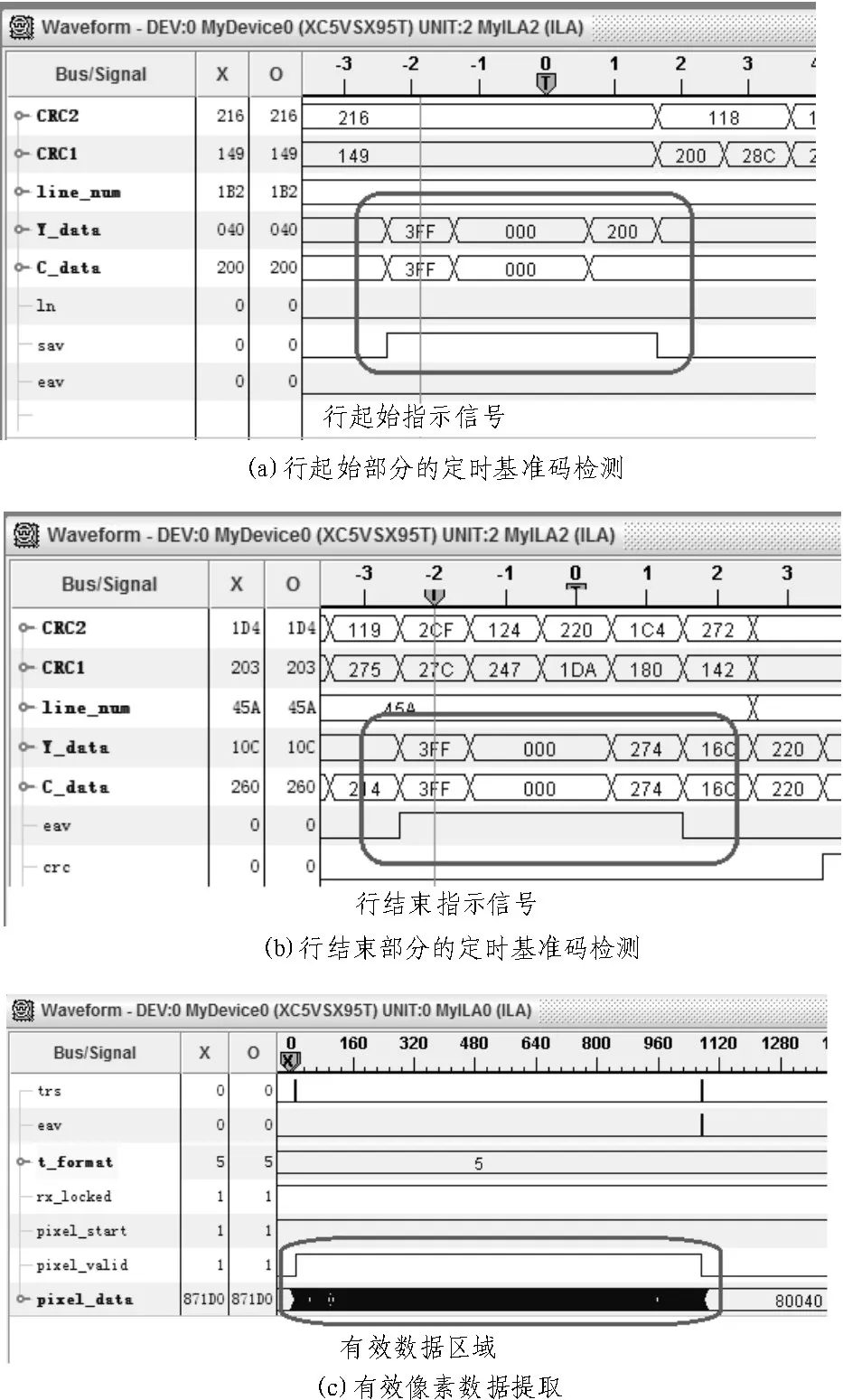

在調整圖像采樣后可輸出Y分量和C分量(Cr或Cb)。接著對兩個分量進行序列檢測,即提取分量中的定時基準碼(TRS)[9],如圖 4(a)、(b)所示。最后,利用提取的TRS判斷視頻格式、分辨率及幀頻以及數據的穩定性(在圖4中判斷mode_locked和rx_locke是否鎖定即是否為高,鎖定后可分別判斷模式是HD-SDI、SD-SDI還是3G-SDI以及傳輸的數據格式即分辨率和幀頻)。在穩定后,可從中提取有效的像素數據,如圖4(c)中橢圓區域標識所示。

圖4 HD-SDI信號接收時序

控制模塊的主要功能包括GTP收發器的主復位(包括GTP_DUAL內部的PLL復位)、發送器復位、接收器復位以及速率檢測。

2.2 DDR2幀存儲

系統中視頻流以逐行掃描1 080 P格式持續輸入,圖像的分辨率為1 920*1 080,幀頻是25 f/s,圖像像素時鐘是74.25 MHz,每幀圖像的包含2 640*1 125個像素時鐘,即行消隱720個像素,場消隱45個行周期,傳輸一幀視頻數據用時40 ms[10]。

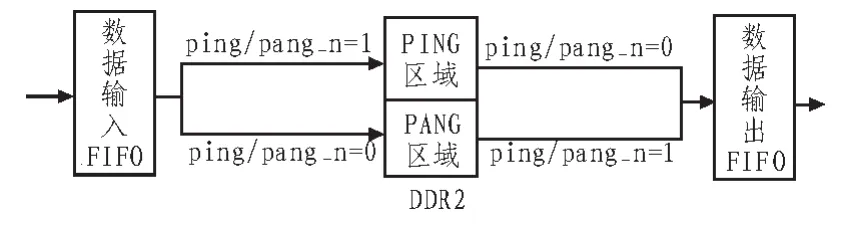

有效圖像數據提出后,經FIFO作跨時鐘域處理后,輸入至DDR2進行緩存后按要求的輸出格式經輸出FIFO讀出。在流水線處理的過程中,為防止讀寫沖突,采用乒乓處理,即對PING區域進行寫操作時,對PANG區域進行讀,反之亦然。DDR2幀存儲模塊框圖如圖5所示。

2.3 跨時鐘域處理

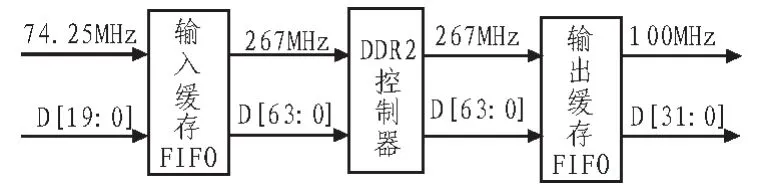

HD_SDI信號在經過解碼、緩存至USB接口輸出,共跨過3個時鐘域:

圖5 DDR2幀存儲模塊框圖

1)GTP經CDR模塊恢復出的時鐘,頻率為74.25 MHz,數據位寬為20位(Y分量與C分量各10位);

2)Xilinx IP核輸出的同步時鐘,頻率為267 MHz,數據位寬為64位(雙邊沿采樣,數據位寬為DDR2 SDRAM位寬的2倍);

3)USB3.0控制器的Slave FIFO輸入時鐘,頻率為100 MHz,數據位寬為Slave FIFO位寬即32位。

跨時鐘域處理如圖6所示。

圖6 跨時鐘域處理

為解決以上3個時鐘域不同步給系統所帶來的亞穩態問題,該文利用異步FIFO,通過空滿、近空近滿等標志信號控制讀寫速率[11],實現不同速率不同位寬接口的無縫連接。

2.4 USB3.0接口控制模塊

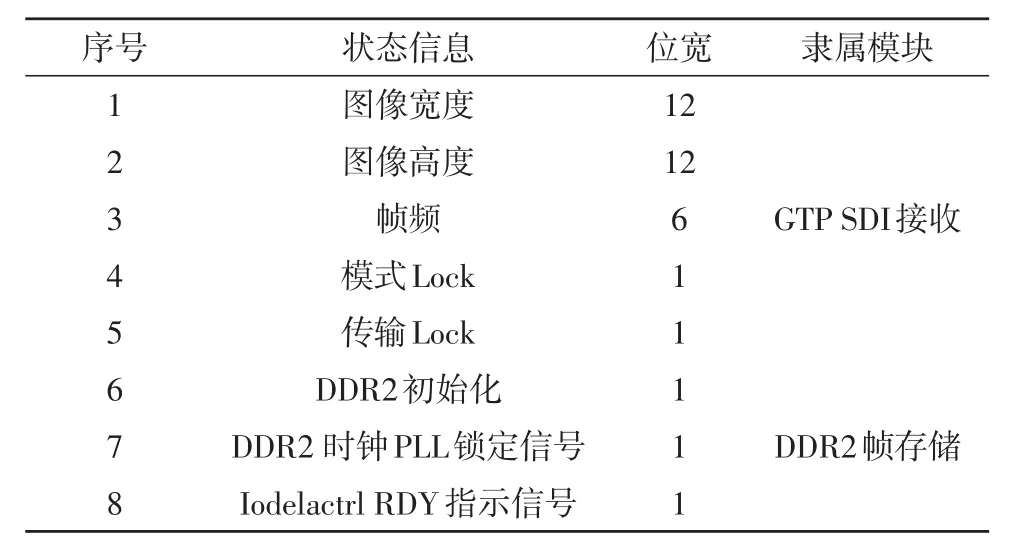

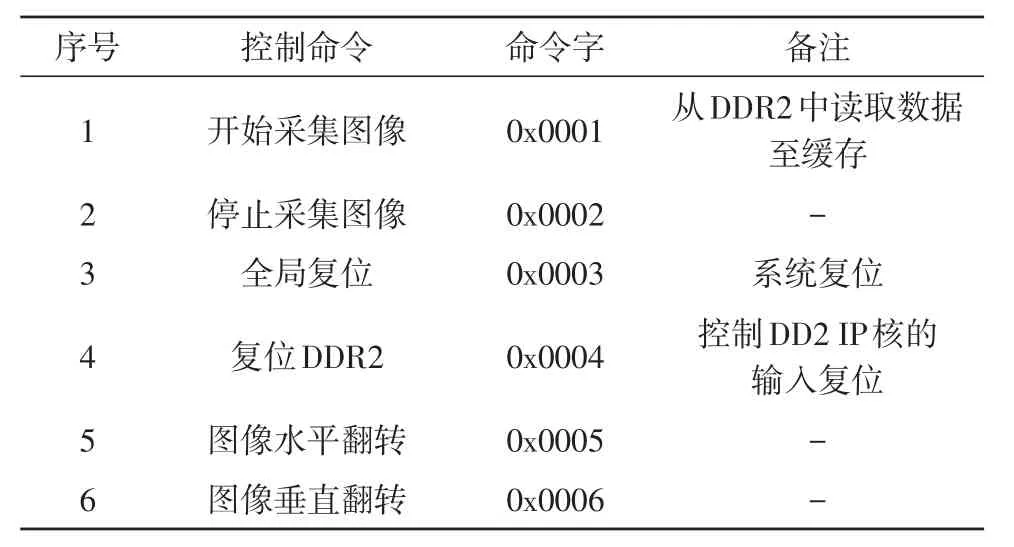

USB3.0控制接口模塊通過控制FX3與FPGA的GPIF II接口,實現FPGA與FX3之間的數據交互。在該方案中,FPGA每秒定時將1 920×1 080的25幀HD-SDI圖像數據以及信號的連接狀態和各個模塊的工作狀態(系統監測信號如表1所示)[12]上傳給FX3,同時FX3將上位機控制指令(如表2所示)下發給FPGA以同步和控制各個模塊的運行。

表1 狀態監控

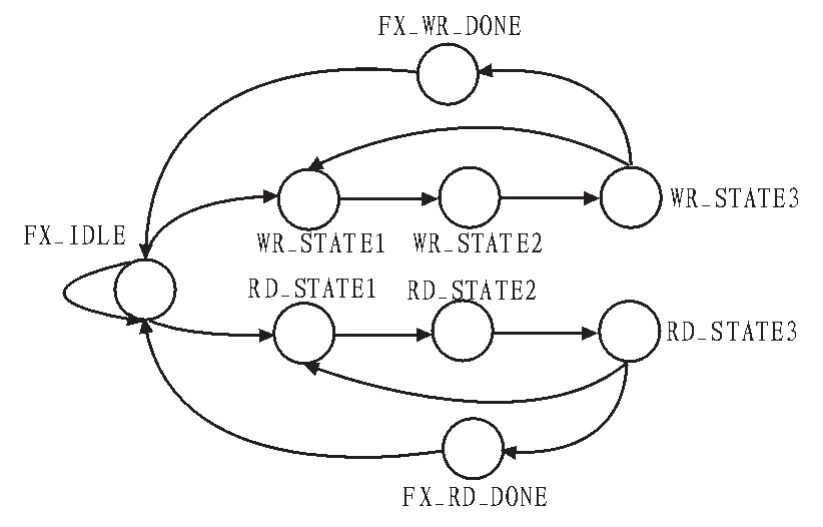

如圖7所示,為USB3.0控制模塊的狀態轉移圖[13]。系統上電復位,狀態機處于空閑態(FX_IDLE),當檢測到圖7中輸出緩存FIFO不空時,狀態切換至WR_STATE1,開始向Slave FIFO中寫入數據,寫狀態定義如下。

表2 控制指令

WR_STATE1:寫入指定的FIFO地址;

WR_STATE2:將寫命令使能(低有效);

WR_STATE3:把寫入的數據送到數據總線;

在完成1次寫操作后即在WR_STATE3狀態時判斷數據是否寫完(即輸出FIFO是否為空),未寫完則進行下一次寫操作(即WR_STATE1狀態),寫完則跳轉至FX_WR_DONE狀態,最后回到FX_IDLE狀態。

當檢測到Slave FIFO的讀狀態為高即不空時,狀態機由FX_IDLE切換至RD_STATE1,開始從Slave FIFO中讀取數據。讀狀態定義如下:

RD_STATE1:寫入需要讀取的FIFO地址;

RD_STATE2:數據輸出使能(低有效);

RD_STATE3:將讀指令使能(低有效)。

在完成1次讀操作后即在RD_STATE3狀態時判斷數據Slave FIFO的讀狀態是否有效,有效則進行下一次讀操作(即RD_STATE1狀態),無效則跳轉至FX_RD_DONE狀態,最后回到FX_IDLE狀態。

USB3.0接口控制狀態機如圖7所示。

3 USB3.0控制器

3.1 固件程序設計

在固件程序設計中,為縮短設計開發周期,該系統使用CYPRESS提供的SDK開發包[14]。

固件的設計分為兩部分,一部分是利用GPIF II Designer工具完成GPIF II接口設計,編譯生成與接口配置相關的C頭文件;另一部分是把頭文件添加到固件工程中,使用Eclipse編譯,利用SDK開發包中的API接口調用固件程序[15]。

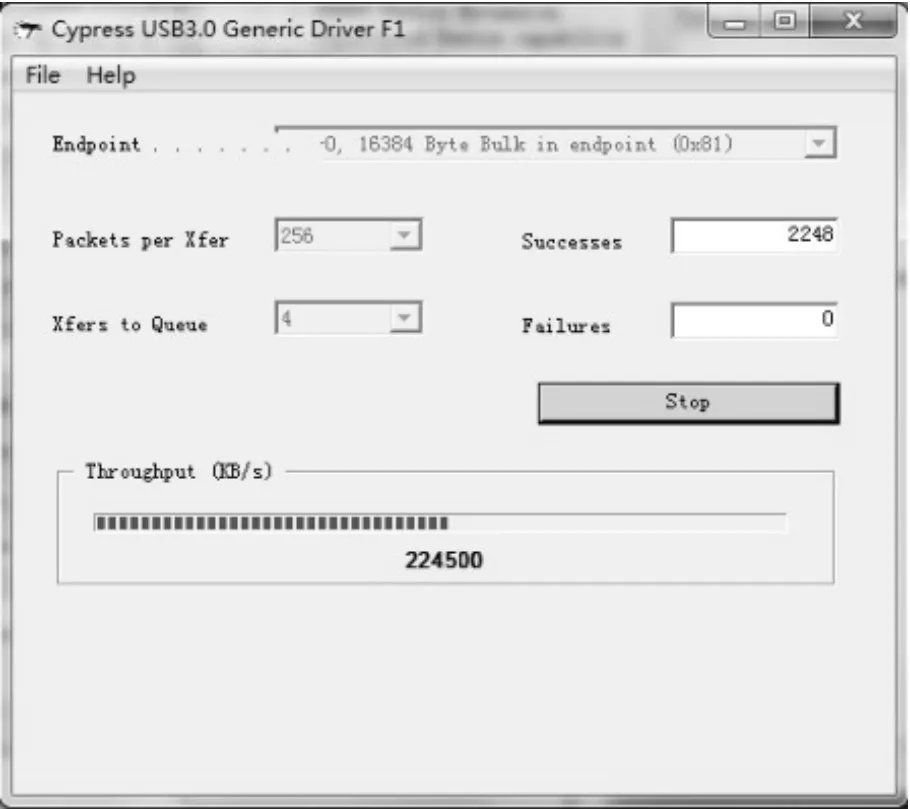

3.2 接口速率測試

利用CYPRESS的Streamer軟件對USB3.0接口進行最大速度測試。內部產生0~255的循環測試數據,向輸出緩存FIFO寫入,并將數據讀出發送給Slave FIFO[16]。

圖7 USB3.0接口控制狀態機

如圖8所示,該系統USB3.0的數據最大讀取速率可達到224.5 MB/s,能夠滿足HD-SDI高清圖像采集系統的傳輸速率要求。

圖8 USB3.0數據速率測試結果

4 結束語

文中利用FPGA和USB3.0控制器實現了高清HD-SDI視頻信號的采集及高速傳輸。充分利用FPGA內部的Rocket IO資源,既提升系統性能又降低了硬件成本,具有使用方便、適用性廣等優勢。除此之外,系統性能留有較大余量,FPGA軟件調整后,可靈活兼容HD-SDI及3G-SDI接口標準[17],為其他種類SDI接口的應用拓展提供了參考和指導,具有實際應用價值。